- 全部

- 默认排序

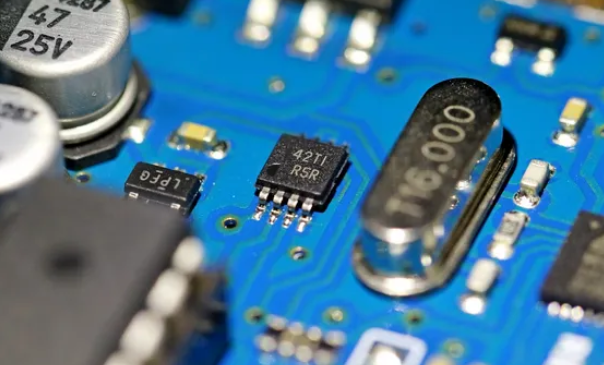

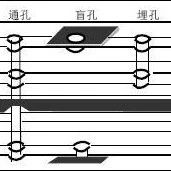

在高速PCB设计中,过孔作为连接不同层的关键元素,其阻抗特性对电子工程师来说很重要。良好的过孔设计,可加强信号完整性,提高系统性能,然而我们总会遇见各种问题,其中之一是:同一个过孔可能会有不同的阻抗,这是为什么?1、孔径与焊盘大小过孔的孔径

在PCB设计中,许多电子工程师会选择通过环形地的设置,来提高电路板的电磁兼容性和静电放电防护,尤其是这个方法特别适合对噪声敏感货对信号完整性有高要求的电路,那么不同形状的PCB板,其环形地该如何设置?1、矩形或方形PCB板①规划环形地路径沿

在集成电路(IC)设计即将流片的关键阶段,走线布局成为决定芯片性能、功耗及可靠性的重要因素,合理的走线策略不仅能优化信号完整性,也能有效减少噪声干扰,确保芯片功能的正确实现。1、控制连线长度与增强驱动金属连线应尽量短以减少延迟和信号衰减;长

在差分信号传输系统中,信道均衡是一种关键技术,直接针对信号在复杂信道中传播时遭遇的衰减与畸变进行精确校正,以确保信号的完整性和准确性,差分信号以其对共模噪声的抑制能力和较高的信号完整性,广泛应用于高速数据传输领域。但是,即便是在差分信号系统

十层板在电路设计中因其优异的信号完整性而备受青睐,但其复杂的布线结构和层间关系也带来了电磁干扰(EMI)的问题。如果不能处理,实在是很麻烦,所以在你设计十层板的EMI解决方案,不如参考这些方法!1、信号与回路层相邻布局严格按照信号、地、信号

Keysight 是德科技的 PathWave Electrical Performance Scan (EP-Scan)是一款可独立运行的 EM 电磁信号仿真软件,仿真结果包括信号完整性度量方面的信息,如通道回波损耗、插入损耗和阻抗时域反射计(TDR)。EP-Scan 可以自动化进行不同设计版本之

在电子系统设计中,如果一个电路是由多个PCB组成,那么它们是否需要共地?今天针对这个问题进行解释,希望对小伙伴们有所帮助。1、大多数情况下需要共地多个PCB组成的电路,为了保持信号的完整性和系统的稳定性,通常需要共地。共地可以减少地电位差,

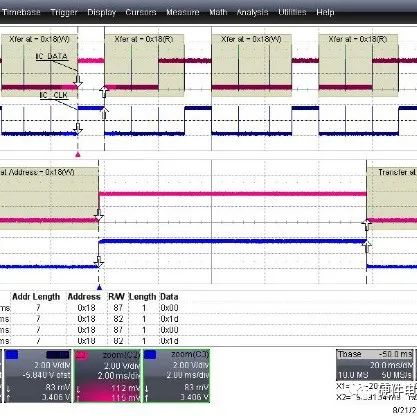

IIC接口—规范硬件信号测试1.测试指标说明 IIC总线根据时钟速率的不同分标准模式、快速模式和高速模式三种,测试中需根据实测的结果选择相应的测试指标作为判断的依据。测试内容主要包括以下两个方面: 信号完整性:SCL、SDA; 信号时序:tHD;STA、tSU;STO、tSU;D

【摘要】本文结合某单板(下文中统一称M单板)FPGA调试过程中发现地弹噪声造成某重要时钟信号劣化从而导致单板业务丢包的故障,来谈下如何最大程度地降低地弹噪声对单板信号完整性影响。一、故障现象M单板在进行业务调试时发现:如果只有上行方向有业务,上行业务正常无丢包;如果只有下行方向有业务,下行业务也正常

PCB过孔分析

【摘要】 在PCB设计过程中,PCB过孔设计是经常用到的一种方式,同时也是一个重要因素,但是过孔设计势必会对信号完整性产生一定的影响,尤其是对高速PCB设计。本文在参阅一些相关资料,及在设计过程中的心得,对过孔进行了一些简单的分析,希望能作为硬件设计人员的参考。一、问题的提出PCB过孔是P

扫码关注

扫码关注