- 全部

- 默认排序

在电子工程中,阻抗控制的设定值经常是10%,虽然大家都说这是基于一系列工程和技术上的考量,但也有很多人好奇,为什么阻抗控制不能是其他数值,必须是10%?首先,这就必须要了解阻抗控制的重要性。阻抗控制的目的是确保信号在传输过程中的稳定性和效率

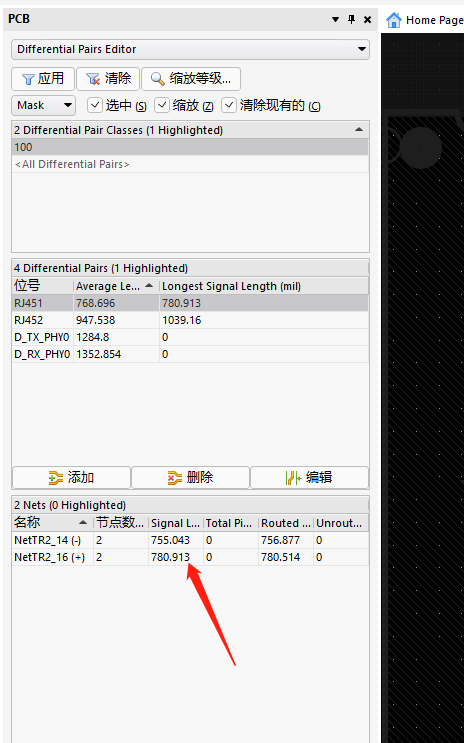

地分割间距要保证2mm,有器件的地方可以不满足2.网口除差分信号外,其他的都需要加粗到20mil3.晶振需要包地处理,并在地线上4.BGA里面的铜皮建议挖空处理5.焊盘到孔的间距过近,建议6mil,后期自己优化一下以上评审报告来源于凡亿教育

在印刷电路板(PCB)设计中,50Ω阻抗值经常被提及,无论是在高速数字信号传输还是射频(RF)电路中,大家好像默认阻抗值都是50Ω,这是为什么?1、历史标准及广泛应用50Ω阻抗值起源于早期的通信和广播电视行业,作为一种广泛接受的标准,它逐渐

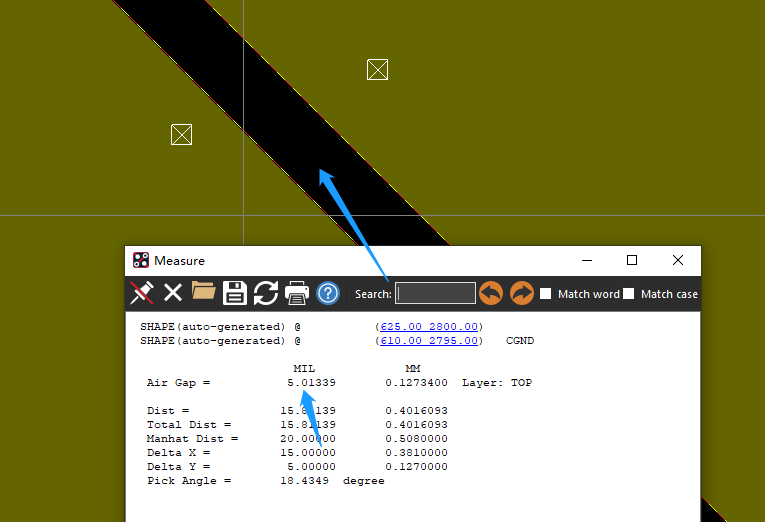

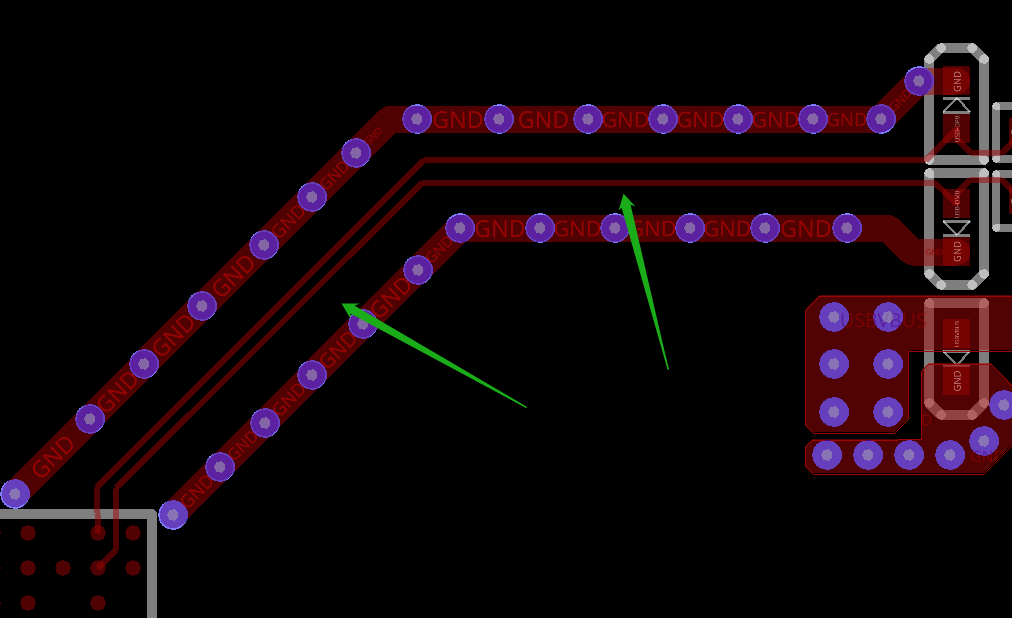

网口差分需要进行对内等长,误差5mil2.走线需要优化一下,尽量不要出现直角3.差分出线要尽量耦合4.差分焊盘出线尽量从四角出线,后期自己优化一下5.差分需要按照阻抗线宽线距走线,避免后期造成阻抗突变6.存在多处drc7.时钟信号包地,尽量

注意优先布局静电器件 再去布局其他器件,优先级最高:注意差分从焊盘拉出也是需要保持耦合的:不要存在直角以及尖角:CC1 CC2信号需要加粗走线:差分打孔换层需要两侧打上地过孔:差分对内等长GAP需要大于等于3W:差分对内等长误差为5MIL:

注意焊盘出线规范后期自己优化一下2.差分对内等长凸起高度不能超过线距的两倍3.注意差分走线要尽量耦合4.一层连接不用打孔,注意不要出现STUB线头5.CC1和CC2属于重要信号,走线需要加粗6.注意差分信号包地要在地线上打上地过孔7.过孔需

随着电子技术的不断发展,芯片生产工艺迭代更新,印制电路板(PCB)结构日益复杂,从最早的单片机到双面板,再到复杂的多层板结构,电路板上的布线密度越来越高。同时,随着DSP、ARM、FPGA、DDR等高速逻辑元件的应用,PCB的信号完整性和抗

随着万物互联时代的发展,5G网络、AI大模型的崛起,信号频率日益增高,产品逐渐高密度化。面对高速高密度的PCB设计挑战,仿真工程师需要改变的不仅仅是工具,还有设计方法、理念及流程。光靠在大学期间所学到的仿真工具及电路原理,动手做过信号仿真项

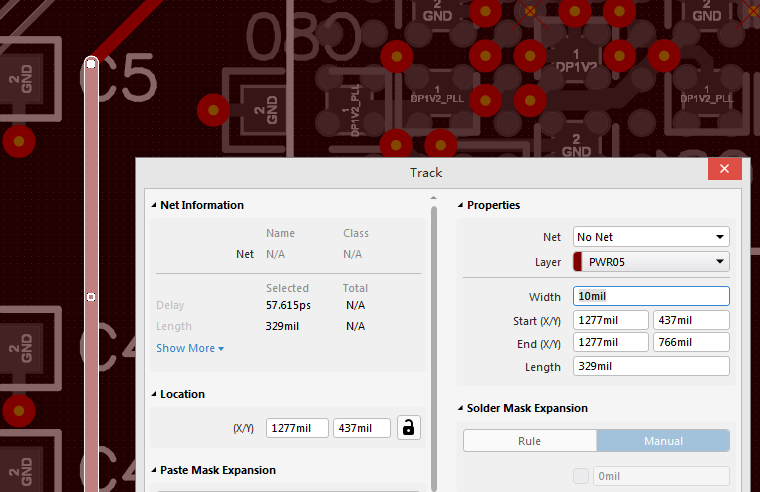

建议平面层的分割带宽度至少20MIL:地址信号类的等长还存在个别信号的误差报错:误差报错的信号自己再去等长优化。建议地址跟数据线两个类之间的信号可以走一根GND信号线进行分割开:或者自己预留20MIL的宽度。整个电源平面的信号都是3.3V信

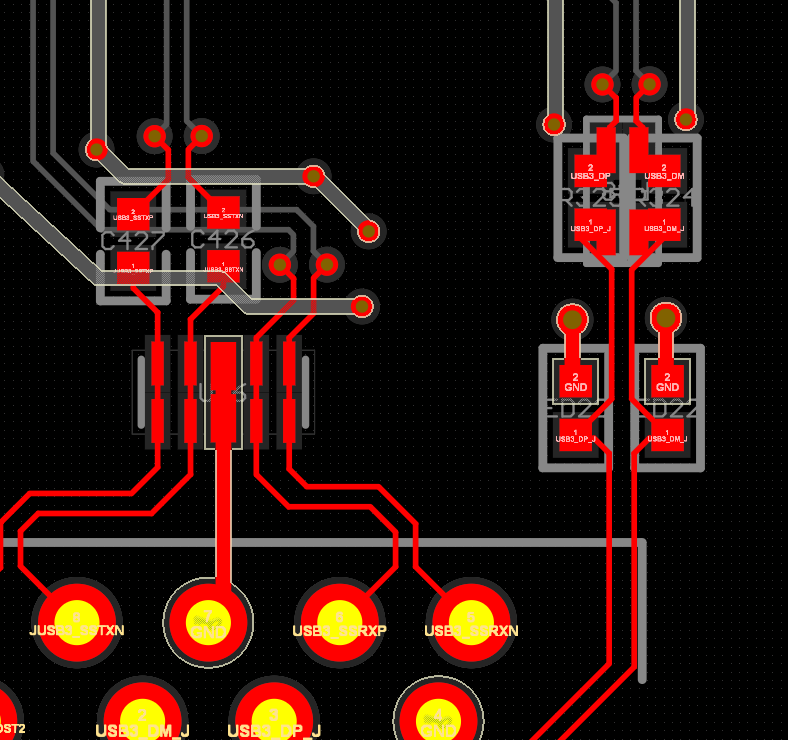

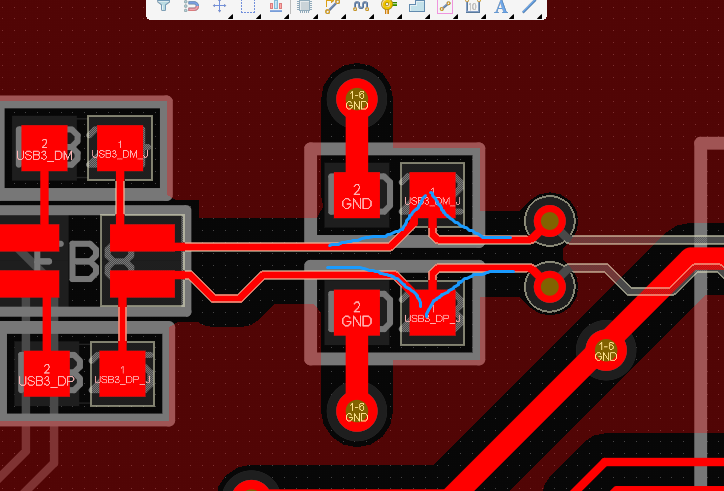

USB2.0:差分走线是需要保持耦合,需要修改,不合格:USB3.0:还有一块铜皮存在板外,自己删除下:此处器件注意整体中心对齐放置:差分信号打孔换层的过孔两侧打上地过孔:此处差分需要优化,要耦合走线 :注意此处焊盘出线,需要从两侧边拉线出

扫码关注

扫码关注