- 全部

- 默认排序

DDR采用菊花链拓扑结构时,由于信号传输线较长通常需要在DDR末端加上终端匹配电阻,端接的方式有很多,但是都是为了解决信号的反射问题,通常为了消除信号的反射可以在信号的源端或者终端进行解决,在源端处消除反射是采用电阻串联的方式,在终端处消除

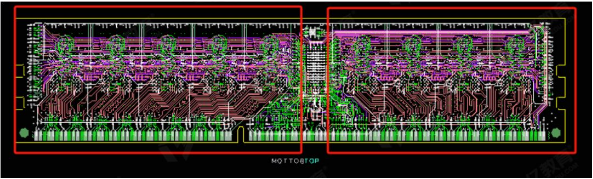

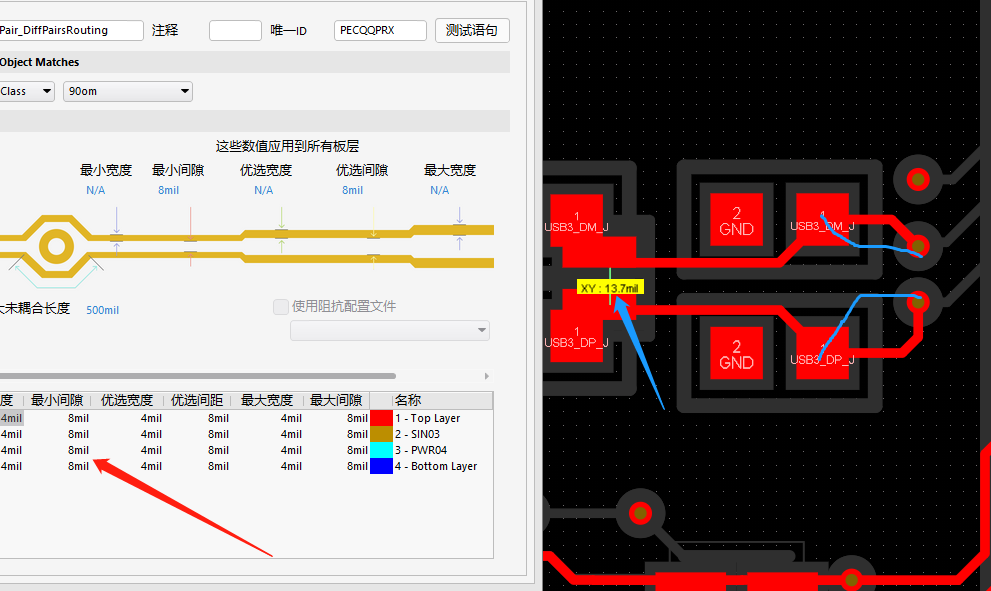

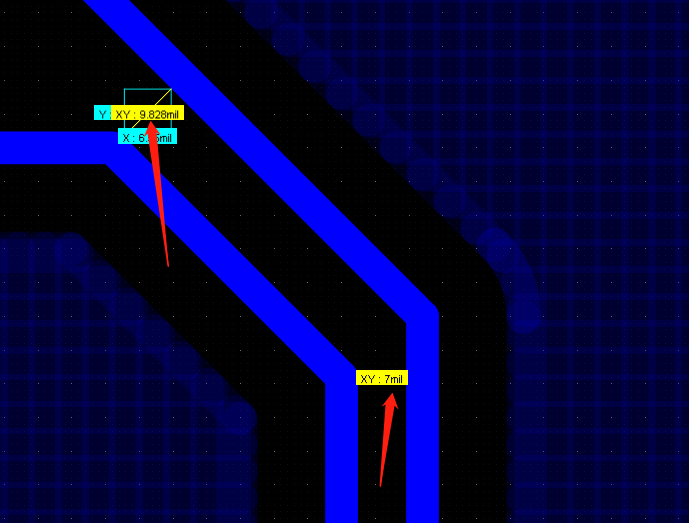

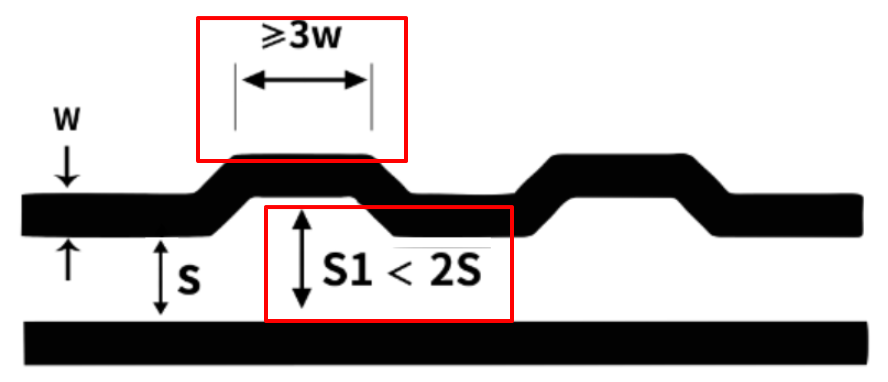

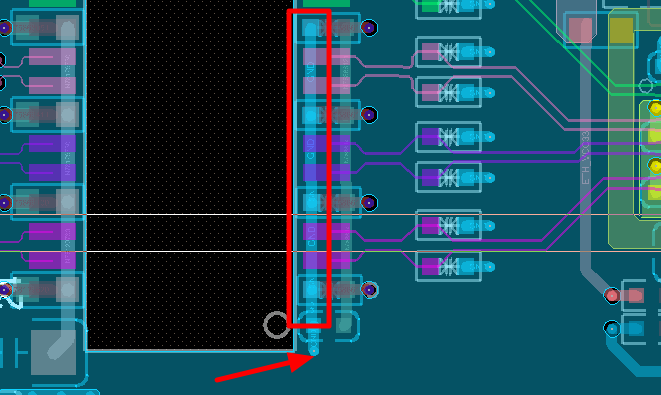

差分走线要按照阻抗间距走,差分出线要尽量耦合,后期自己优化一下有好几处差分没有按照阻抗线距走,后期自己调整一下2.差分对内等长凸起高度不能超过线距的两倍3.CC1和CC2属于重要信号,走线需要加粗4.走线需要优化一下,尽量不要有直角5.差分

差分需要按照阻抗线距走,后期埃及调整一下2.差分对内等长凸起高度不能超过线距的两倍网口座子需要靠近板框摆放3.差分出线要尽量耦合,走线需要优化一下4.时钟信号包地需要在地线上打孔,建议50mil-100mil一个以上评审报告来源于凡亿教育9

差分对内等长绕线不符合规范差分对布线线宽不一致,会导致阻抗不一致多个器件没有布局布线内层电源和地没有铜皮,导致电源和地都是开路变压器前后电源线宽不一致,变压器除差分外所有走线加粗到20mil时钟信号没有布线,应包地打孔连接rx,tx应建立等

地网络焊盘就近打孔接地晶振应走类差分形式包地打孔处理重要信号线尽量少换层,最多打三次孔以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com

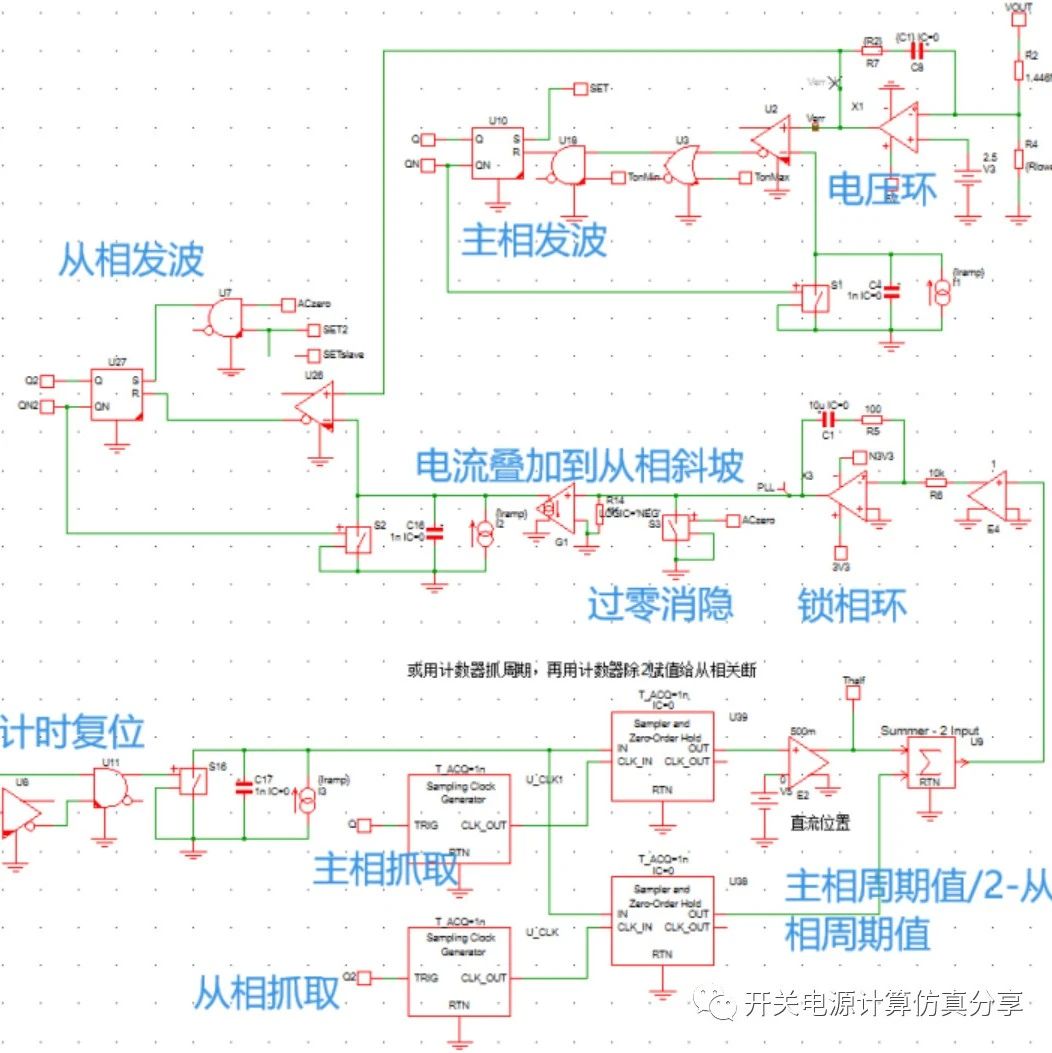

上一期通过单相CRM BOOST PFC仿真已经把主功率电路、环路控制ON TIME、过零检测、起振信号验证完成,接下来就是加入交错电路,实现两相变频交错。 第一步是先把单相临界模式PFC直接改为两相并联,共用驱动,保证功率电路能正常工作,并将环路参数调好,调试方法请参考交错CRM B

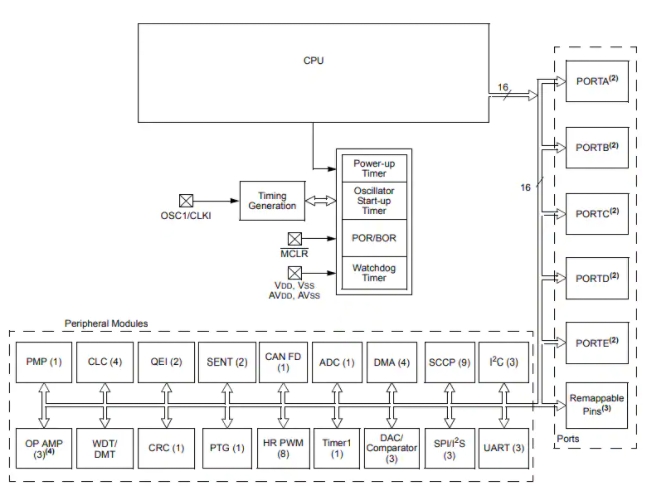

一、产品详情:dsPIC33CK 16位数字信号控制器 (DSC) 设计用于将MCU的控制属性与DSP的计算能力集成在单一内核中。这些dsPIC33CK DSC具有16位CPU、高分辨率PWM、CAN灵活数据 (CAN FD)、内部振荡器、

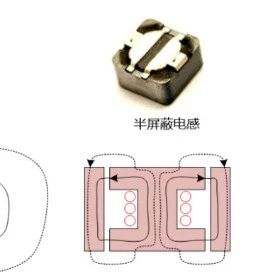

电感下方到底要不要铺铜?

PCB设计,电感下面怎么处理?针对不同类的产品,处理的方式也有所不同,一直以来,都是有不同看法的。电感通过交变电流,电感底部铺铜会在地平面上产生涡流,涡流效应会影响功率电感的电感量,涡流也会增加系统的损耗,同时交变电流产生的噪声会增加地平面的噪声,会影响其他信号的稳定性。在EMC方面来看,在电感底部

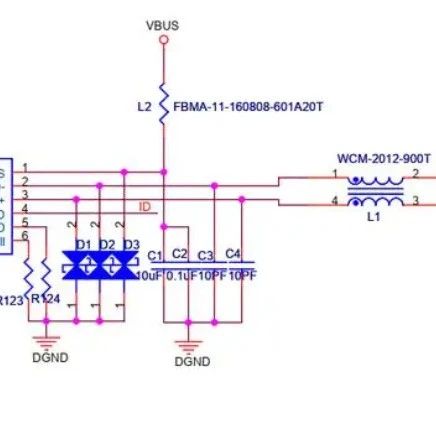

USB接口的EMC设计

在提到干扰对USB的影响时,差分数据传输与简单的同轴电缆相比具有很大的优势。在感性干扰效应(磁场)情况下,导线的绞合可以弥补干扰效应。●USB控制器的输入/输出不是完全对称的,因此USB信号显示出共模干扰。●Layout与HF/EMC不兼容,寄生电容和缺少波阻匹配会产生共模干扰。●电路设计(USB滤

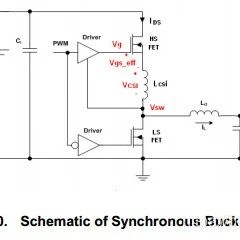

MOS管及其外围电路设计

01栅极驱动部分常用的mos管驱动电路结构如图1所示,驱动信号经过图腾柱放大后,经过一个驱动电阻Rg给mos管驱动。其中Lk是驱动回路的感抗,一般包含mos管引脚的感抗,PCB走线的感抗等。在现在很多的应用中,用于放大驱动信号的图腾柱本身也是封装在专门的驱动芯片中。本文要回答的问题就是对于一个确定的

扫码关注

扫码关注