- 全部

- 默认排序

1、R7FA6M3AF3CFB带有 USB 高速、以太网和 TFT 控制器的 120MHz 32位微控制器RA6M3 微控制器 (MCU) 群组使用高性能 Arm® Cortex®-M4 内核,提供具备 2D 加速器和 JPEG 解码器的

以太网硬件电路设计

点击上方名片关注了解更多实现以太网通信硬件电路方法很多,一般情况是CPU MAC PHY 网络变压器 RJ45。整个硬件电路最多用5个电子器件完成。随着集成电路的发展,很多功能被集成在一起,简化硬件电路的设计。上述那种方法,器件较多,开发难度比较大。下面列举其它3种方法。1、CPU(集成MAC层),

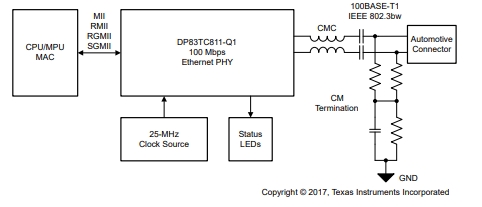

1、器件说明DP83TC811-Q1 器件是一款符合 IEEE 802.3bw 标准的汽车类 PHYTER™ 以太网物理层收发器。它提供通过单一屏蔽双绞线电缆发送和接收数据所需的所有物理层功能。该器件具有 xMII 灵活性,支持标准 MII

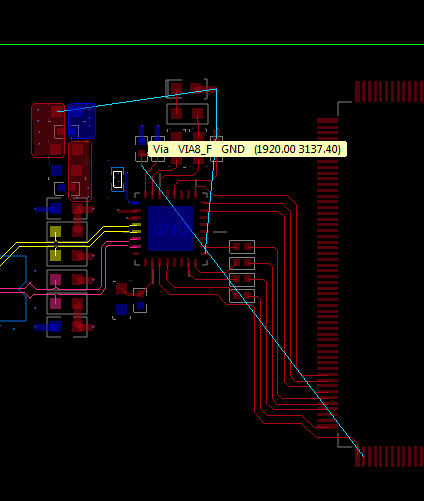

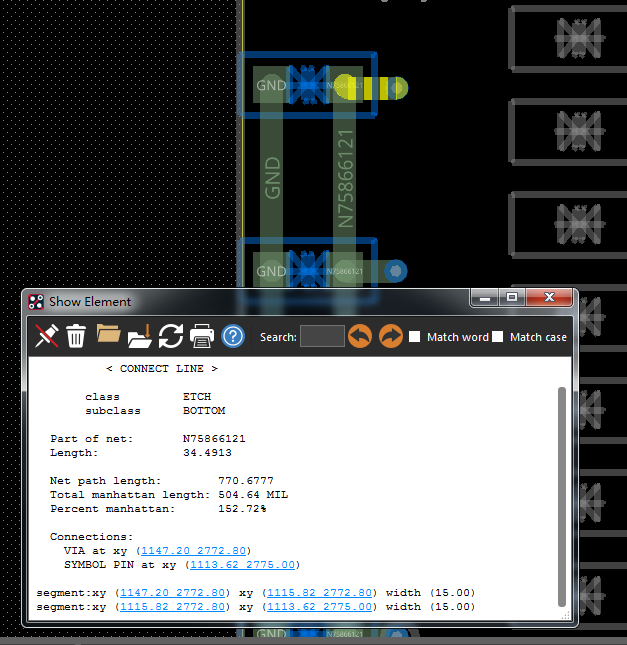

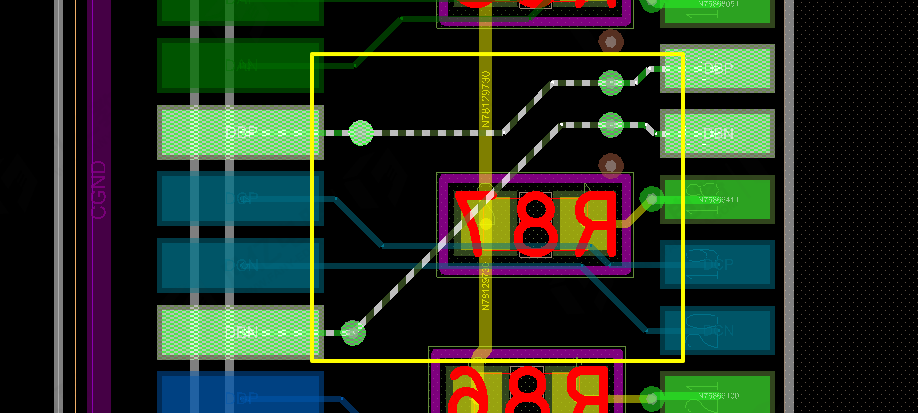

还存在飞线,注意电源信号处理:差分打孔换层的过孔两边注意添加地过孔,缩短回流路径:注意差分对内等长误差为5MIL:差分组跟组不用等长,组内等长就可以了:单端信号的TX RX需要组内等长,没有设置:自己后期去设置下组内等长,在拉等长。以上评审

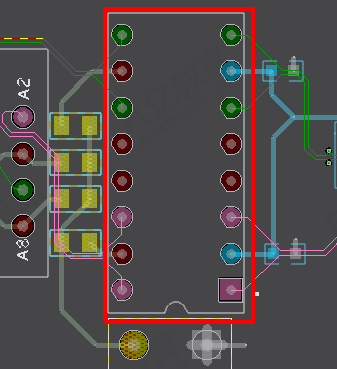

变压器上除了差分信号,其他的加粗20MIL走线:晶振尽量包地处理:RX TX以及差分组内等长没啥问题:建议机壳地与电路地之间分割2MM间距:其他的没什么问题。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可

差分走线尽量耦合差分应建立对内等长规则控制对内等长5mil误差范围变压器除差分对以外所有走线加粗到15mil以上晶振布线应走类差分形式芯片主电源输入走线应加粗过孔到焊盘应保持一定间距,不要靠的太近以太网芯片到CPU的RX、TX信号线要分别建

1、VSC7435XMT6端口电信级以太网交换机,带2个Cu PHY324BGA说明VSC7435 Serval-TE交换机以IP边缘分界和接入设备为目标,提供企业和移动回程。VSC7435基于虚拟服务感知架构(VISAA),这是一种硅实现

变压器下方所有层挖空铺铜差分换层打孔旁边要打回流地过孔差分对内等长绕线错误差分对内等长误差控制5mil范围内以太网转换芯片到CPU的tx、rx网络走线分别建立等长组,控100mil误差范围分别等长。电源输入接到第一个电容前方,在从最后一个电

在设计PCB时,经常会遇到高速差分线,比如USB、HDMI、LVDS、以太网等等,高速差分线不仅要求信号线的正端和负端信号线宽及线间距保持一致,还需要对差分信号线进行阻抗控制。控制差分信号线的阻抗,对高速数字信号的完整性是非常重要的,因为差分阻抗影响差分信号的眼图、信号带宽、信号抖动和信号线上的干扰

1、BCM87800A0KEFBG 7nm CMOS 800GbE (8:8) PAM-4 PHY 以太网收发器BCM87800是业界性能最高、功耗最低的单芯片800GbE PAM-4 PHY收发器,能够以53 Gbaud驱动八通道106

扫码关注

扫码关注