- 全部

- 默认排序

FPGA在逻辑芯片项目工程中是常见的,很多FPGA在项目中基本上都是以HDL代码来设计逻辑电路,但很多小白编写的HDL代码基本上都是不符合需求,费时费力,所以如何快速判断HDL代码是可行的?任何符合HDL语法标准的代码都是对硬件行为的一种描

我国虽然在5G上、物联网上、航天航空上等多种领域处于国际先进水平,但不可否认的是我们也在多种领域落后于海外国家,如先进芯片、EDA软件、芯片制造等,其中就有科学计算软件,我国的科学计算软件基本上是靠海外进口,没有完全自主的国产软件。科学计算

对程序进行优化,通常是指优化程序代码或程序执行速度。优化代码和优化速度实际上是一个予盾的统一。一般是优化了代码的尺寸,就会带来执行时间的增加;如果优化了程序的执行速度,通常会带来代码增加的副作用。很难鱼与熊掌兼得,只能在设计时掌握一个平衡点

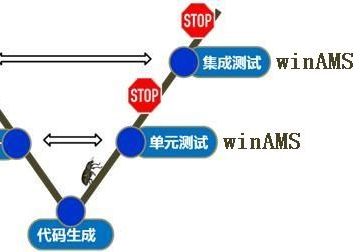

CoverageMaster winAMS : 适用于嵌入式目标机代码的单元测试/集成测试工具全面支持嵌入式微机!验证嵌入式C/C++软件 实施以模块为单位的自动化单元测试工具 不需要HookCode 直接使用目标机代码进行单元测试 联合静

在底层代码编写中,初始的框架设计总会面临选择,针对实际的硬件使用环境,大家对于使用的软件框架有很多选择,今天我简单描述一些比较常用的架构,让大家能够理解并选择合适的架构。总述1. 简单的顺序执行程序:这类写法是大多数人使用的方法,不需用思考程序的具体架构,直接按照执行顺序编写应用程序即可。2.前后台

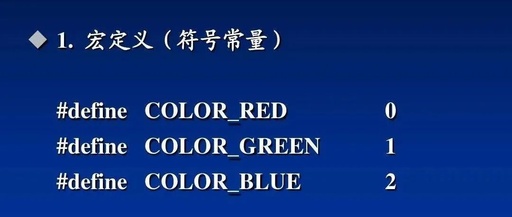

嵌入式 C 语言中,宏是在预编译时用宏体内容“文本替换”代码中的宏名的。先讲一些宏嵌套的展开规则:1、一般的展开规律像函数的参数一样:先展开参数,再分析函数,即由内向外展开。2、当宏中有#运算符的时候,不展开参数。3、当宏中有##运算符的时候,先展开函数,再分析参数。4、##运算符用于将参数连接到一

一、前言耦合性是程序结构中各个模块之间相互关联的度量。它取决于各个模块之间接口的复杂程度、调用模块的方式以及哪些信息通过接口。编写代码有两个核心点:隔离变化、降低复杂度,而解耦是达到这两个目标的重要手段。二、使用回调函数降低耦合 问题描述:实现回家函数come_home,传入出发的时间,打印回家的方

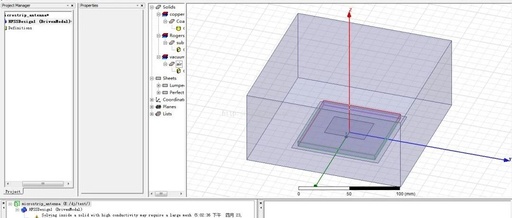

我们知道HFSS是一款电磁仿真商用软件,用其进行天线的设计十分方便。而该软件也预留了可以运行脚本的接口,使用者可以使用脚本对软件进行控制,实现模型的建立、求解等等。由于后期可能会用到联合仿真,而大多数联合仿真的脚本都是使用的Matlab进行编程,网上也有不少现成的api,因为对python比较熟悉,

创建 FPGA 设计和维护 Vivado® 设计套件项目时,版本控制系统对于团队合作可能是一项具有挑战性的任务。工程师必须能跟踪设计变更,完整地从 HDL 或 TCL 源代码再现项目并交付特定的项目状态。Vivado 工具非常适用于这类工作

JVM底层原理解析

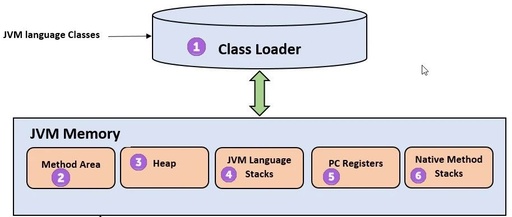

hi ,大家好,我是极客重生的Alex,今天分享一篇JVM底层原理的文章,希望可以帮助大家了解一下语言虚拟机一些设计原理,不管你当前使用语言是C,C++,Golang,Python等,很多思想和原理是相通的,可以借鉴。比如之前分析内核虚拟机eBPF架构:在本文中,您将学习JVM架构软件代码编译执行流

扫码关注

扫码关注