- 全部

- 默认排序

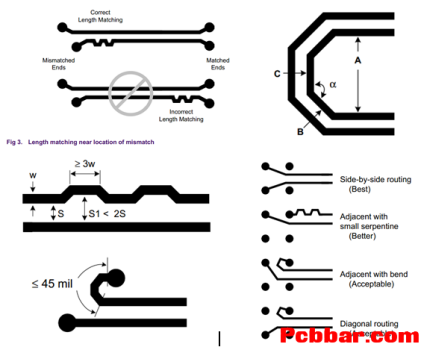

差分走线,信号换层过孔数量,等长长度把控,阻抗控制要求,跨分割的损耗,走线拐角的位置形状,绕线方式对应的插损和回损,布局不妥当造成的一系列串扰和叠层串扰,布局不恰当操作焊盘存在的stub。

通用串行总线(英语:Universal Serial Bus,缩写:USB)是连接计算机系统与外部设备的一种串口总线标准,也是一种输入输出接口的技术规范,被广泛地应用于个人电脑和移动设备等信息通讯产品,并扩展至摄影器材、数字电视(机顶盒)、游戏机等其它相关领域。最新一代是USB 3.1,传输速度为10Gbit/s,三段式电压5V/12V/20V,最大供电100W ,新型Type C插型不再分正反,如图4-8所示,展示了几种常用的USB接口实物,这类型USB接口广泛应用于MID的产品中

串行总线的发展一共目前可以总结分为3个环节时期, 时钟并行总线:小于200MHZ,比如CPCI,PCIX,SDRAM,ISA,PIC 源同步时钟并行总线:小于3200Mbps,比如DDRr1234系列,MII,EMMC 高速串行总线:最高有56NRZ ,比如USB1/2/3/3.1/3.2,PCIE3,PCIE4,SAS3,SAS4.

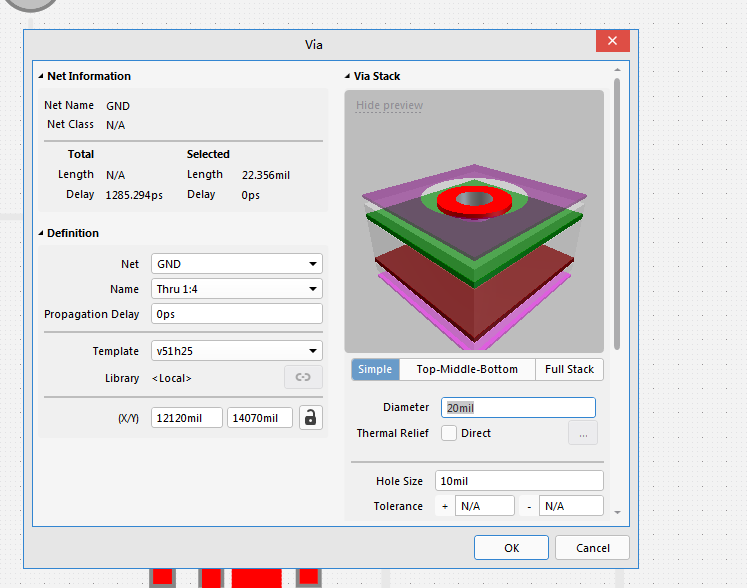

有时候为了为了增大内层的敷铜面积,特别是BGA区域,尤其在高速串行总线日益广泛的今天,无论是PCIE,SATA串行总线,还是GTX,XAUI,SRIO等串行总线,都需要考虑走线的阻抗连续性及损耗控制,而对于阻抗控制,主要是通过减少走线及过孔中的STUB效应对内层过孔进行削盘处理。

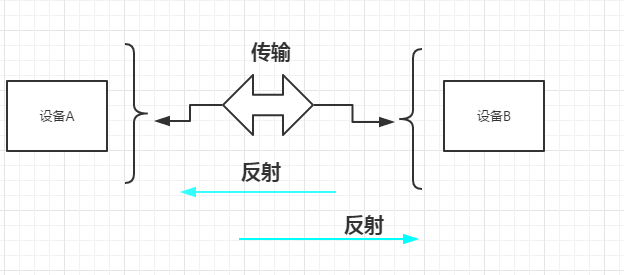

至于USB,SATA,PCIE等串行信号,并没有上述并行总线的时钟概念,其时钟是隐含在串行数据中的。数据发送方时钟包含在数据中发出,数据接收方通过接受到的数据恢复出时钟信号。这类串行总线没有上述并行总线等长布线的概念。但因为这些串行信号都采用差分信号,为了保证差分信号的信号质量,对差分信号对的布线一般会要求等长且按总线规范的要求进行阻抗匹配的控制

随着科技迭代发展,电子设备的接口类型也在迭代更新中,造成市场上有较多的接口及协议,那么市场上有哪些接口?它们各有什么优缺点?今天为小伙伴们盘点下!USB全称为Universal Serial Bus,即通用串行总线,是一种输入输出接口的技术

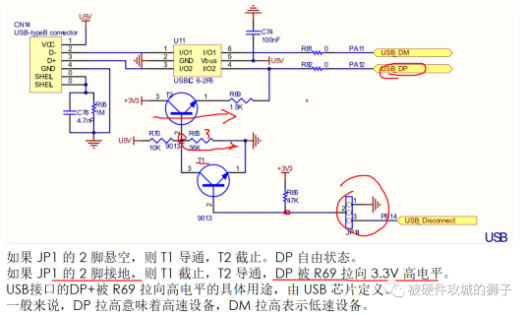

从一个电路说起:Eg:DP+被拉高具体是什么用途,由USB Controler决定,本电路图中DP+被拉高禁用USB设备.1.USBUSB:UniversalSerial Bus,中文译为“通用串行总线”,USB设备最显著的优点是具有热插拔

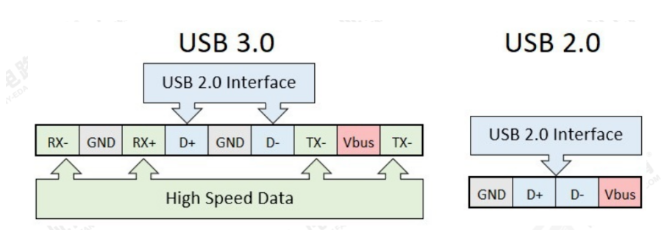

USB 2.0和USB 3.0是最常见的通用串行总线,也是应用广泛的输入输出技术规范,也是由Intel公司开发的总线架构之一,被广泛应用在个人电脑和移动设备等信息通讯产品,因此是工程师最为了解的接口之一,但很多人可能不太清楚USB 2.0/

熟悉硬件/单片机的工程师,想必对PCIe接口不陌生吧!PCIe是一种高速串行总线接口,主要功能是数据传输,被广泛应用计算机、工业控制等多种领域。若是遇见PCIe的PCB项目该如何做?不如来看看这篇文吧!本文将介绍PCIe接口的PCB设计技术

USB是通用串行总线的英文缩写,是连接外部装置的一个串口总线标准,也是一种输入输出接口的技术规范,被广泛地应用于个人电脑和移动设备等信息通迅产品,并扩展到摄影器材,数字电视(机顶盒)、游戏机等其它相关领域。USB2.0接口具有高达480Mb

扫码关注

扫码关注