- 全部

- 默认排序

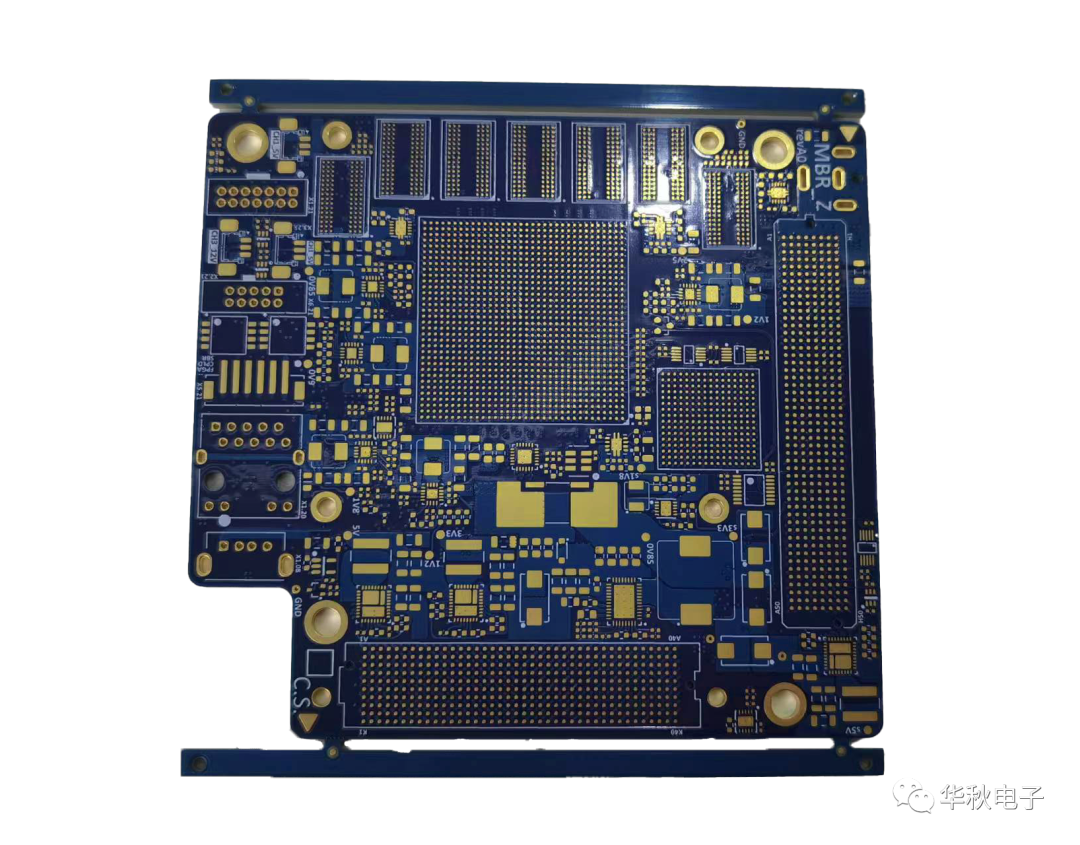

随着高频高速电子产品的快速发展,信号传输过程更容易出现反射、串扰等信号完整性问题,且频率越高、传输速率越快,信号损耗越严重,如何降低信号在传输过程中的损耗、保证信号完整性是高频高速PCB发展中的巨大挑战。在高速PCB设计中,阻抗匹配显得尤为

在现代高速电子设备中,PCB板的阻抗测量和控制是至关重要的技术,准确的阻抗设计和测量可确保产品的信号完整性、抑制信号串扰及提高系统性能,因此是很多电子工程师的重点学习内容,下面聊聊PCB阻抗测量及控制方法。一、PCB板上如何测量阻抗?1、T

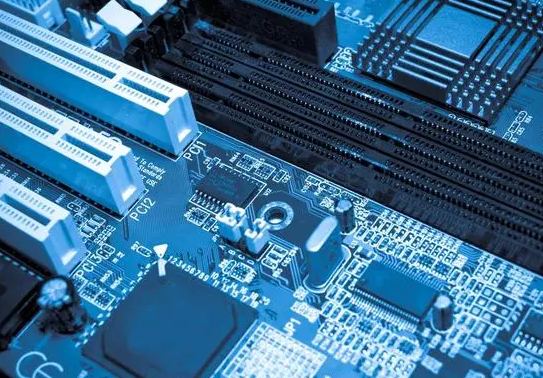

在现代电子设计中,高速信号的传输变得越来越常见,然而高速信号传输过程中总会遇见信号耦合和串扰等问题,这些现象将导致信号完整性的损坏,从而影响系统的性能和可靠性,那么下面将聊聊如何解决信号耦合和串扰等问题。1、信号耦合和串扰的产生高速信号传输

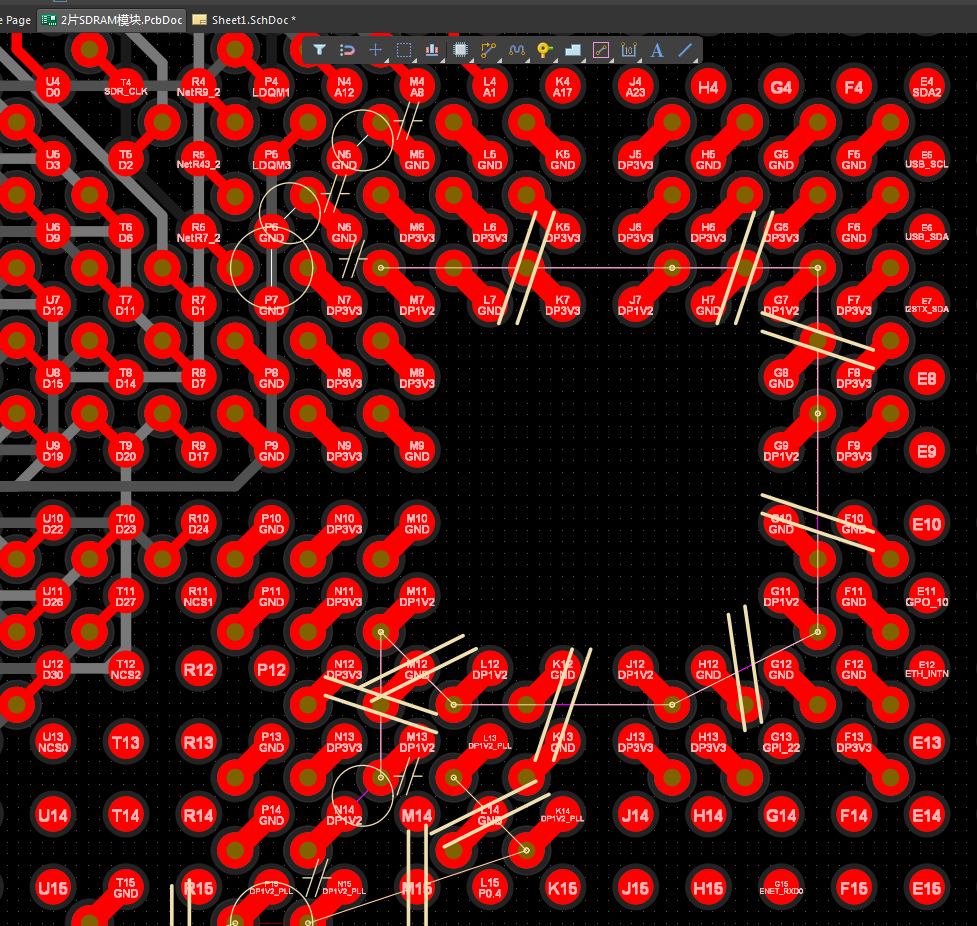

注意数据跟地址,时钟,控制之间用GND走线隔开:建议等长线的GAP也尽量满足3W,避免自身的串扰:等长不是很美观,尽量采取咬合等长,既美观也节省空间,还可以调整下美观性:上述一致原因,注意等长线的gap:其他的等长没什么问题,只要是等长美观

电源信号都没有处理:注意等长线的GAP尽量满足大于等于3W长度:可以减少串扰。注意看下xsignals分组 U16 -U17没有信号:数据跟地址用GND走线隔开:此处电源可以在电源层分割:以上评审报告来源于凡亿教育90天高速PCB特训班作业

PCB设计,细节要牢记,技巧规范,别忘记。元件选择,要慎重权衡,性能优化,细节考虑。电路布局,尺寸精确,差分信号,清晰准确。地平面铺,阻抗匹配,多层堆叠,功耗降低。信号路径,长度平等,串扰减小,信噪比增。参考设计,莫忽略,静电防护,接地要密

今天主要是关于:EMC,PCB设计中如何降低EMC?一、EMC是什么?在PCB设计中,主要的EMC问题包括3种:传导干扰、串扰干扰、辐射干扰。1、传导干扰传导干扰通过引线去耦和共模阻抗去耦影响其他电路,例如:噪声通过电源电路进入系统,支持电路将受到噪声的影响。下图显示了通过共模阻抗进行的噪声去耦。电

PCB设计,细节要牢记,技巧规范,别忘记。元件选择,要慎重权衡,性能优化,细节考虑。电路布局,尺寸精确,差分信号,清晰准确。地平面铺,阻抗匹配,多层堆叠,功耗降低。信号路径,长度平等,串扰减小,信噪比增。参考设计,莫忽略,静电防护,接地要密

随着半导体集成度越来越高,PCB层间的串扰问题愈发严重,虽然很多电子工程师通过3W规则来解决串扰,但你知道吗?还有很多方法可以抑制PCB板的串扰问题。串扰CrossTalk)是指PCB上不同网络之间因较长的平行布线引起的相互干扰,主要是由于

随着半导体集成度越来越高,PCB层间的串扰问题愈发严重,虽然很多电子工程师通过3W规则来解决串扰,但你知道吗?还有很多方法可以抑制PCB板的串扰问题。串扰CrossTalk)是指PCB上不同网络之间因较长的平行布线引起的相互干扰,主要是由于

扫码关注

扫码关注