- 全部

- 默认排序

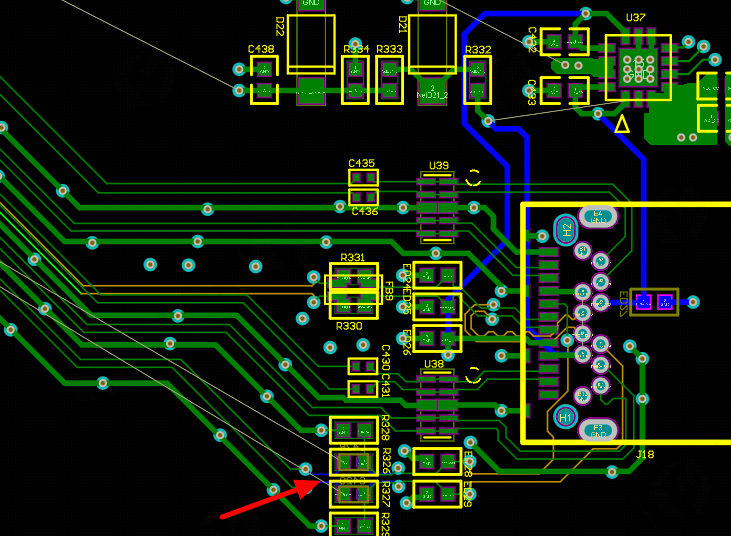

多处飞线未连接差分出焊盘后尽快耦合差分对内绕线不符合规范存在报错未处理差分走线不耦合,前后前后线距不一致兼容器件这样布局差分对内等长控制5mil误差,有两对差分走线没有建立差分对,没有加入差分组以上评审报告来源于凡亿教育90天高速PCB特训

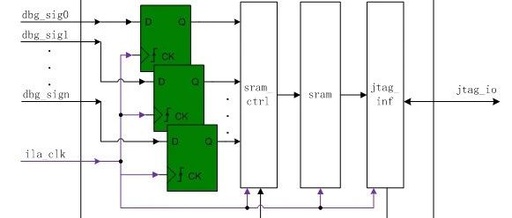

1. 前言在数字IP/IC,FPGA项目的上板验证阶段,对于一些难以确定原因的bug,比如:RTL仿真时,测试pattern覆盖不够全面,fpga跑起来后的实际信号时序可能跟RTL 仿真不一致,从而出现Bug。一种debug的方式就是用FPGA工具提供的ILA模块(xilixn在ISE中叫:chip

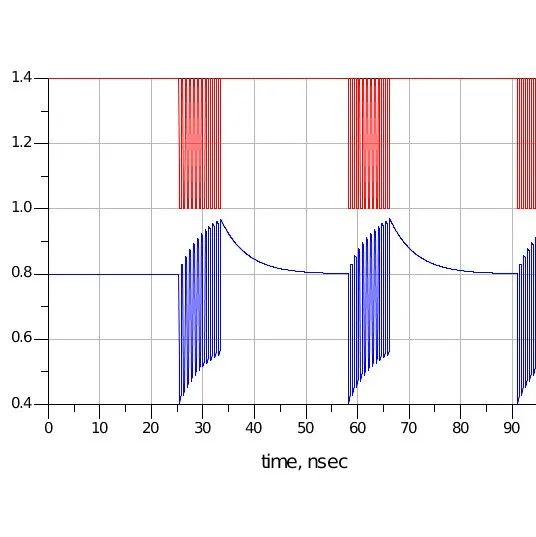

【摘要】信号的AC耦合方式具有屏蔽发送端和接收端直流偏置不一致的好处,但并不是所有信号都适合使用这种方式传输,即只有直流平衡信号(数据流中的1与0的数量相等的状态)才可以。本文试图从电容充放电的角度,解释非直流平衡信号不适用于AC耦合方式传输的原因。一、问题的提出在某系统研发过程中,出现了2次串行数

原理图中有多个相同的模块,为了方便,我把PCB的其中一个模块先画好,然后批量复制,导致器件的位号和原理图不一致,网络也没了,怎么实现PCB和原理图位号同步并还原网络呢

规则设置过孔是10-18mil,放置时使用快捷键P+V或者点击工具栏放置的过孔为28-50mil,而在走线状态下按下“*”键防止的过孔是和规则一致的

大神们好! 看了郑总的2层板视频,根据视频设置了走线规则和过孔规则后在走线或防止过孔时发现尺寸和设置的规则不一致。具体情况如下:过孔 规则设置过孔是10-18mil,放置时使用快捷键P+V或者点击工具栏放置的过孔为28-50mil,而在走线状态下按下“*”键防止的过孔是和规则一致的,如下图:问

请教各位引脚数不一致问题,在库中已经修改,但是这里显示具体设计中没有修改一直报error,这个封装一直不能更新成功,placement这个件放不进,这个该怎么解掉

扫码关注

扫码关注