- 全部

- 默认排序

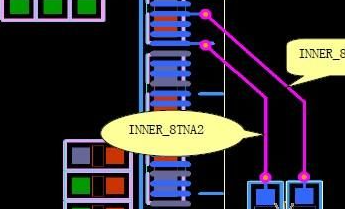

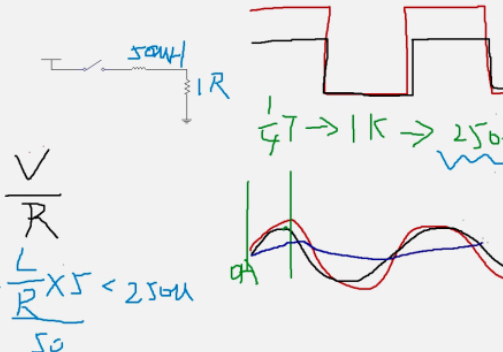

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。等长走线的目的就是为了尽可能的减少所有相关信号在PCB上的传输延迟的差异。高速信号有效的建立保持窗口比较小,要让数据和控制信号都落在有效窗口内,数据、时钟或数

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。

同步电路是数字电路中常见的电路设计方法之一,但部分小白对该类电路不甚了解,甚至遇见该类设计是惘然无措,所以本文将重点分析同步电路的设计准则,并分享电路设计的优点。同步电路是指所有电路在同一个公共时钟的上升沿或下降沿的触发下同步地工作。但在实

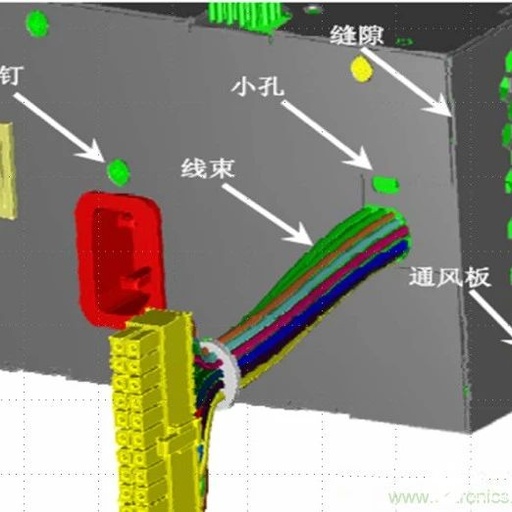

人们在研发新产品时,往往急于实现产品的功能,于是沿用低频、低速时的经验,满足于利用软件将单片机、芯片和元器件连接起来,就希望实现产品功能、效能和性能,结果事与愿违,不仅只是在低水平徘徊,而且延误了宝贵的时间。其实,随着集成电路时钟速率的提高,上升、下降沿速率加快,电源电压降低以及产品复杂性和密集度的

RGMII接口是MAC和PHY之间常用的千兆网通信接口,采用4bit数据接口,工作时钟为125Mhz,并且上升沿和下降沿同时传输数据,因此传输速率可达1000Mbps。RK3588芯片拥有2个GMAC控制器,提供RMII或RGMII接口连接

扫码关注

扫码关注