- 全部

- 默认排序

高速高密度多层pcb板的SI/EMC(信号完整性/电磁兼容)问题长久以来一直是设计者所面对的最大挑战。然而,随着主流的MCU、DSP和处理器大多工作在100MHz以上(有些甚至工作于GHz级以上),以及越来越多的高速I/O埠和RF前端也都工作在GHz级以上,再加上应用系统的小型化趋势导致的PCB空间缩小问题,使得目前的高速高密度pcb板设计已经变得越来越普遍。许多产业分析师指出,在进入21世纪以后,80%以上的多层PCB设计都将会针对高速电路。

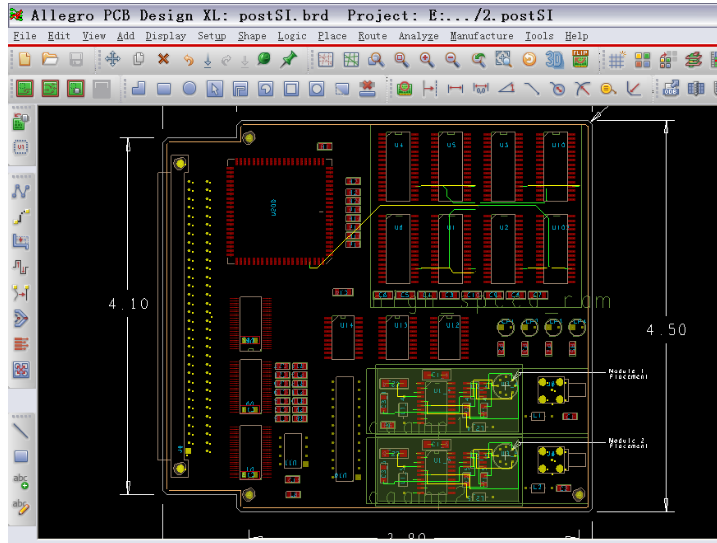

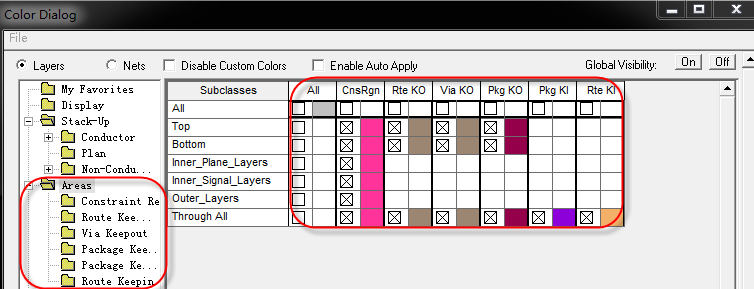

我们在进行PCB设计的时候,需要根据不同的pcb板结构以及一些电子产品的需求来进行各种不同区域的设计,包括允许布局区域设计、禁止布局区域设计。允许布线区域设计等等。在Allegro设计中,设置这些就在Areas,如图5-60所示。 图5-60 各类布局布线区域示意图Ø 在Allegro软件中有Route Keepout、Route Keepin、Package Keepout、Package Keepin、Via Keepout等多种类型的区域进行设置,对PCB工

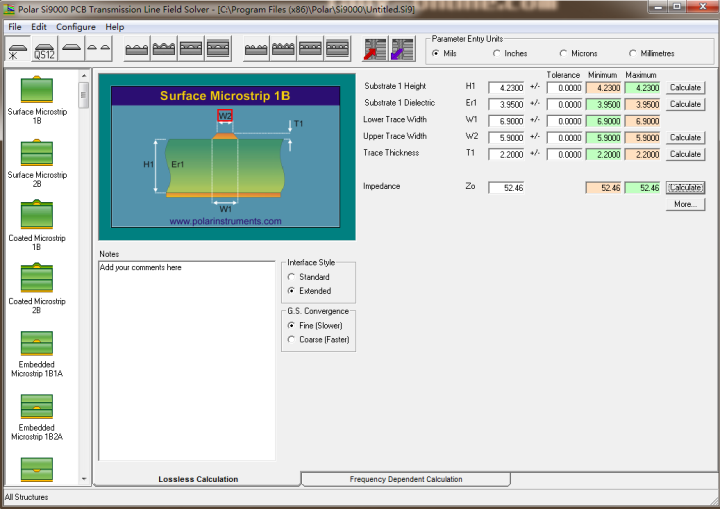

特性阻抗,体现在pcb板上,主要是通过叠层、线宽、线距。在PCB版图布局完成以后,我们要对pcb板进行层叠设计,将pcb板按照一定的厚度叠好以后,根据层叠结构,通过SI9000这个软件来进行阻抗线宽的计算,然后根据计算好的线宽来进行布线,即可达到控制特性阻抗的效果。如图1-21所示,1.6MM的厚度的pcb板的层压结构。TOP0.5oz +PlatingPP(2116)4.23GND021ozCore20.08ART031ozPP(1080*2)4.59PWR041ozCore20.08GND0

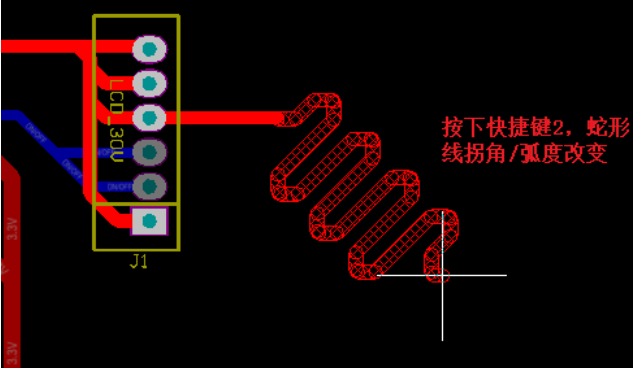

PCB上的任何一条走线在通过高频信号的情况下都会对该信号造成时延时,蛇形走线的主要作用是补偿“同一组相关"信号线中延时较小的部分,这些部分通常是没有或比其它信号少通过另外的逻辑处理;最典型的就是时钟线,通常它不需经过任何其它逻辑处理,因而其延时会小于其它相关信号。

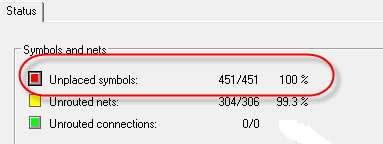

很多刚开始接触这个Allegro软件的同学,就有这样的疑问,我的原理图的网表都已经导入到PCB中了,为什么pcb板上什么都没有呢?元器件、飞线等都没有。其实,只要是网表导入到PCB中,器件都是在后台显示,需要指定元器件封装库,然后手动放置出来,下面我们详细介绍一下操作的办法:第一步,需要检查原理图的网表是否导入成功,执行菜单命令Display,在下拉菜单中选择Status,整个PCB文件的状态,如图324-1所示,进入到状态的界面,最上面一栏是Symbols and nets的选项,网表导入成功

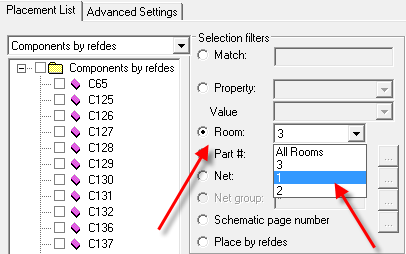

上述我们讲解了怎么快速的将元器件放置在pcb板上,通过图6-40所示的图可以看出,器件放置的都是很零散的,不是按模块或者是按页放置的,这里给大家介绍一些,通过在原理图添加ROOM属性,然后通过ROOM框在pcb板上来放置元器件,这样就可以根据模块或者一页原理图去发放置元器件了,具体操作如下:第一步,需要对原理图中的元器件添加ROOM属性,这个在前面的问答中已经讲述过了,这里不再做赘述,然后导入网表到PCB中;第二步,在PCB中绘制ROOM框,执行菜单命令Setup-Outlines-ROOM O

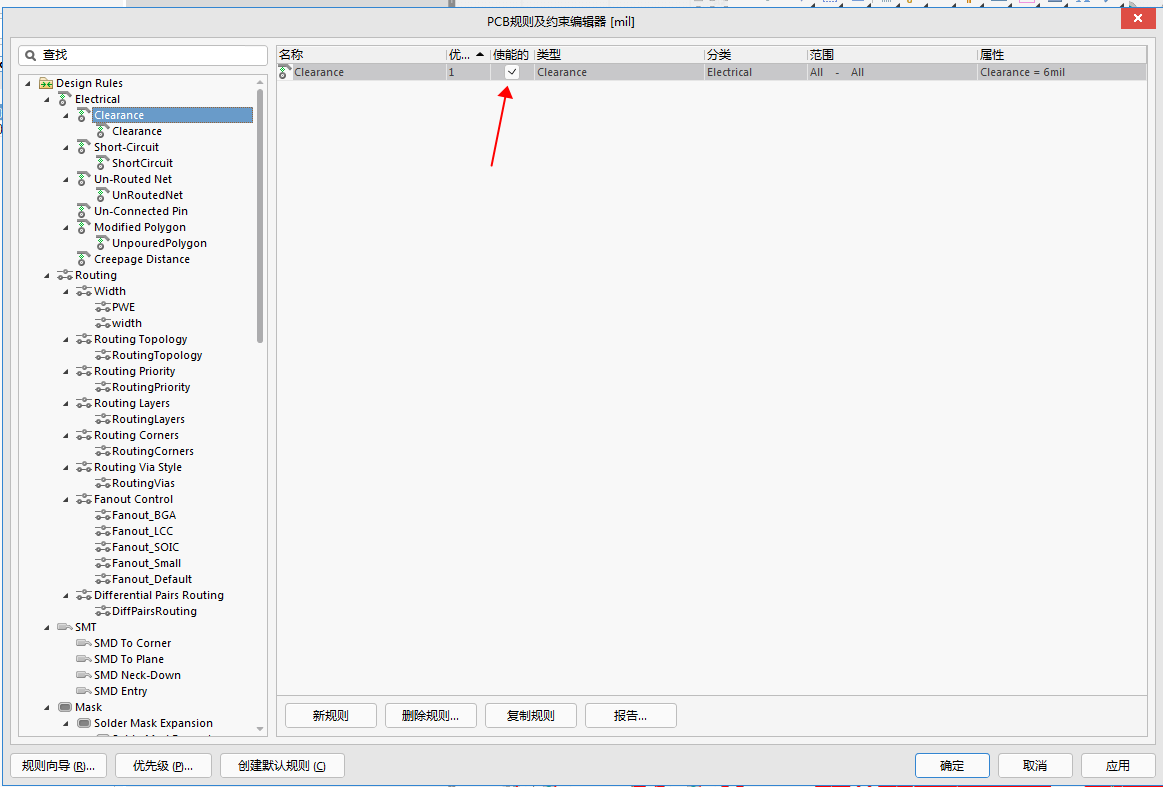

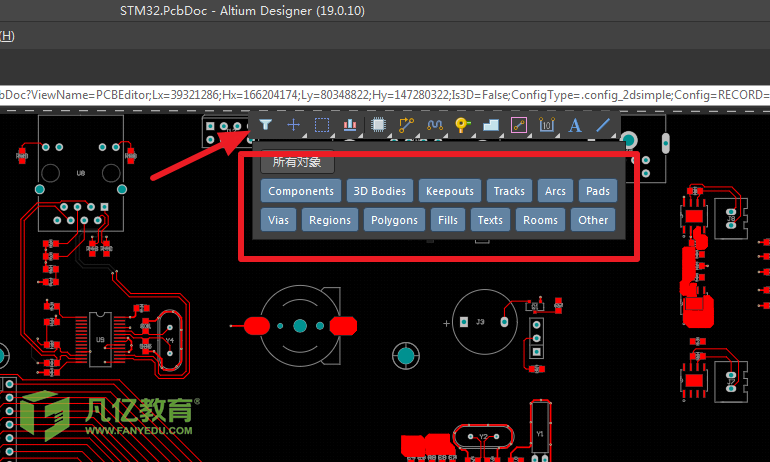

我们在根据pcb板的要求,在规则编辑器里面加入了很多对应的规则。比如:间距规则,线宽规则,短路等都是非常重要的电气规则规则,及其重要性是非常重要。

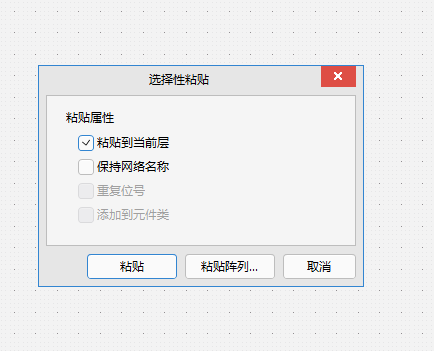

怎么样等间距的复制很多过孔?怎么带网络的复制走线?又或者是怎么样把元件的位号及网络从当前的这个PCB调用到另一个pcb板中呢?PCB设计当中经常会遇到这些问题,可以使用特殊粘贴也可以称为智能粘贴法来实现。

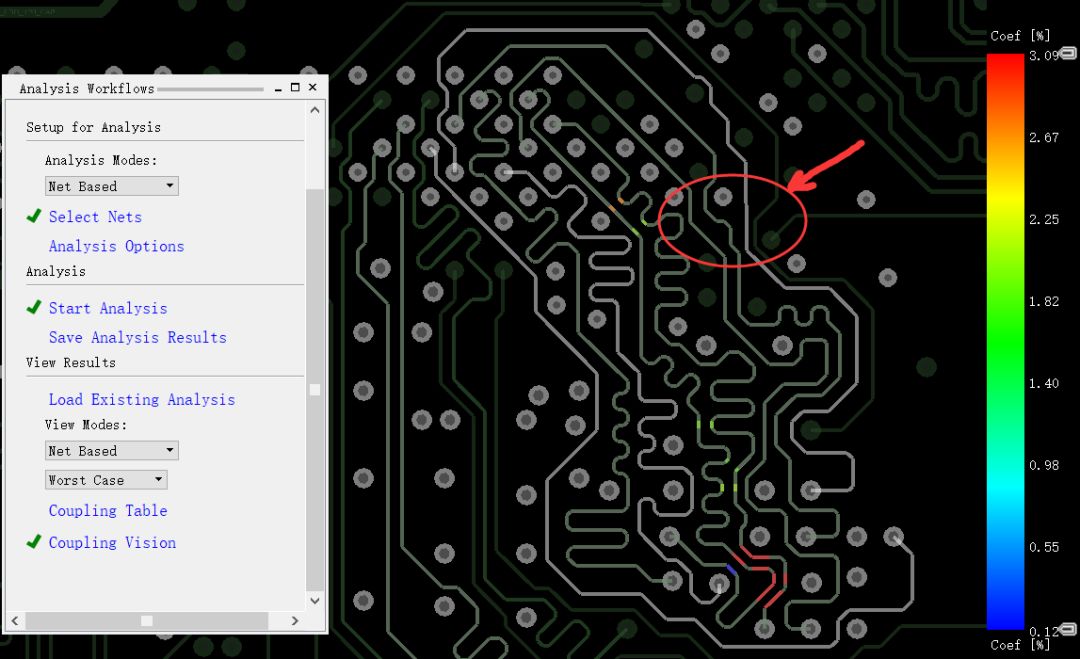

串扰是两条信号线之间的耦合、信号线之间的互感和互容引起线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。 pcb板层的参数、信号线间距、驱动端和接收端的电气特性及线端接方式对串扰都有一定的影响。下面是在SigXplorer里面搭建了一个串扰的仿真链路,黄色部分就是得到的信号之间的串扰分析结果。

扫码关注

扫码关注