- 全部

- 默认排序

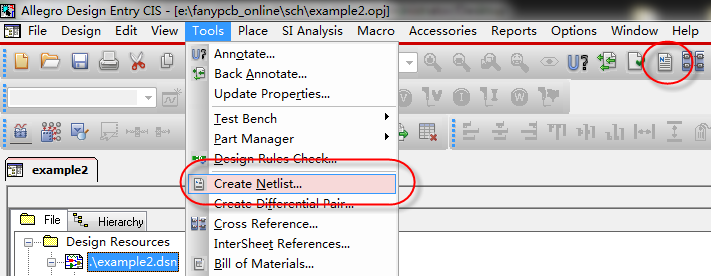

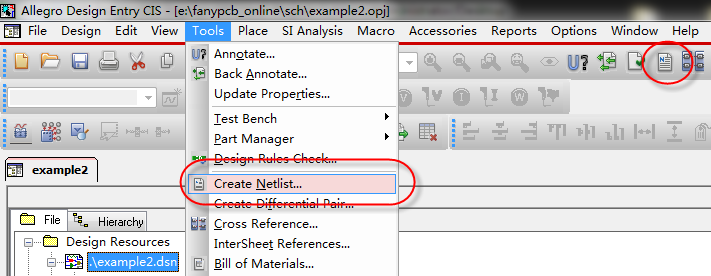

现在市面上用的最多的是,Orcad软件绘制原理图,Allegro软件绘制PCB版图。我们现在讲解一下怎么使用Orcad软件将绘制好的原理图,输出第一方的网表,然后将第一方的网表导入到Allegro软件中,具体操作如下:第一步,选中原理图根目录,执行菜单命令Tools-Create netlist,创建网表,如图6-26所示; 图6-26 使用Orcad软件创建第一方网表示意图第二步,执行上述命令之后,会弹出如图6-27所示的界面,在此界面中选择PCB Editor,进行第一

我们在进行原理图设计的时候,完成之后就需要去进行网表的导出,然后在pcb中去进行设计。有很多学员在原理图导出网表的这一操作中会出现各种各样的报错,那么今天我们就来看看最常见的一项导出网表的报错的解决办法,即”netlister failed”的报错。

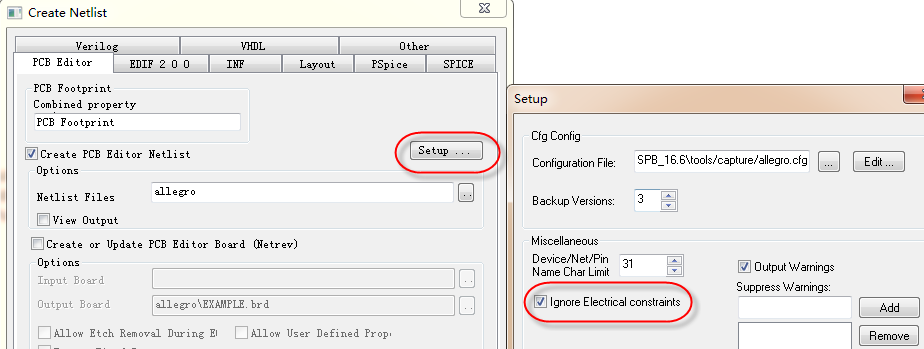

答:orcad产生Cadence Allegro的网表的操作步骤如下;第一步,选择原理图根目录,执行菜单Tools→Creat netlist,或者是点击菜单栏上的图标,调出产生网表的界面,如图3-68所示; 图3-68 产生网表示意图第二步,弹出的Creat netlist界面中,选择的是PCB Editor,产生Allegro的第一方网表,如图3-69所示; 图3-69 Allegro第一方网表参数设置示意图第三步,输入Allegro第一方网表需要注意下面几个

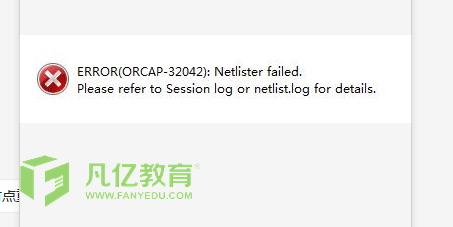

答:使用Orcad软件进行输出Allegro第一方网表时,弹出如图3-72所示的界面,这个是表示原理图有错误,不满足Allegro软件的要求,不能输出网表, 图3-72 输出Allegro网表报错示意图在输出Allegro第一方网表弹出这个界面,我们需要找到如图3-72所示的netlist.log这个文件,原理图中存在的错误在这有详细的描述,这个文件一般存储于输出网表的那个文件夹下,用写字本文件打开此文件,如图3-73所示,将列表中所列的错误一一解决掉,即可输出网表文件了。

答:orcad产生Cadence Allegro的网表的操作步骤如下;第一步,选择原理图根目录,执行菜单Tools→Creat netlist,或者是点击菜单栏上的图标,调出产生网表的界面,如图3-74所示; 图3-74 输出网表示意图第二步,弹出的输出网表界面中选择Other选项,来输出第三方网表,如图3-75所示,在Formatters栏中选择orTelesis.dll选项,上面的Part Value栏需要用PCB Footprint来代替,不然会产生错误;

答:我们在进行PCB设计的时候呢,尽量不要把原理图的规则导入到PCB中,我们需要在输出网表的时候进行设置,具体的操作步骤如下所示:第一步,选中原理图的根目录文件即DSN文件,进行网表的输出,执行菜单Tools-Create netlist,创建网表;第二步,在弹出的输出PCB网络表的对话框中,其它地方都是不用勾选的,在右侧有一个Setup选项,是输出网络的参数设置按钮,我们需要在这里进行不输出原理图规则的设置;第三步,点击输出网表的Setup选项,进行参数的设置,如图3-211所示,在左侧箭头所

用Design Entry CIS生成逻辑网表的时候没有报错,能够成功的生成pxlBA.txt,netlist.log,pstchip.dat,pstxnet.dat,pstxprt.dat五个文件,这五个文件在同一个文件夹netlist下。然后一个叫work2的文件夹使用PCB Design GX

这是什么问题?求解 protures提示:Simulation FAILED due to netlist compiler error(s)

扫码关注

扫码关注