- 全部

- 默认排序

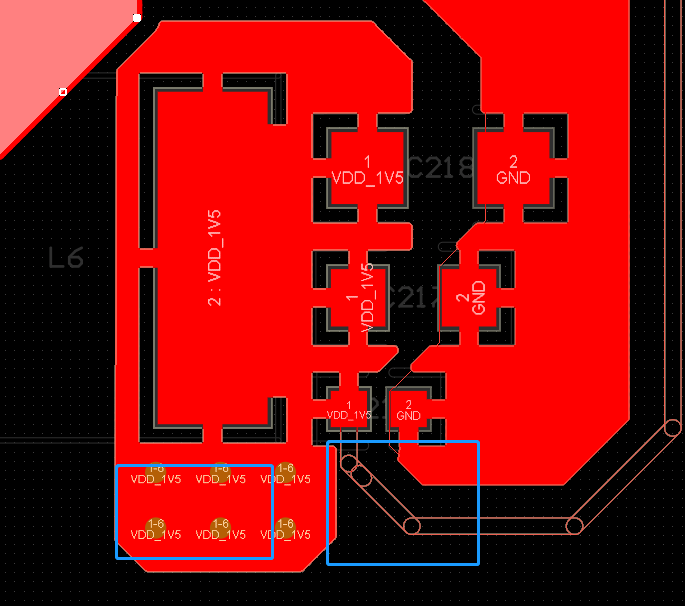

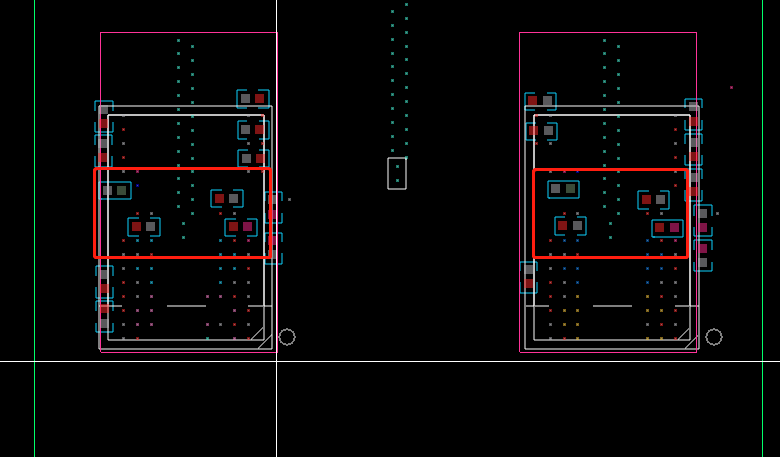

电源输出打孔要打在电容后面2.反馈信号要走10mil3.等长存在误差报错4.差分走要满足差分间距要求,等长原则是哪里不耦合,就在哪里进行等长5.VREF线宽最少要加粗到15mil以上6.注意器件摆放不要干涉以上评审报告来源于凡亿教育90天高

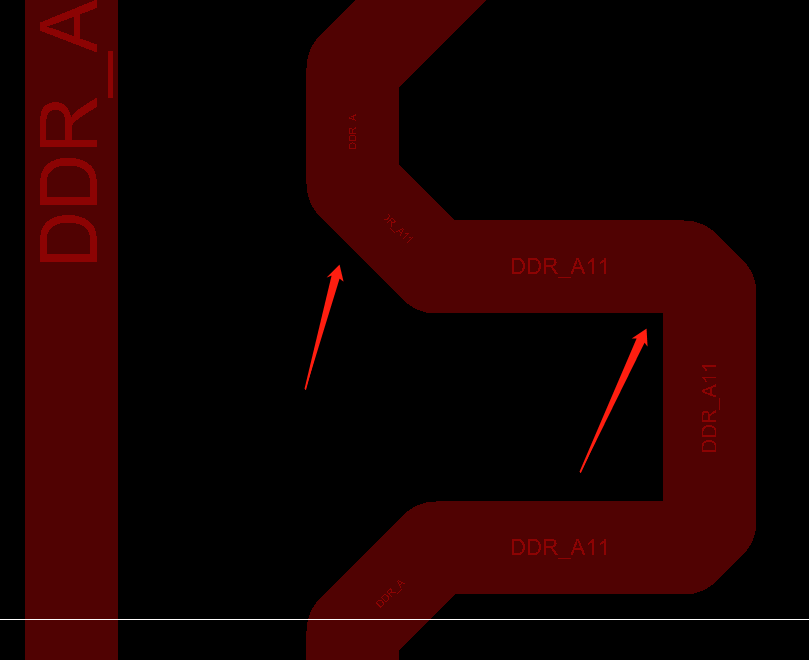

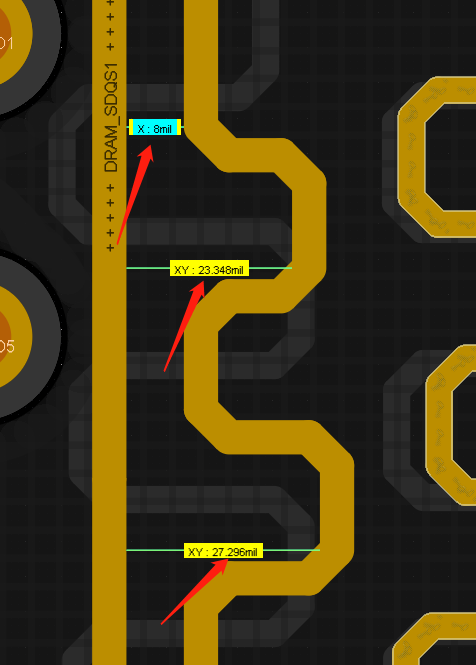

注意绕蛇形不要有直角2.差分线等长凸起高度不能超过线距的两倍3.存在多余的走线4.过孔不要上焊盘5.VREF的电源信号走线最少要加粗到15mil以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫

差分对内等长凸起高度不能超过线距的两倍2.注意T点的间距要求,后期自己看视频在了解一下3.地网络需要就近打孔,缩短回流路径4.VREF的电源最少要加粗到15mil以上5.此处不满足载流6.注意差分走线要尽量耦合,满足差分间距要求,控好阻抗7

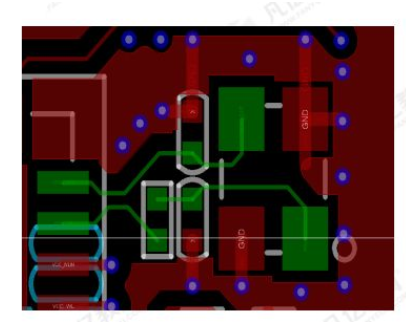

在现代电子设计领域,随着计算机性能的不断提升,高速数据传输变得越来越重要,ddr(双倍数据率)内存模块作为计算机系统的重要器件,其高速PCB布局布线显得尤为关键,正确的布线设计可提升ddr的稳定性、性能和可靠性,下面来总结下ddr模块的高速

电感所在层需要挖空处理2.差分对内等长凸起高度不鞥超过线距的两倍3.器件摆放靠近管脚,尽量短4.电源输出打孔要打在最后一个滤波电容的后面5.除了散热过孔,其他的都需要盖油处理6.器件摆放注意不要干涉7.差分出线要注意耦合以上评审报告来源于凡

在电子工程中,ddr(双数据速率)内存模块的设计和验证是很多电子工程师最头痛的问题之一,为了确保ddr模块在实际应用中稳定工作,信号仿真是必不可少的环节,然而如何选择仿真工具来进行?这些你知道吗?下面将列出几款常用于仿真ddr模块的软件,对

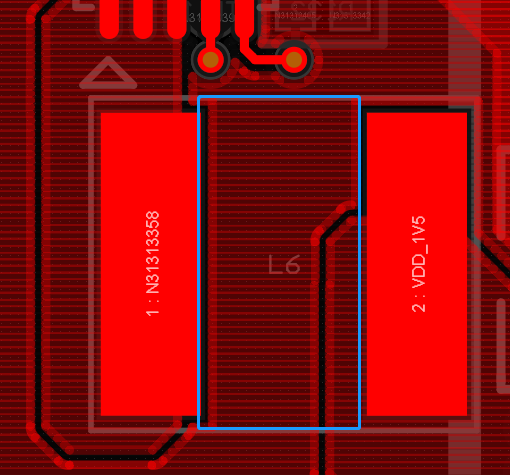

上期和大家聊的电源PCB设计的重要性,那本篇内容小编则给大家讲讲存储器的PCB设计建议,同样还是以大家最为熟悉的RK3588为例,详细介绍一下ddr模块电路的PCB设计要如何布局布线。由于RK3588 ddr接口速率最高达4266Mbps,

个别器件注意整体对齐:注意等长线之间需要满足3W间距原则:没满足的都自己优化下。数据线组内也需要满足3W:差分对内等长误差为5MIL:其他的没什么问题。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问

1、模块整体布局时,WIFI模组要尽量远离ddr、HDMI、USB、LCD电路以及喇叭等易干扰模块或连接座;2、晶体电路布局需要优先考虑,布局时应与芯片在同一层并尽量靠近放置以避免打过孔,晶体走线尽可能的短,远离干扰源,尽量天线区域;晶体以

随着半导体技术高速发展,越来越多电子产品迭代更新速度加快,高速度的数据传输及内存支持,这些都离不开ddr产品的支持,ddr产品已成为了大部分电子工程师的日常设计产品之一。然而ddr产品的设计是具有挑战性的,因为它涉及到高速数字电路和复杂的时

扫码关注

扫码关注