- 全部

- 默认排序

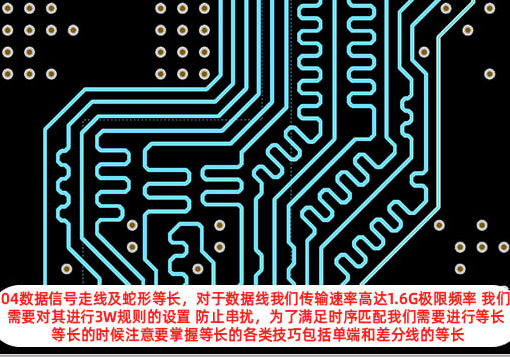

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(ddrSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。等长走线的目的就是为了尽可能的减少所有相关信号在PCB上的传输延迟的差异。高速信号有效的建立保持窗口比较小,要让数据和控制信号都落在有效窗口内,数据、时钟或数

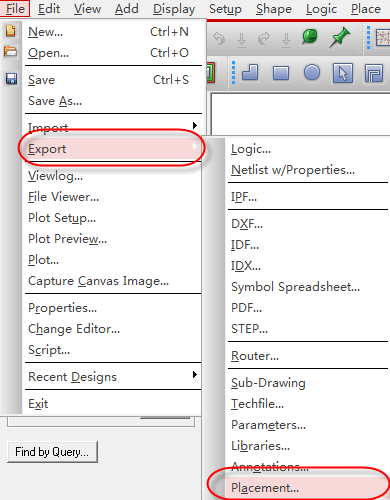

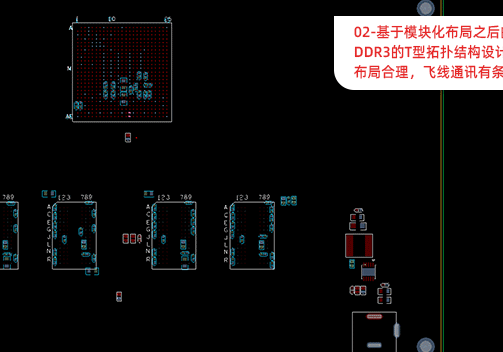

答:我们在进行PCB文件的修改时候,有时候回去复用一些以前已经处理好的模块的布局,比如ddr模块的布局、PMU模块的布局,我们这里讲述的是位号一致的情况,来直接根据坐标文件进行复用,具体操作的步骤如下所示:

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(ddrSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。

假设现在需要你去绘制一个产品PCB,我们是不是可以从HDMI、AV、RH45、WIFI、DCDC电源、PMU电源管理单元、ddr、FLASH存储器等等模块入手透析这个产品的本质, 了解好每一个模块的基本原理,再掌握每一个模块的PCB布局和PCB布线的要点,然后汇总整个设计, 这时你会发现这个PCB板子基本完成了80%的工作量,剩下的只是模块与模块之间的信号互联了。后续基本通过几个不同难度的全流程案例操作,基本就得心应手了。 训练营第一阶段:理清思路,开启高速无限可能 万丈高楼平地起。开课第一周

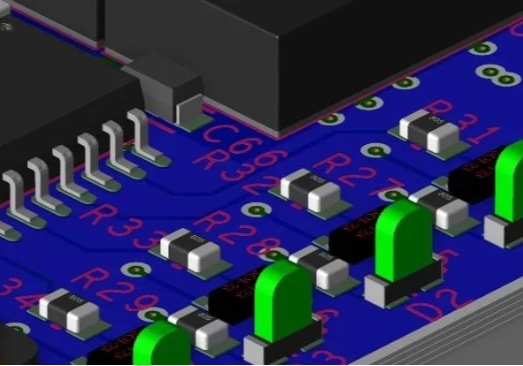

ddr布线技术的重要性在如今的印刷电路板设计中,双数据速率(ddr)存储器非常普遍。许多设计都会用到ddr存储器配置的不同版本,这需要在布局中使用特定的布线模式。ddr的名称来源于其能够在每个时钟周期内发送和接收两次信号,是原先的单数据速率

据外媒报道,三星已通知客户,ddr3内存芯片最后接单时间将截止到2022年末,并承诺会在2023年完成所有内存订单。凡亿教育带你走进ddr3:>>8层ddr3全流程PCB设计实战>>8层ddr3FLY-BY拓扑结构实战这意味着,从2024年

自ddr内存问世以来,由于它的大容量、高带宽、兼容性好等诸多特点,ddr产品很快占领内存市场并沿用至今。从ddr发展到ddr5。现在的ddr主流产品主要以ddr4为主,ddr3产品正走向落幕。今天将以ddr3和ddr4为主,重点谈谈它们之间

英特尔最新第12代酷睿处理器成功上线,首发支持ddr5成最大看点,这也将意味着内存领域又一次更新换代的开始:ddr5替代ddr4,虽然市面上ddr产品主要以ddr4为主。但我们可以分析ddr4和ddr5的区别及联系,对比其的性能差距。感兴趣

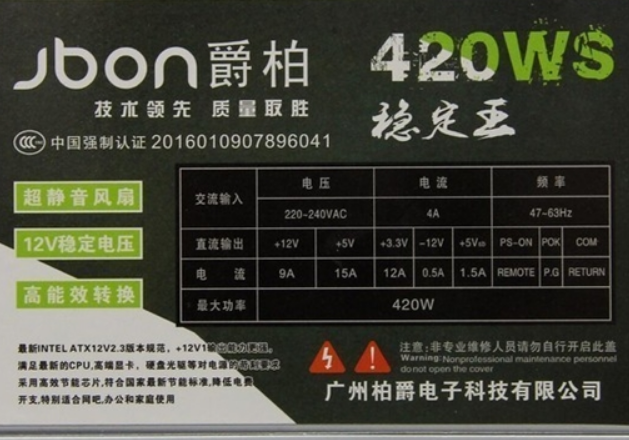

升级电脑,如何选购电源?

随着12代酷睿和ddr5内存的上线,不少玩家都有了升级电脑的念头,再加上显卡价格已经开始回落,让不少人已经开始往购物车里装硬件了。不过要注意的是,CPU和显卡都是耗电大户,如果你的电源跟不上,小马拉大车可容易出问题。那么电源应该如何选呢?首

自Intel 12代酷睿处理器问世以来,因全面支持PCle5.0协议和引入ddr5内存协议,而备受关注,这也宣告者内存更新换代的时代即将来临,ddr3和ddr4将连续走上舞台的落幕。凡亿教育ddr产品开发课程如下:>>Allegro 8层D

扫码关注

扫码关注