- 全部

- 默认排序

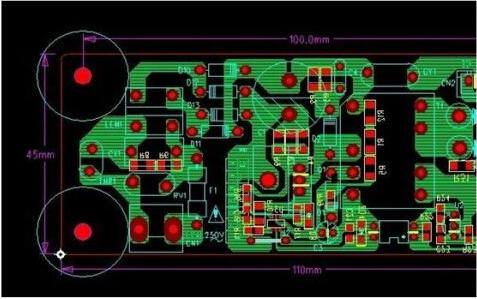

此Altium Designer视频是专门针对 ddr3 设计来的,采用飞思卡尔 IMX6 主控芯片, 4 片 ddr3 同层设计,采用 ddr3 常见的 T 点拓扑结构,一个大 T 点两个小 T 点的方式。讲解了 ddr3 设计的信号 class 分组,信号的同组同层及常用规则注意事项,信号完整性的规划等,让学习者知其然知其所以然。

一、PADS8层ddr3 Fly-by拓扑结构视频课程详情本pads视频课程基于飞思卡尔 i.MX6 处理器的 8层PCB设计,重点介绍 ddr3 内存的设计思路,一共四颗 ddr3,采用菊花链(Fly-By)的拓扑结构。讲解了 ddr3 设计的信号 class分组,信号的同组同层布线、信号时序等长及常用规则注意事项、信号完整性、电源完整性的规划等。

Allegro的全称是Cadence Allegro PCB Designer,是Cadence公司推出的一套完整的、高性能印制电路板设计套件。它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段进行定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。Allegro印制电路板设计提高了PCB设计效率和缩短设计周期,让您的产品尽快进入量产。Allegro是我们目前高速PCB设计中使用最多的工具。

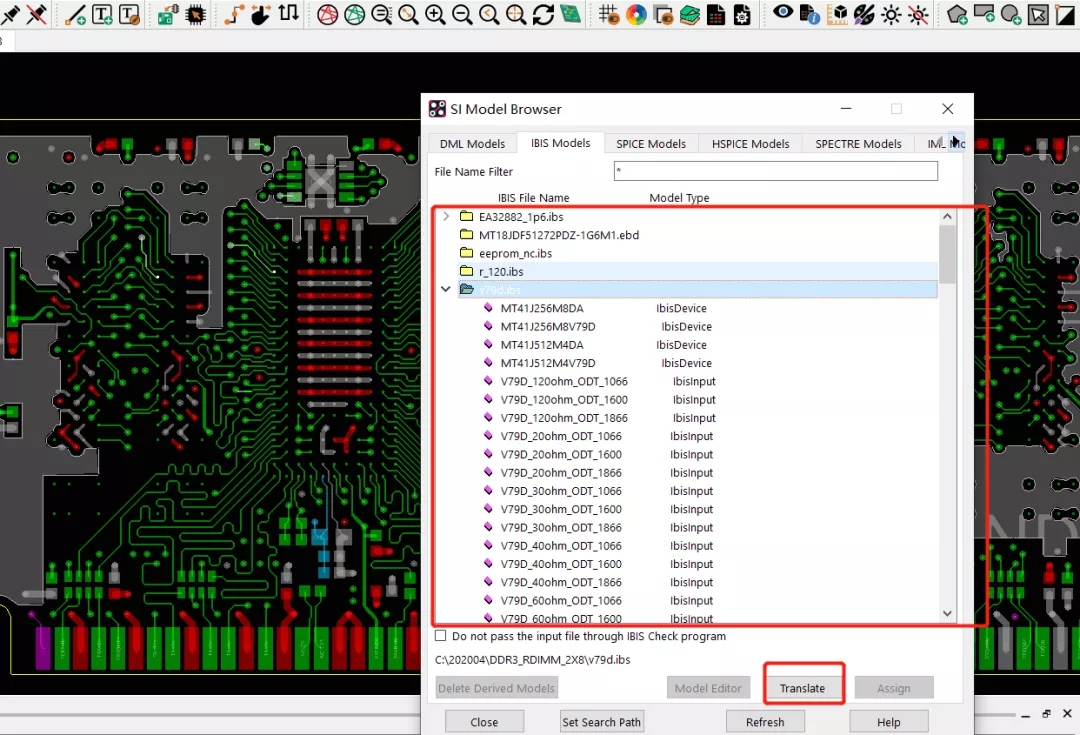

内存条,我们都知道它是电脑平台里不可缺少的一部分,最早开始到现在的ddr2、ddr3、ddr4一类的内存条。随着科技的发展,DIY各类产品层出不穷,而镁光成为内存的老啊·牌厂家,为无数王佳提供纵横游戏的尖端装备,据10月份的消息,Cadence和镁光公布了自己的ddr5内存研发进度,两家厂商一起开始研发16GBddr5的产品,并计划在2019年年底之前实现量产目标,

串行总线的发展一共目前可以总结分为3个环节时期, 时钟并行总线:小于200MHZ,比如CPCI,PCIX,SDRAM,ISA,PIC 源同步时钟并行总线:小于3200Mbps,比如ddrr1234系列,MII,EMMC 高速串行总线:最高有56NRZ ,比如USB1/2/3/3.1/3.2,PCIE3,PCIE4,SAS3,SAS4.

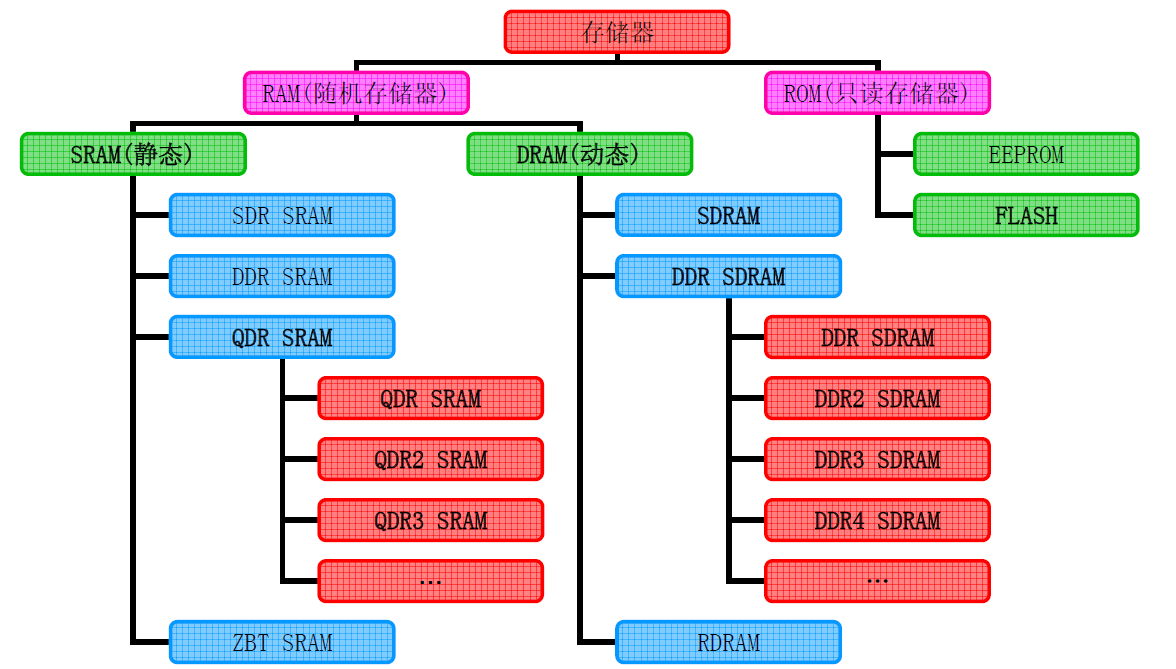

答:PCB设计中常用的存储器有如下几种:Ø SDRAM,Synchronous Dynamic Random Access Memory(同步动态随机存储器)的简称,SDRAM采用3.3v工作电压,带宽64位,SDRAM将CPU与RAM通过一个相同的时钟锁在一起,使RAM和CPU能够共享一个时钟周期,以相同的速度同步工作,与 EDO内存相比速度能提高50%;Ø ddr, Dual Data Rate双倍速率同步动态随机存储器,严格的说ddr应该叫ddr SDRAM,人们习惯称

扫码关注

扫码关注