- 全部

- 默认排序

上篇《dcdc的Layout终极奥义》中,我举的BUCK的例子,给出了我自己的布局走线方式。然后有两位兄弟留言说,他们会将Buck输入滤波电容按照最近的方式放置,开关节点SW打孔走出去,也就是下面这两种方式的右边那种。 这两种方式最大的区别就是SW的处理不一样,我之前也有想过,不过我无法确定哪种方式

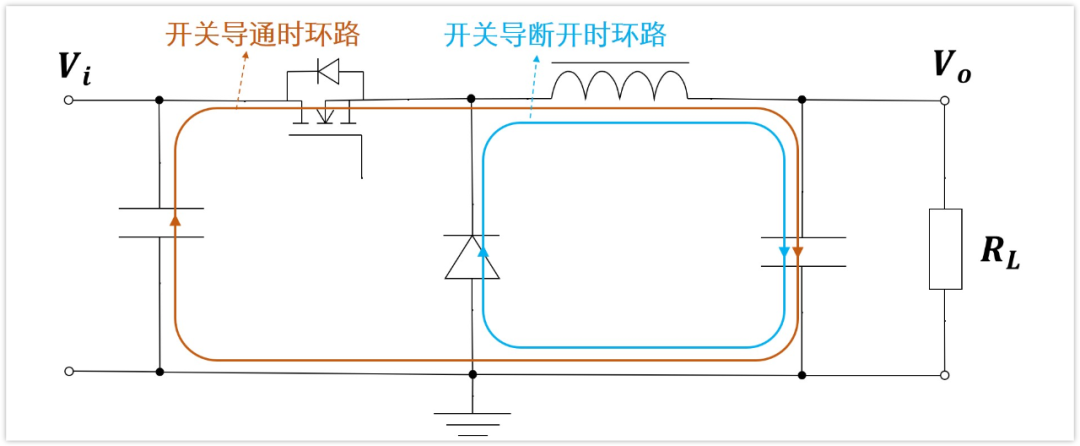

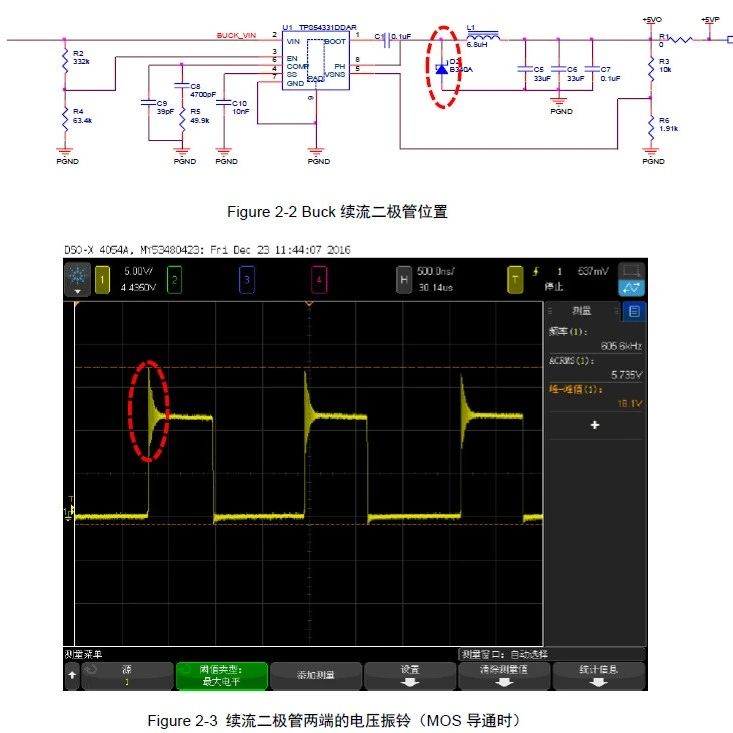

关于Buck和Boost的,我已经写了几篇,不过很少提到PCB Layout,这篇就说说PCB Layout。 很多dcdc芯片的手册都有对应的PCB Layout设计要求,有些还会提供一些Layout示意图,都是大同小异的。比如我随便列几点buck的设计要点:1、输入电容器和二极管在与IC相同的面

相信每个硬件工程师应该都用过DC-DC,那么分压反馈电阻的取值有没有想过呢?实际应用中大抵都是直接抄的手册中推荐的分压电阻阻值,就算没有正好对应输出电压的分压阻值,也一般是选择接近的电阻大小。但是,总会有个别人可能想过:我想降低系统功耗,因此想让FB的分压电阻成倍增大,那到底有没有风险呢?最近在自己

分享一个EMI整改文档,对于EMC来说,接触的案例越多,整改的成功率就越高,整改的方法也越多,从案例中吸取教训,总结经验,避免设计中出现同样的问题。注意:按照文档描述,从下面两张图片可以看出470MHz和940MHz(二次谐波)左右,这两个频点的功率非常高,可能该产品是一款无线产品,对于主频--有意

在电子设计中,dcdc转换器常用于将输入电压降至所需的输出电压,在使用时,工程师可能会考虑在dcdc降压前使用分压电阻来降低输入电压,以此减少压差,这种做法是可行的吗?1、分压电阻的基本原理分压电阻通过串联在电路中的方式,利用欧姆定律(V=

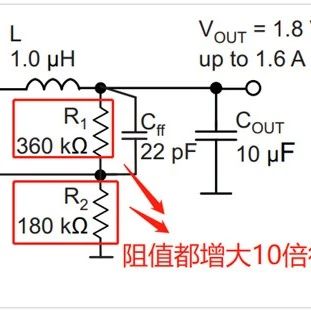

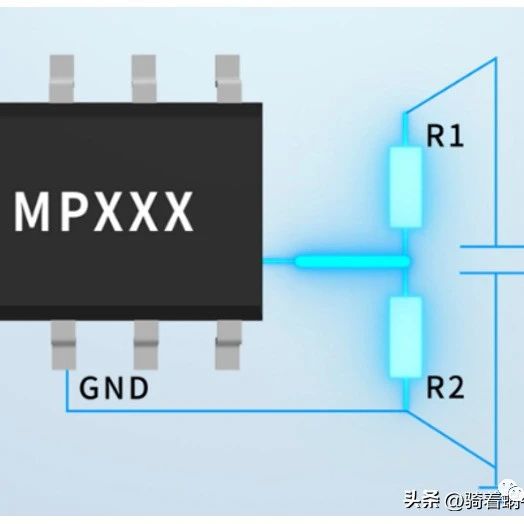

在 DC/DC 变换器中,反馈 (FB) 分压电阻的规格常给设计人员带来各种设计挑战,例如如何确定所需的电阻或调节参数(如输出电压、上分压电阻或下分压电阻)。 图 1 显示了 FB 上/下分压电阻的各种幅度组合。图 1:FB 上/下分压电阻的各种幅度组合本文将探讨 FB 分压电阻的设计规范,包括待机

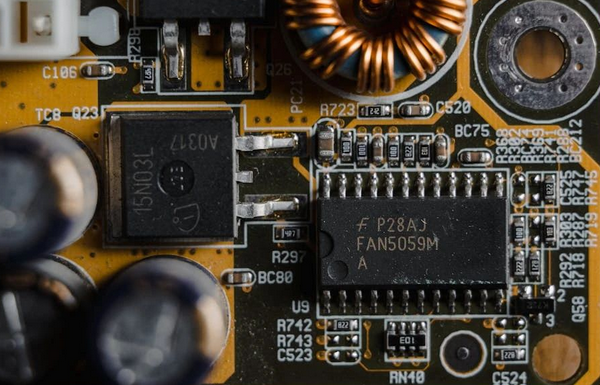

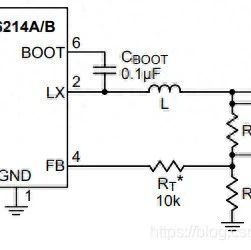

如下图为典型的dcdc电路:芯片是台湾省立琦科技的。上图为dcdc典型应用电路,CIN为输入滤波电容,CBOOT是上管驱动“自举”电容,L是储能电感,R1和R2是反馈电阻,CFF是前馈电容,COUT是输出滤波电容,RT是内部运放补偿器件。一、理论分析没有前馈电容如果没有前馈电容,内部补偿DC-DC转

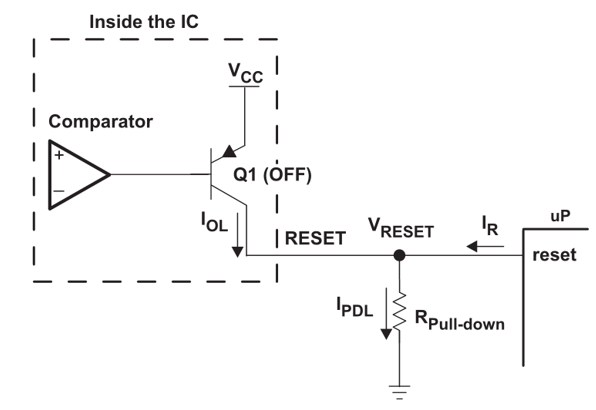

集成芯片的数字输出引脚分为开漏(OD, Open Drain)和推挽(Push-Pull)结构。开漏结构可以进行并联实现或逻辑,在后级芯片识别逻辑与本身耐压范围内可以拉到系统的任何电压,使用十分灵活。芯片上常见的OD结构输出常见于dcdc芯片的PG(Power Good)和 LB

【摘要】某产品研发阶段在做四角实验的过程中,发现单板在低温下出现反复重启动的问题,经过反复的实验和定位,发现是核电源DC-DC芯片使用的液态电解电容,在低温下,内部液体固化。导致电容ESR降低,进而使DC-DC输出的纹波变大,出现单板反复重启动的问题。一、问题的提出该产品是一款有线通信设备,CPU为

扫码关注

扫码关注