- 全部

- 默认排序

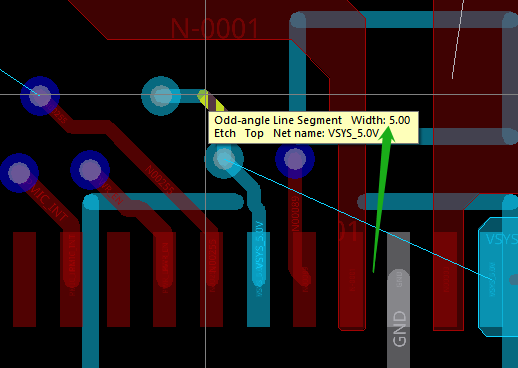

此处不满足载流,后期自己加粗一下线宽或者铺铜处理2.反馈线宽尽量保持一致,加粗到10mil3.存在开路,后期自己处理一下电源和地的飞线电感下面尽量不要放置器件注意不要重复打孔,打孔尽量对齐处理以上评审报告来源于凡亿教育90天高速PCB特训班

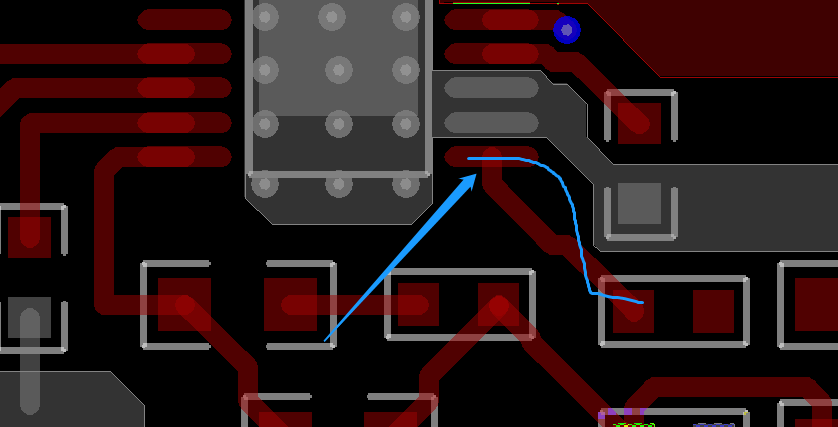

焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊2.走线尽量不要走直角,建议45度3.铺铜注意层的问题,器件在top层,铜皮在bottom层4.模块复用后铜皮变静态铜皮,需要自己调整成动态铜皮,后期自己处理一下5.采用单点接

许多电子工程师会选择Cadence allegro来设计PCB,在使用时会遇到许多操作,其中之一是在Cadence环境中创建封装库,确保数据的高效与准确,那么在操作Cadence时需要注意什么?1、精确测量与缩放Pad尺寸根据Pin脚的精确

基于最新的 allegro X 23.11 版本更新,我们将通过实例讲解、视频演示让您深入了解 allegro X System Capture、allegro X PCB Designer、allegro X Pulse 产品的新功能及用法,助力您提升设计质量和设计效率。allegro X PCB

随着工艺技术不断发展,芯片规模及复杂度翻倍增长,验证对芯片设计的重要性不言而喻,因为在芯片开发过程中,直接流片的成本让人望而却步。因此,工程师及厂商必须在流片前对芯片设计进行“原型验证”——就是模仿真实软件应用条件下的芯片和系统表现是否满足

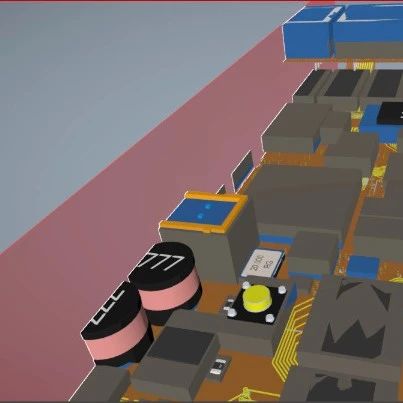

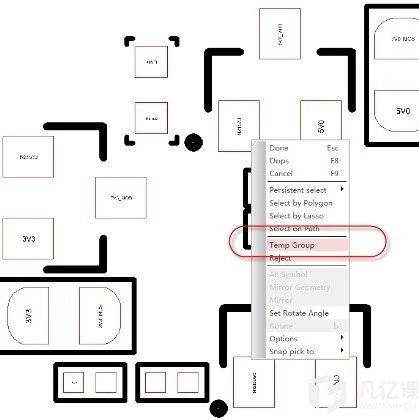

复用模块(Reuse Module)是布局中可以重复应用的部分,可以应用在相同的设计上,也可以应用在存在类似电路的不同设计上。 非正式的模块可以透过place replicate命令生成,以便快速应用于模块复用的电路设计中。正式的模块通常与电路的电路图相关联,以便在放置过程中加以利用。为了方便在其它

01什么是Temp Group?所谓的Temp Group,就相当于临时创建的Group组,用于很多元素的选择,用于一起执行某项命令,比如移动、复制等等。执行完命令之后呢,Group组就打散了,不存在了,今天我们以移动命令为例,讲解一下如何使用Temp Group功能。第一步执行移动命令,Edit-

电子工程师刚开始接触DDR4存储器时,线路板密密麻麻的,动辄DDR2/3/4的,专业术语层出不穷的,很容易看晕。而且随着DDR产品的迭代更新,存储器项目的设计复杂度翻倍增长。同时,DDR产品的设计难度很高,因为它涉及到高速数字电路和复杂的时

全球分布的设计团队越来越多,使缩短设计周期的难题雪上加霜。人工处理多用户问题的权宜措施非常耗时、缓慢并且容易出错。在PCB设计过程中遇到比较复杂的设计时候,通常需要我们进行协同设计,协同设计分为主设计者这以及从设计者,采用的是allegro软件自带的Team Design功能,Team Design

allegro半自动出换pin表SKILL小程序1、 程序的加载a) 在命令窗口敲入skill loadi("MHY_AutoShow_sortedNetName.ile")b) 或在allegro.ilinit 中增加一行 loadi("

扫码关注

扫码关注