- 全部

- 默认排序

StraTIx V是业内第一款可提供精度可变DSP模块的FPGA,这使得它可提供业内效率最高、性能最好的多精度DSP数据通路和功能,如FFT、FIR和浮点 DSP。StraTIx V FPGA的主要性能突破包括:集成66个28Gbps串行收

StraTIx V FPGA具有1.6 Tbps串行交换能力,采用各种创新技术和前沿28-nm工艺,突破带宽瓶颈,降低了宽带应用的成本和功耗。StraTIx V FPGA的主要性能突破包括:集成66个28Gbps串行收发器(每通道功耗仅20

StraTIx V系列FPGA采用新的存储器体系结构,降低延时,高效实现FPGA业界最好的系统性能。StraTIx V FPGA为网络设备生产商提供存储器接口解决方案,支持在互联网上迅速有效的传送视频、语音和数据。StraTIx V FPG

生成式人工智能(GeneraTIve AArTIficial Intelligence,简称生成式AI)是一种人工智能技术,旨在通过复杂的算法、模型和规则,从大规模数据集中学习,并生成新的学习内容,它不仅可处理分析数据,也能创造文本、图片、

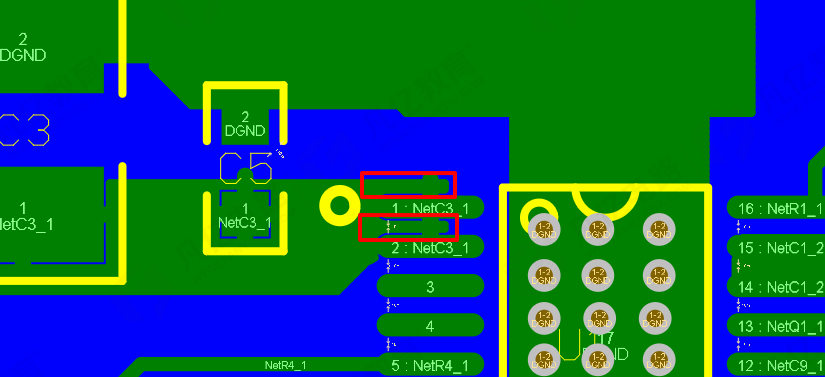

电源主输入注意加宽载流相邻电路大电感应朝不同方向垂直放置养成好习惯焊盘出线应避免从长边出线铺铜尽量避免直角以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.

布线未完成,多处开路、天线报错过孔应错开打孔保持一定间距过孔盖油处理过孔应打到最后一个器件后方下方是电源主输出,应铺铜加宽载流,上方是反馈信号走线加宽到10mil即可电源输入电容, 应在底层铺铜打孔连接到电容在加宽连接到管脚以上评审报告来源

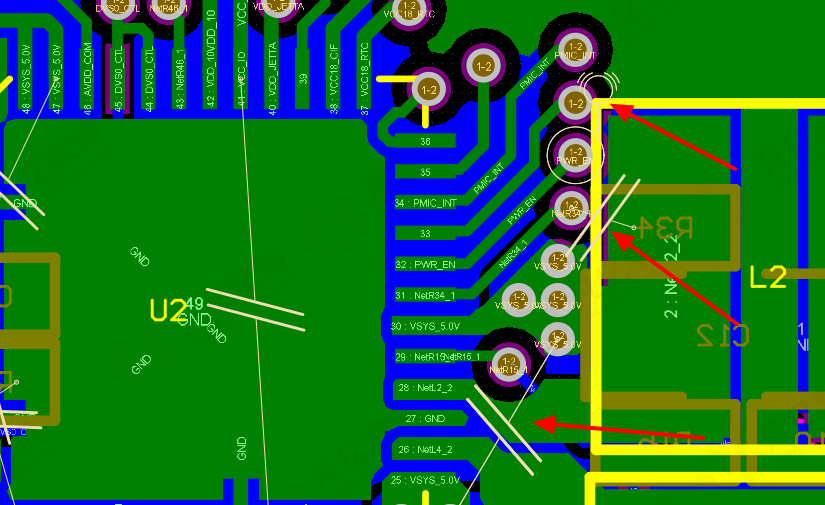

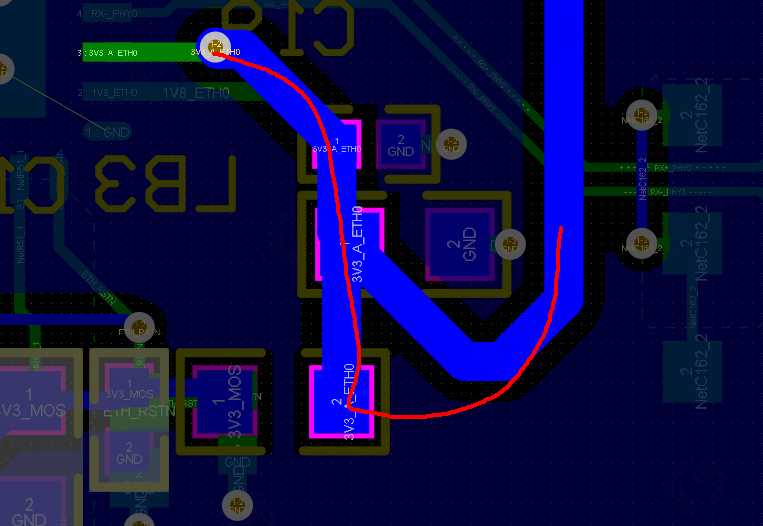

电源输入按照原理图顺序从第一个器件连接时钟信号走线包地打孔处理信号线保持3w间距要求等长绕线从引起不等长端绕线差分走线尽量耦合,减少不必要绕线以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码

MSP430单片机是美国德州仪器(TI)自1996年开始推向市场的单片机,是一种16位超低功耗,具有精简指令集(RISC)的混合信号处理器,但相比51、STM32等单片机,许多小白对MSP430单片机了解不深,所以下面将对MSP430单片机

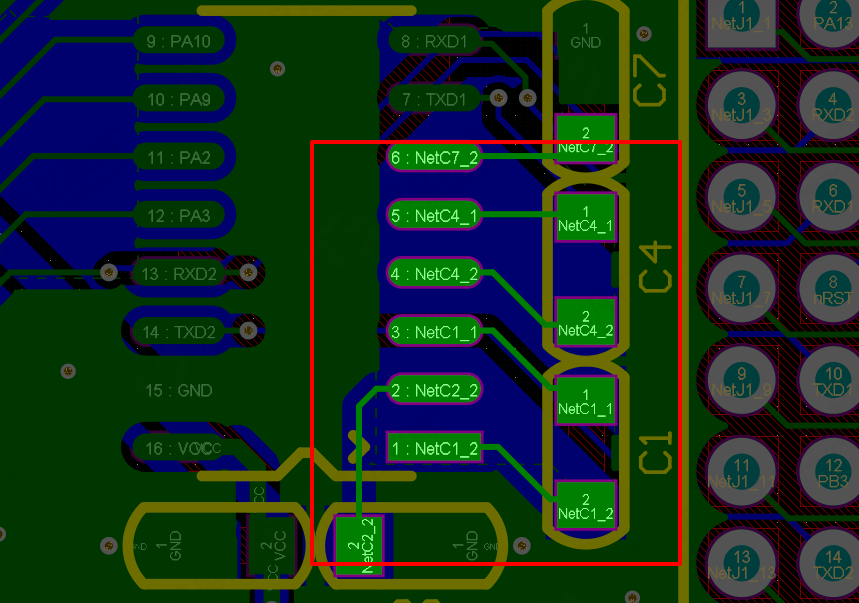

232模块c+-、v+-所接升压电容,走线需要加粗到10mil以上晶振包地打孔处理usb差分尽量走一层,换层长度不要太长器件布局太近相互干涉,大器件到小器件间应最少隔开1.5mm以上电源加宽载流,走线加宽或铺铜走线不完全连接,走线应连接到焊

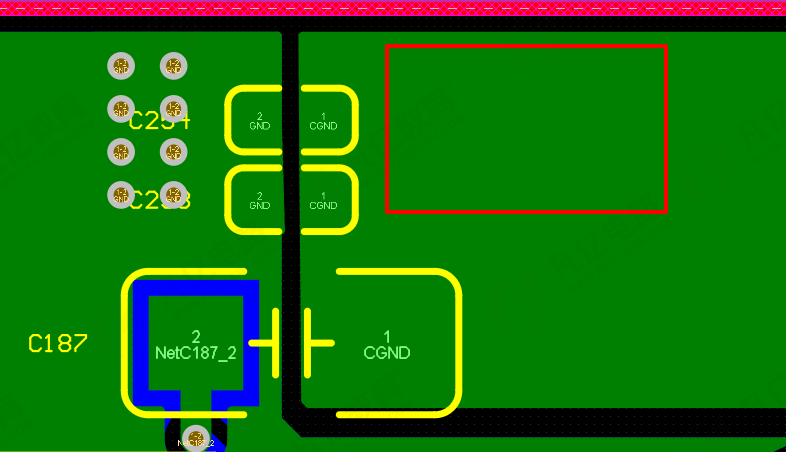

地网络跨接处两边都要多打过孔两个地隔离2mm以上间距焊盘应从短边出线,避免从四角和长边出线存在短路报错未处理以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item

扫码关注

扫码关注