- 全部

- 默认排序

答:1)需要塞孔的过孔在正反面都不做阻焊开窗;2)需要过波峰焊的PCB板卡,BGA下面的过孔都需要做塞孔处理、不开窗;3)BGA器件的pinTCh间距≤1.0mm,BGA下面的过孔都需要做塞孔处理、不开窗;4)BGA器件加的ICT测试点,测试焊盘直径32mil,阻焊开窗37mil。

答:orcad系统自带的原理图库的路径是(16.6版本)C:\Cadence\SPB_16.6\tools\capture\library,在路径下,后缀为olb的文件就是,每一个库所包含的器件如下:AMPLIFIER.OLB 共182个零件,存放模拟放大器IC,如CA3280,TL027C,EL4093;ARITHMETIC.OLB 共182个零件,存放逻辑运算IC,如TC4032B,74LS85等;ATOD.OLB 共618个零件,存放A/D转换IC,如A

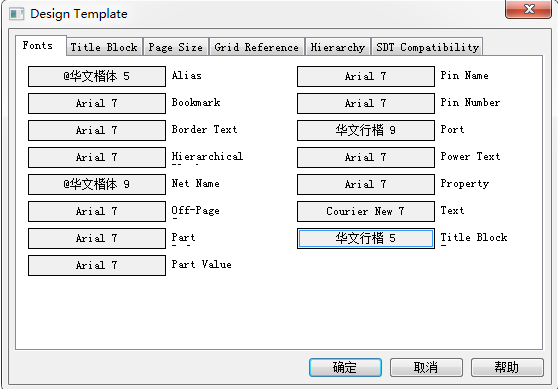

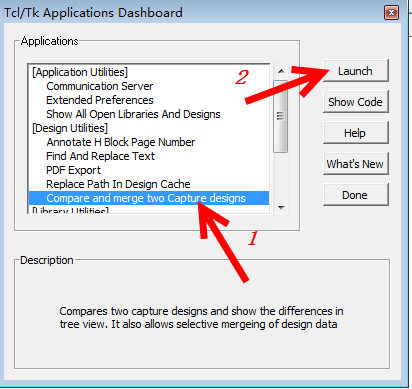

答:在电子设计中, 电路图的修改是非常频繁的,改动的多了,有时候会出现要改回去的情况,所以有时就会需要对两份原理图进行差分化的对比,操作步骤如下:第一步,首先,我们对一份原理图进行修改,修改一点点内容,做为测试之用,如图3-123与图3-124所示,方便后期查找; 图3-123 修改后的原理图示意 图3-124 修改前的原理图示意第二步,我们打开其中的任意一份原理图,选中原理图的根目录,然后执行菜单命令Accessories-Cadence TCL/Tk Utilities命

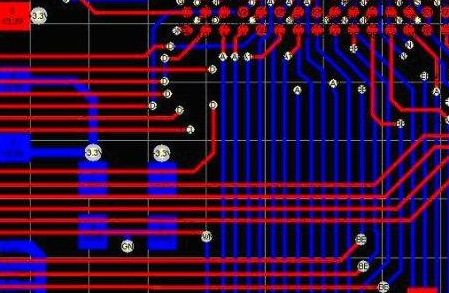

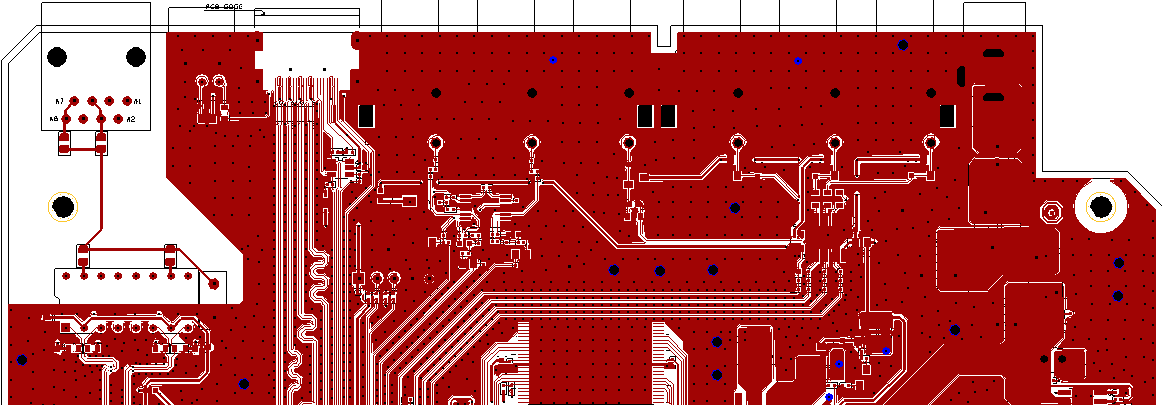

答:我们在使用Allegro软件进行PCB设计时,铺的铜皮都是动态或者是静态的铜皮,当打开ETCh的时候,所有的走线跟铜皮都是同时显示的,如图5-130所示,在Allegro软件中是否可以隐藏铜皮呢,只显示走线呢,答案是可以的,具体操作如下:

答:在Allegro软件中,所铺的铜皮全部都是动态铜皮,在进行ETCh显示的时候,包括走线、铜皮都会显示,在前面的问答中我们讲解了如何将铜皮全隐藏不显示,但是,这样不方便走线设计,走线时不清楚哪一块有铜皮,这里我们讲解一下,如何设置铜皮不显示,但是在PCB中还是显示铜皮的边框,具体操作如下所示:

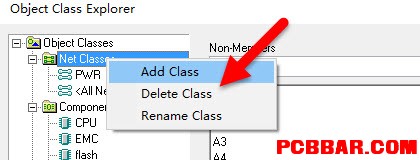

答:我们在Allegro中进行设计的时候,总会遇到这样的问题,创建类的时候,可供选择的选项太多,这里我们对这些不同的类做一个说明:

职位描述: 软件工程师 ,理工类本科学历,自动化/机电一体专业,男性。1、2年以上自动化产品、设备软件开发相关工作经验。英文能读写,语言表达清晰;2、能够运用C/汇编制作软件、熟练操作相关开发软件,如KEIL、C++、VC等,熟悉USB、TCIP、DMX、RDM、CAN等通讯协议;3、常用办公软件OFFICE、CAD、CRD;熟悉单片机原理和相关MCU基本知识。可以自行绘制PCB、能够根据软件判断和解决系统问题。

谈谈阻抗匹配的理解

阻抗匹配(impedance maTChing)信号源内阻与所接传输线的特性阻抗大小相等且相位相同,或传输线的特性阻抗与所接负载阻抗的大小相等且相位相同,分别称为传输线的输入端或输出端处于阻抗匹配状态,简称为阻抗匹配。否则,便称为阻抗失配。有时也直接叫做匹配或失配。

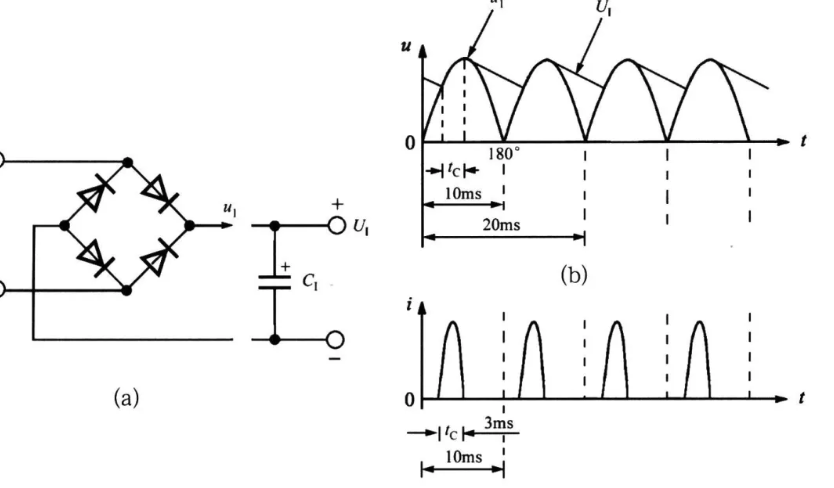

50Hz交流电压经过全波整流后变成脉动直流电压u1,再通过输入滤波电容得到直流高压U1。在理想情况下,整流桥的导通角本应为180°(导通范围是从 0°~180°),但由于滤波电容器C的作用,仅在接近交流峰值电压处的很短时间内,才有输入电流流经过整流桥对C充电。50Hz交流电的半周期为 10ms,整流桥的导通时间TC≈3ms,其导通角仅为54°(导通范围是36°~90°)。因此,整流桥实际通过的是窄脉冲电流。桥式整流滤波电路的原 理如图1(a)所示,整流滤波电压及整流电流的波形分别如图l(b)和(

扫码关注

扫码关注