- 全部

- 默认排序

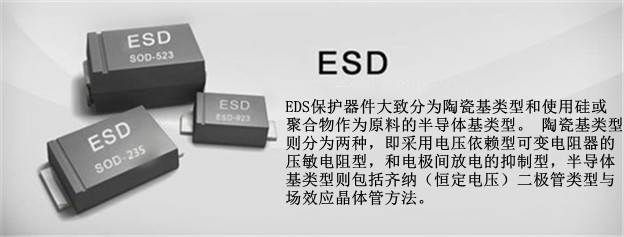

在集成电路中,若电子系统正常工作,ESD器件的作用几乎忽略不计,但当外部接口电压超过ESD器件的击穿电压时,ESD器件将开始起作用,起到很大的作用,它可将电流分流到地,保护后级敏感电子元件免受静电损坏。当然,可能很多小白不清楚,所以下面细说

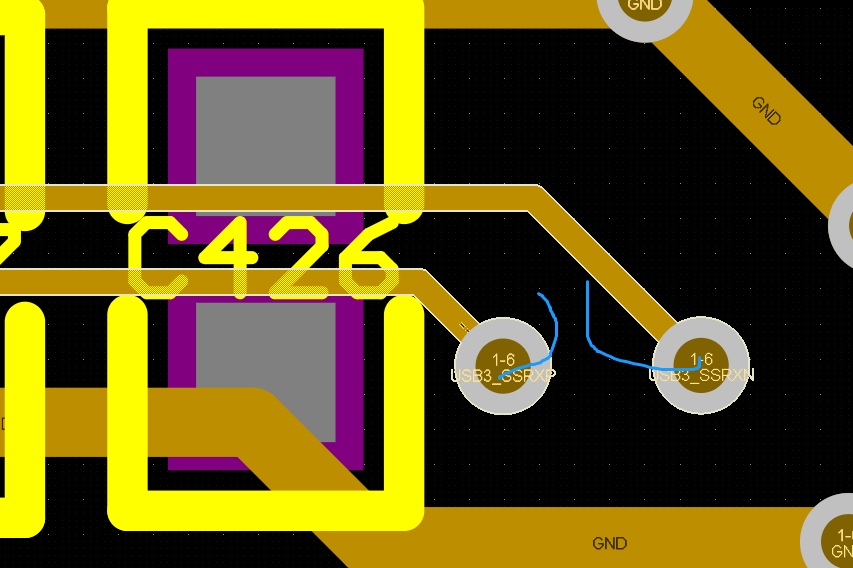

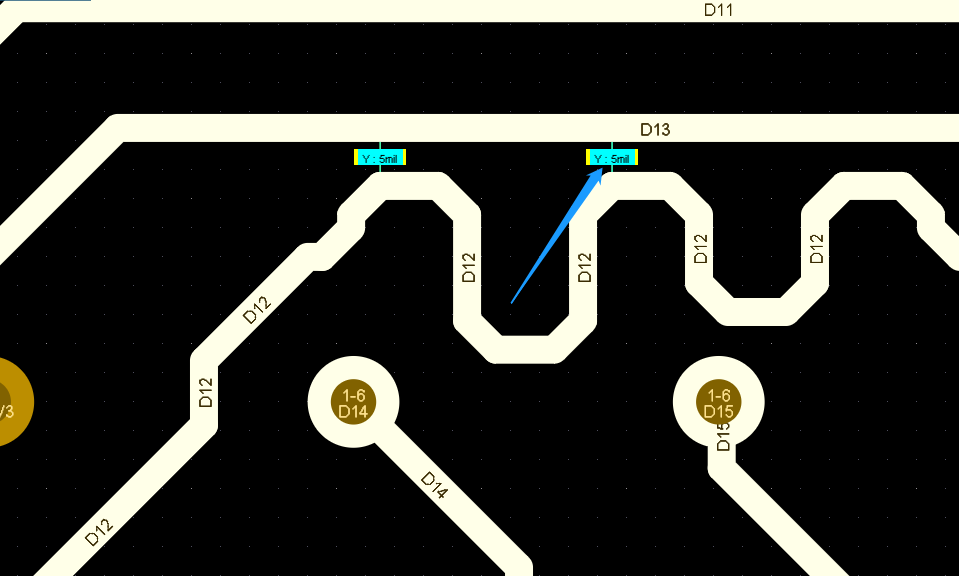

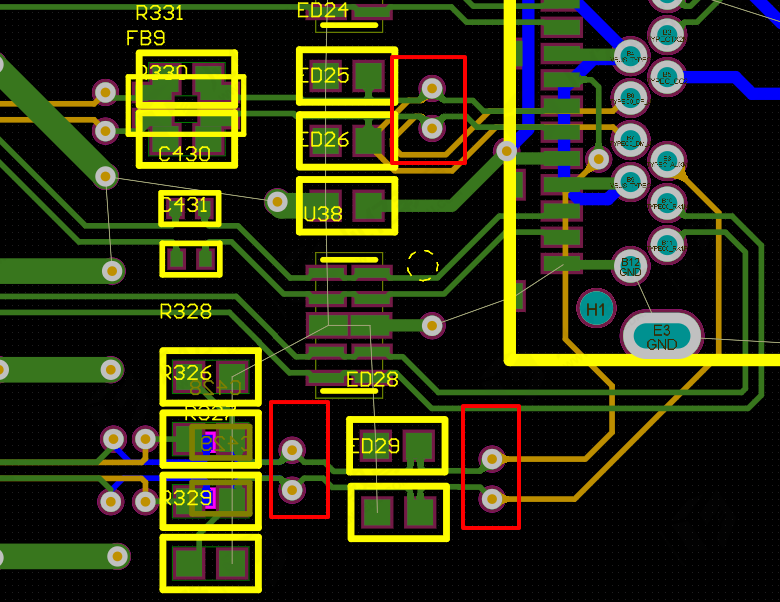

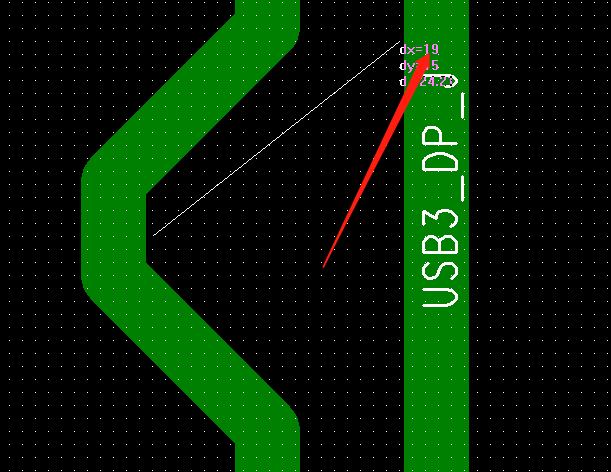

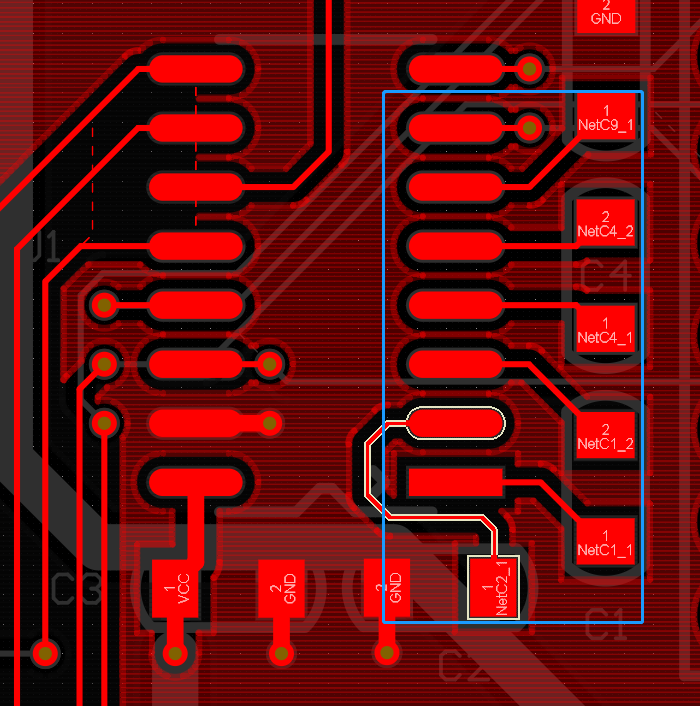

差分走线注意出线耦合2.注意焊盘出线规范3.差分对内等长不规范,锯齿状等长,凸起高度不能超过线距的两倍4.注意打孔要打在ESD器件前面,先经过ESD器件5.器件摆放不要挡住1脚标识6.USB差分需要进行对内等长,误差5milUSB2.0电源

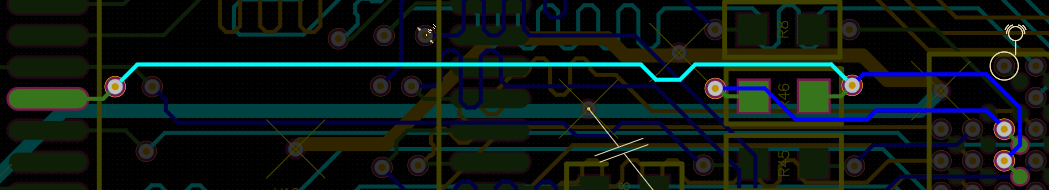

时钟等长错误,按下方正确等长方法等长多处电源和地焊盘没有打孔导致开路地址线等长误差太大,地址线等长误差-+100mil电源没有连接,电源扇孔走线没有加粗以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问

注意数据线等长需要满足3W规则2.地址线之间等长也需要满足3W规则3.注意数据线扇孔线宽尽量保持一致4.地址线等长存在误差报错5.等长组创建有问题,有很多网络没有添加到里面,后期自己重新创建一下6.注意走线不要有直角和尖角,尽量钝角7.注意

差分换层需要在旁边200mil范围内打回流地过孔电源走线注意加粗usb座子到eSD器件之间也需要建立差分对,对内误差控制5mil等长差分对内等长不符合规范差分对内等长误差超过5mil负片没有指定网路多处孤岛铜皮、尖岬铜皮以上评审报告来源于凡

在电子工程中,集成电路(IC)已成为不可或缺的核心组件,然而,你知道吗,集成电路的隐形杀手是什么?是静电,无法消除,很容易对集成电路构成严重威胁,本文将深入剖析静电对集成电路的危害,分析下为什么要预防静电。首先,静电积累过多很容易对集成电路

1注意差分对内等长凸起高度不能超过线距的两倍2.差分出线要尽量耦合,后期自己调整一下3.此处线宽不满足载流,后期自己加粗一下线宽或者铺铜处理4.CC1和CC2属于重要信号,走线需要加粗处理5.ESD器件要靠近关键摆放,先经ESD器件在到座子

GitHub 镜像访问GitHub文件加速Github 加速下载加速你的 Github谷歌浏览器 GitHub 加速插件(推荐)GitHub raw 加速GitHub JSDelivr通过 Gitee 中转 fork 仓库下载通过修改 HOSTS 文件进行加速为什么 github 下载速度这么慢

1、ESD224DQARTVS ESD保护二极管阵列ESD224二极管是双向阵列,设计用于高速应用,如USB 3.0和HDMI 2.0。ESD224的额定ESD冲击消散值为IEC61000-4-2国际标准中规定的最高水平(4级)。ESD22

RS232的升压电容走线需要加粗处理2.USB差分对内等长误差5mil3.注意焊盘出线规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊4.注意电池供电,走线需要加粗处理,满足载流5.SD卡数据线误差尽量控制300mil6.晶振尽量包地

扫码关注

扫码关注