- 全部

- 默认排序

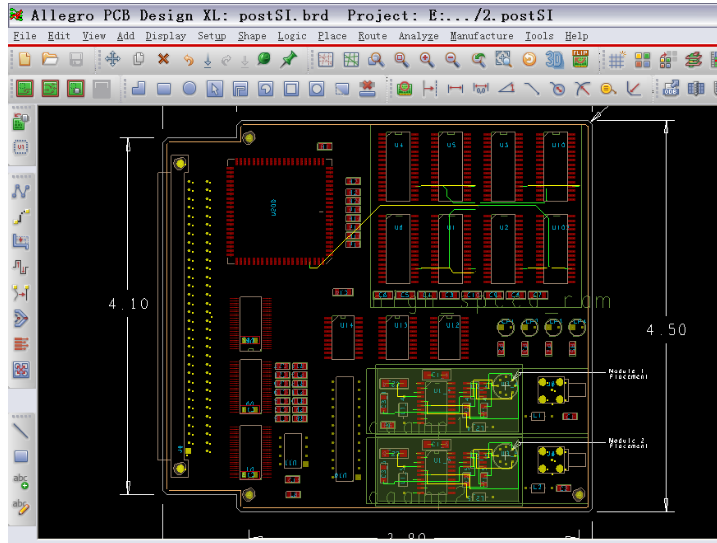

高速高密度多层PCB板的SI/EMC(信号完整性/电磁兼容)问题长久以来一直是设计者所面对的最大挑战。然而,随着主流的MCU、DSP和处理器大多工作在100MHz以上(有些甚至工作于GHz级以上),以及越来越多的高速I/O埠和RF前端也都工作在GHz级以上,再加上应用系统的小型化趋势导致的PCB空间缩小问题,使得目前的高速高密度PCB板设计已经变得越来越普遍。许多产业分析师指出,在进入21世纪以后,80%以上的多层PCB设计都将会针对高速电路。

高清晰度多媒体接口(英文:High Definition Multimedia InteRFace,HDMI)是一种数字化视频/音频接口技术,是适合影像传输的专用型数字化接口,其可同时传送音频和影像信号,最高数据传输速度为4.5GB/s,时无需在信号传送前进行数/模或者模/数转换。

PADS经历过哪些历史版本,下面跟pads教程小编一起来了解一下:1986年:PADS PCB,DOS操作系统;1989年:PADS Logic,DOS操作系统;1990年:PADS 2000,DOS操作系统;1993年:PADS PeRForm,DOS和Windows操作系统;1995年:PowerPCB V1.0,Windows 95操作系统;1997年:PowerPCB V2.0,WindowsNT操作系统;1998年:PowerPCB V3.0,Windows 98操

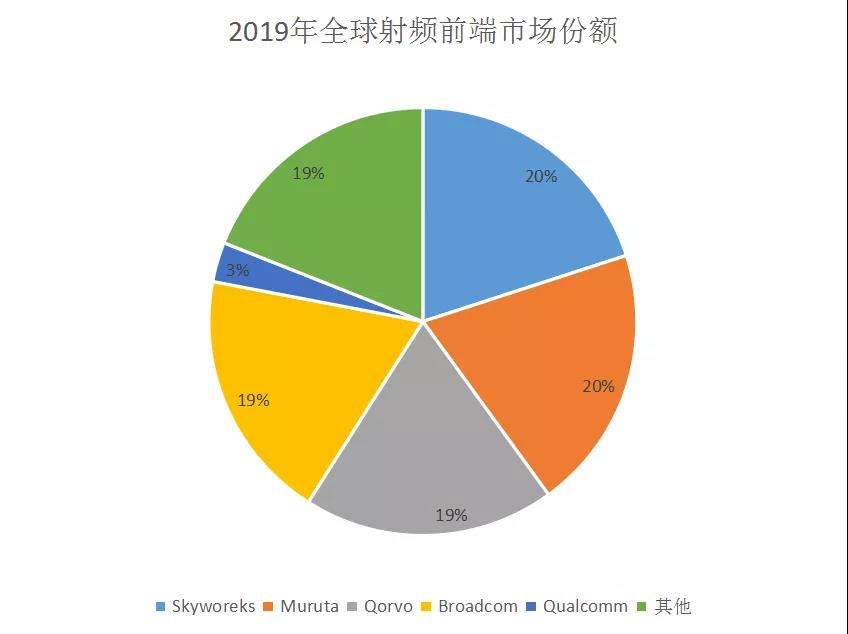

射频前端(RFFE)作为模拟芯片这顶皇冠上的“明珠”,如今随着5G技术的全面铺开,全球的市场格局正在发生悄然变化。据高通数据统计预测,三年内5G射频前端市场复合增长率为12%,规模将达到180亿美。

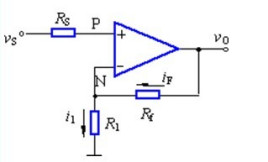

同相比例运算电路的认识?

同相输入放大电路如图1所示,根据“虚短”与“虚断”,信号电压通过电阻Rs加到运放的同相输入端,输出电压vo通过电阻R1和RF反馈到运放的反相输入端,构成电压串联负反馈放大电路。

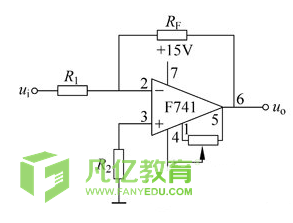

反向比例运算电路的认识

在反相比例运算电路中,电路输入信号ui总是经过一个电阻R1接到反相输入端,输出信号uo经过一个电阻RF反馈到反相输入端,如图1(a)所示。由图可见,图中电路是一个用国产芯片F741接成的反相比例运算电路,图中同时给出了电源连接及调零电路,并在同相输入端对地串了一个电阻R2=R1//RF,目的是使两个输入端对地的等效电阻相同。 (a)用F741接成的反相比例运算电路 (b)反相比例运算电路的简化图对于图1(b),由于理想运放的经输入电流为零,所以ip=in=0,由于运放的同相和

LDO应用要点

(1) VRF滤波由LDO的工作原理可知,Vref(基准电压)的稳定性与LDO输出电源的纹波及噪声密切相关。为了减小器件面积,某些LDO在片内不提供对VREF引脚的滤波。在这种情下,设计者需在VREF引脚附近添加10uF电容,以保证VREF的低噪声和低纹波(2) SENSE(感应)引脚的处理SENSE引脚是LDO、DCDC电源芯片上常见的引脚在PCB上,当电源输出端与负载端相距较远时,输出电源Vout需通过较长距离的PCB导线(或PCB铜皮)才能加载到负载上,由于负载电流流经

答:SMT是SuRFace Mount Technology的缩写,是表面组装技术,是目前电子组装行业里最流行的的一种技术和工艺,是一种无需在印制板上钻插装孔,直接将表面组装元器件贴、焊到印制电路板表面规定位置上的电路装联技术。表面组装技术,就是用一定的工具,将表面组装元器件引脚对准预先涂覆了粘剂和锡膏的焊盘图形上,把表面组装元器件贴装到PCB表面上,然后经过波峰焊或者是回流焊,使得表面组装元器件和电路之间建立可靠的机械与电气连接。SMD是SuRFace Mounted Devices的缩写,是

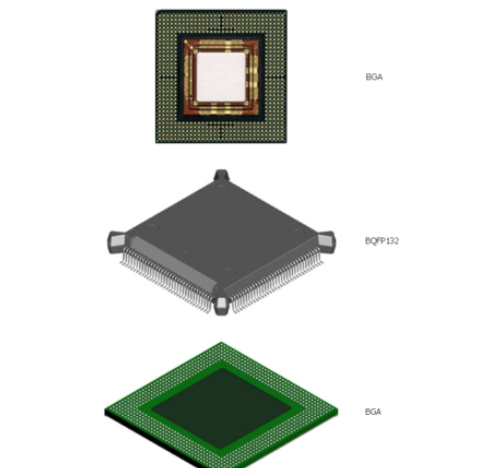

答:PCB封装就是把实际的电子元器件,芯片等的各种参数(比如元器件的大小,长宽,直插,贴片,焊盘的大小,管脚的长宽,管脚的间距等)用图形方式表现出来,以便可以在画pcb图时进行调用。1)PCB封装按照安装方式来区分的话,可以分为贴装器件、插装器件、混装器件(贴装和插装同时存在)、特殊器件。特殊器件一般指沉板器件。2)PCB封装按照功能以及器件外形来区分的话,可以分为以下种类:SMD: SuRFace Mount Devices/表面贴装元件。RA:

答:在将网表导入到PCB的过程中,经常会出现封装内管脚名或者数目与原理图内的器件管脚不一致,从而导致导入过程中报错,如图4-90所示: 图4-90 导入网表提示解析示意图上图是一个比较典型的封装中管脚与原理图中不一致而出现的报错内容。从上示报错内容(红色框标识的内容)可以获取以下信息点:Ø 器件的封装名为ERF8-40。Ø 封装中有几个多余的管脚,管脚名为41、42、43、44、45、46、47、48。Ø 封装中缺少了几个管脚,管脚名为H1、H

扫码关注

扫码关注