- 全部

- 默认排序

在开始新设计时,因为将大部分时间都花在了电路设计和元件的选择上,在PCB布局布线阶段往往会因为经验不足,考虑不够周全。如果没有为PCB布局布线阶段的设计提供充足的时间和精力,可能会导致设计从数字领域转化为物理现实的时候,在制造阶段出现问题,或者在功能方面产生缺陷。那么设计一个在纸上和物理形式上都真实可靠的电路板的关键是什么?让我们探讨设计一个可制造,功能可靠的PCB时需要了解的前5个PCB设计指南。

原来当我在研究实验室工作并为我们的电喷控制系统设计PCB时,我的布局很糟糕。因为当时我们并不担心外包装机箱,以及有限的电路板空间或必须紧凑的布线等小问题。只要我们能够将所有必需的元器件放在电路板上并最终将电路板实现成为物理印刷电路,我们就已经很满足了。

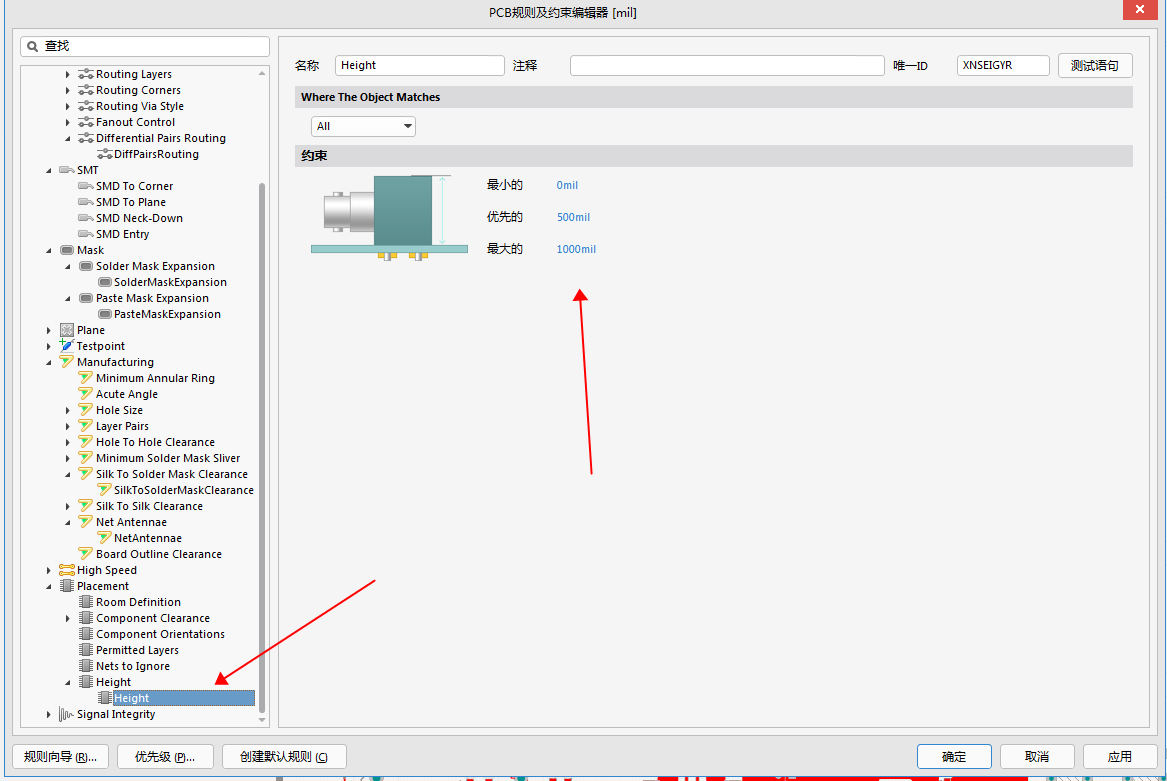

因为考虑到PCB布局存在限高要求,这种情况需对高度等进行例行检查,元件高度检查需要元件封装设置好高度信息,设置好高度检查规则及适配范围(全局还是局部),并勾选高度检查。

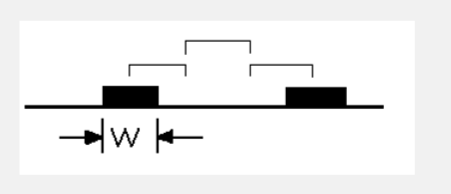

答:为了信号走线的质量,不产生串扰,我们保持信号走线与信号走线之间的间距为3倍线宽,这个间距指的是走线的中心到中心的间距,因为我们的线宽英文是width,所以这个规则我们通常就叫做3W原则。当我们的走线的中心间距不少于3倍线宽时,可以保证70%的线间电场不互相干扰,如果信号需要达到98%的线间电场不互相干扰,可以使用10W规则。3W原则是一种设计者无须其他设计技术就可以遵守PCB布局的原则。但这种设计方法占用了很多面积,可能会使布线更加困难。使用3W原则的基本出发点是使走线间的耦合最小。这种原则

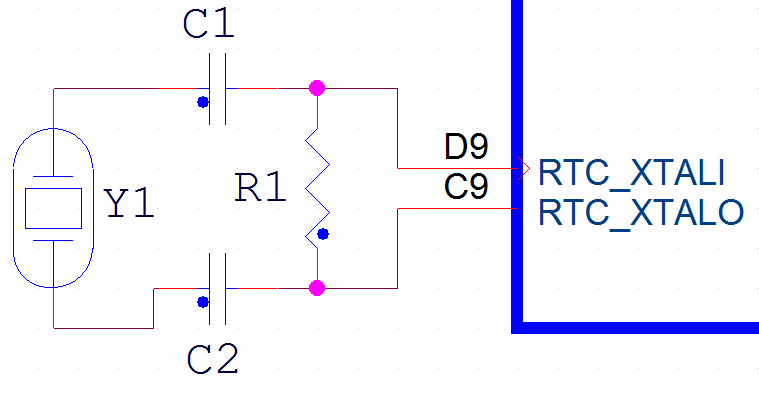

PCB设计中晶体的π型滤波应该怎么设计?答:在晶体的电路设计中一般都采用π型滤波来进行设计,原理图设计部分如图1-41所示,后期我们在进行PCB布局布线的时候,要注意以下几点:布局整体紧凑,一般放置在主控的同一侧,靠近主控IC,尽量不要靠近板边;布局是尽量使电容分支要短,目的是为了减小寄生电容;晶振电路一般采用π型滤波形式,放置在晶振的前面;晶体和晶振的布局要注意远离大功率的元器件、散热器等发热的器件。其原理图设计部分如图1-41所示。 图1-41 晶体π型滤波电路示意图其PCB设计部

扫码关注

扫码关注