- 全部

- 默认排序

一、输入失调电压(Offset VoLtage,VOS) (一)定义:在运放开环使用时, 加载在两个输入端之间的直流电压使得放大器直流输出电压为 0。 (二)优劣范围:1µV 以下,属于极优秀的。100µV 以下的属于较好的。最大的有几十mV。 (三)对策: 1)选择 VOS远小于被测直流量的放大器, 2)过运放的调零措施消除这个影响 3)如果你仅关心被测信号中的交变成分,你可以在输入端和输出端增加交流耦合电路,将其消除。 4)如果 IB1=IB2,那么选择 R1=R2//RF,可

一、输入失调电压(Offset VoLtage,VOS) (一)定义:在运放开环使用时, 加载在两个输入端之间的直流电压使得放大器直流输出电压为 0。 (二)优劣范围:1µV 以下,属于极优秀的。100µV 以下的属于较好的。最大的有几十mV。 (三)对策: 1)选择 VOS远小于被测直流量的放大器, 2)过运放的调零措施消除这个影响 3)如果你仅关心被测信号中的交变成分,你可以在输入端和输出端增加交流耦合电路,将其消除。 4)如果 IB1=IB2,那么选择 R1=R2//RF,可

仅看近30年的发展,以PC为代表的行业几度繁荣而后归于平静,从最早的百兆级处理器速度倍频直到今天的几个GHz级别,总线位宽从16位扩展到今天的64位,以InteL为首的行业龙头公司将CPU的处理能力整整提升了成百上千倍。 在总线宽度和处理器速度达到瓶颈后的近10年里,整个行业将突破的战场放在了高速接口上,外部串行高速接口的速率从Gbps迅速飞升到几十个Gbps,为了实现更高的吞吐量,还采用了复杂的高阶调制和增加链路宽度的办法。这一切简直是以“迅雷不及掩耳盗铃之势”汹涌而至,作为“攻城狮”的你做

电子电路仿真软件分析

1、电路仿真软件proteus用得比较多。 2、Proteus 组合了高级原理布图、混合模式SPICE 仿真,PCB 系统特性: 设计以及自动布线来实现一个完整的电子设计系统。 2.Proteus 产品系列也包含了我们革命性的VSM 技术,用户 可以对基于微控制器的设计连同所有的周围电子器件一 起仿真。用户甚至可以实时采用诸如LED/LCD、键盘、 RS232 终端等动态外设模型来对设计进行交互仿真。

最新一代安卓系统安卓N已经出现了,和以往的全新安卓系统一样,尽管新的安卓拥有很多激动人心的新特性,但仍很难勾起人们的兴趣。无它,就因为新的安卓系统,和大部分用户绝然是没什么关系的,不能升级说这个有什么用?尽管安卓来自GoogLe,但GoogLe却似乎管生不管养,手中的机器能不能升级到安卓,还得各家OEM厂商说了算。

硬件设计就是根据产品经理的需求PRS(Product Requirement Specification),在COGS(Cost of Goods SaLe)的要求下,利用目前业界成熟的芯片方案或者技术,在规定时间内完成符合PRS功能(Function),性能(Performance),电源设计(Power SuppLy), 功耗(Power Consumption),散热(ThermaL/CooLing),噪音(Noise),信号完整性(SignaL Integrity), 电磁辐射(EMC/

ALtium Designer的原理图设计导入PCB,存在两种方法:一种是直接导入法,类似于ALLegro的第一方导入;另一种是间接法,即网表对比导入法。

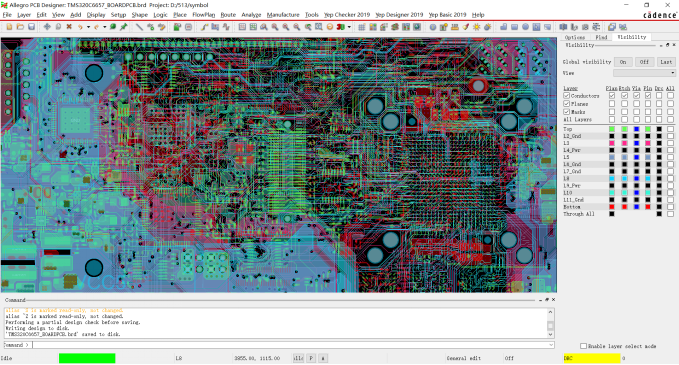

1、 ALLegro的全称是Cadence ALLegro PCB Designer,是Cadence公司推出的一个完整的、高性能印制电路板设计套件。通过顶尖的技术,它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。ALLegro印制电路板设计提高了PCB设计效率和缩短设计周期,让您的产品尽快进入量产(目前高速PCB设计用的最多工具,就是ALLegro)。

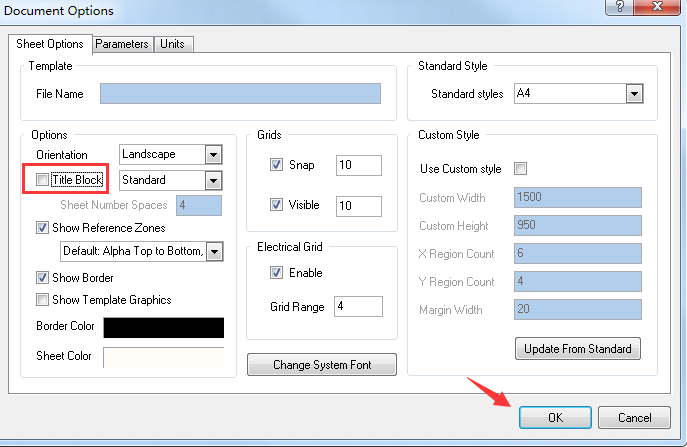

1. 新建个原理图文件。 2. ALtium_Designer9->DocumentOptions,把 TitLe BLock 的选项去掉。3. 将文件保存为“ .SchDot”格式; 4. 使用PLace->Drawing TooLs->Line ,根据自身需要,绘制出如下图所示界面;

扫码关注

扫码关注