- 全部

- 默认排序

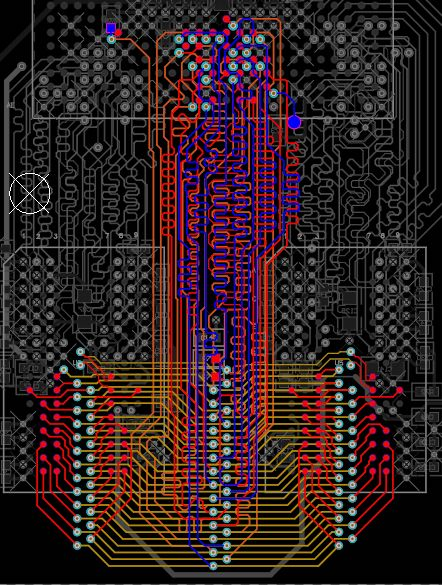

在PCB设计时我们在处理DDR部分的时候都会进行一个拓扑的选择,一般DDR有T点和Fly-by两种拓扑结构,那么这两种拓扑结构的应用场景和区别有哪些呢?T点拓扑结构:CPU出来的信号线经过一个过孔后分别向两边进行连接,分叉点一般在信号的中心

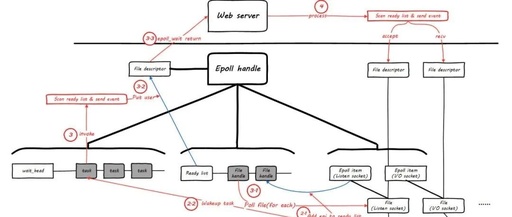

hello, 大家好,我是Alex,今天分享一篇关于socket编程里面经典问题:惊群问题,文章深入分析了惊群问题的现象和其根本原因,并给出一些很好的解决方案,值得我们参考和学习,通过文章,我们可以学习到彻底理解惊群问题epoll底层实现原理epoll的ET和LT区别socket的reuseaDDR

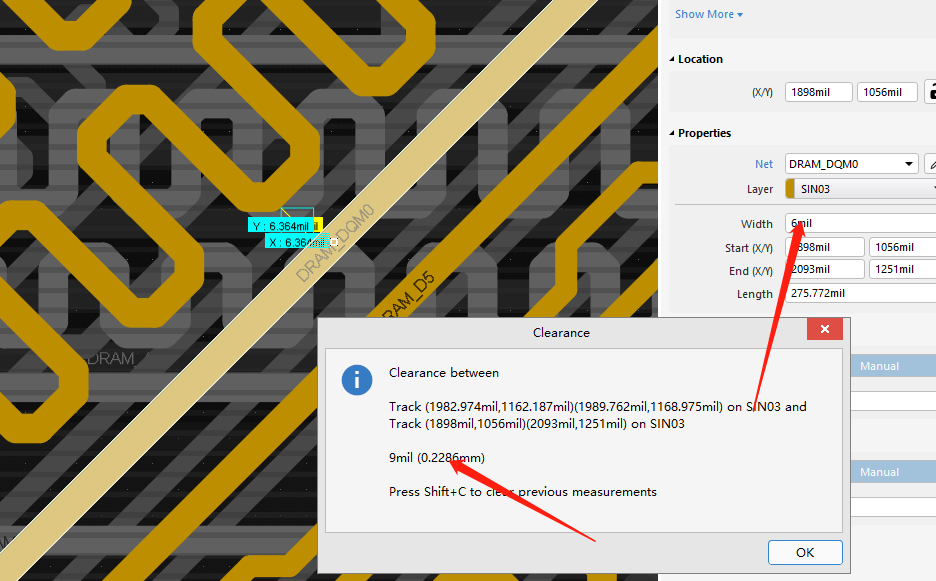

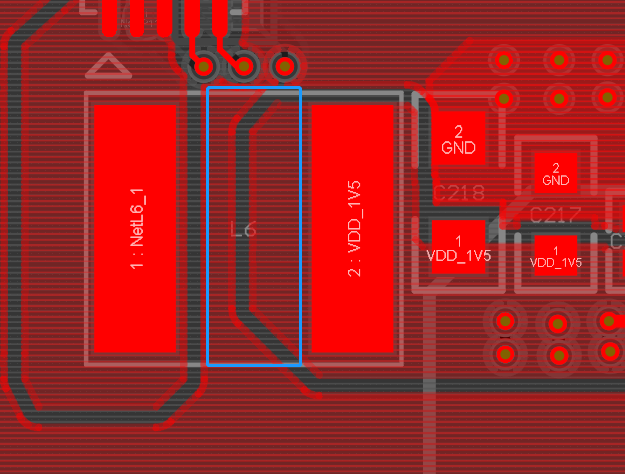

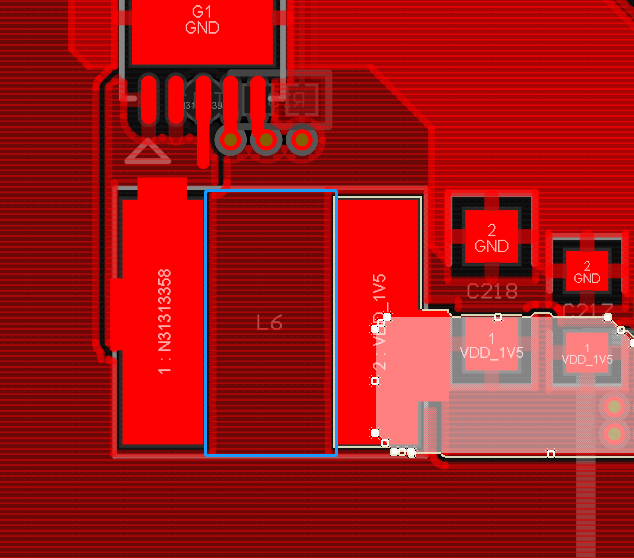

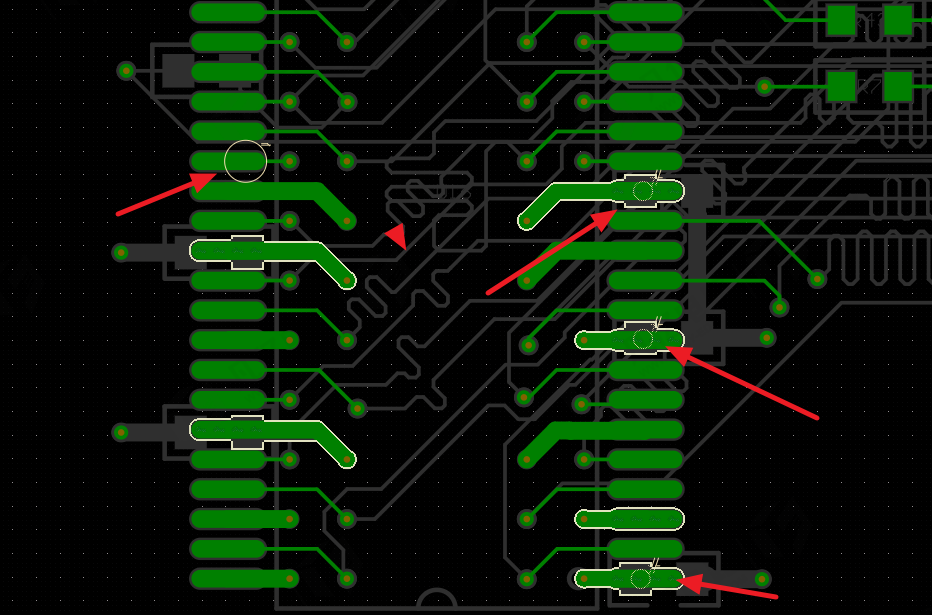

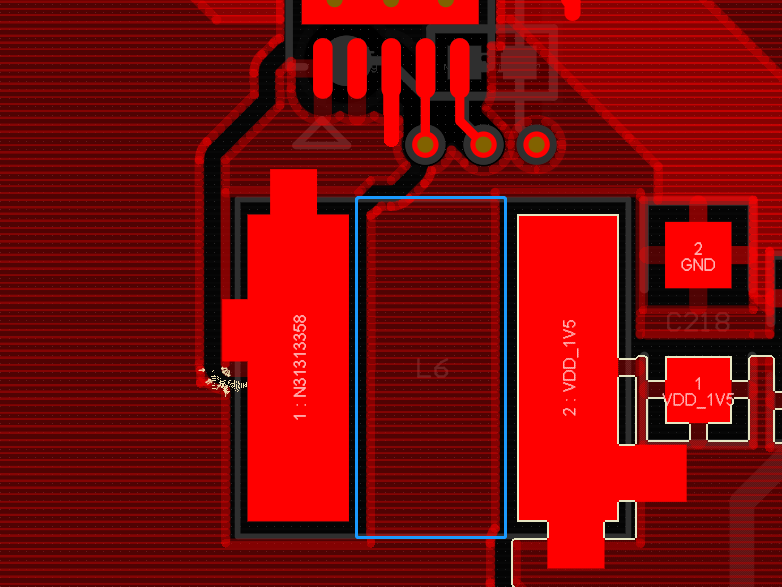

数据线等长需要满足3W规则2.地址线也需要满足3W规则3.差分线处理不当,锯齿状等长,凸起高度不得超过线距的两倍4.电感所在层的内部需要挖空处理5.座子需要放置在板边6.器件摆放不要遮住一脚标识7.注意过孔需要盖油处理10.DDR的VREF

电感所在层内部需要挖空处理2.滤波电容摆放应该先大后小3.差分线处理不当,锯齿状等长,凸起高度不得超过线距的两倍4.数据线等长需要满足3W规则5.地址线也要满足3W规则6.此处不满足载流,VREF电源最少需要加粗到15mil7.此处走线需要

电感所在层的呢恩不需要挖空2.差分线对内等长处理不当,锯齿状等长,凸起高度不得超过线距的两倍3.注意数据线等长需要满足3W规则4.差分出线要尽量耦合5.存在多余的线头6.注意过孔不要上焊盘7.注意器件摆放过近,建议最少1.5mm8.过孔需要

差分线处理不当,锯齿状透气高度不能超过线距的两倍2.注意地址线等长需要满足3W规则3.注意器件摆放不要干涉1脚标识4.器件干涉以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:htt

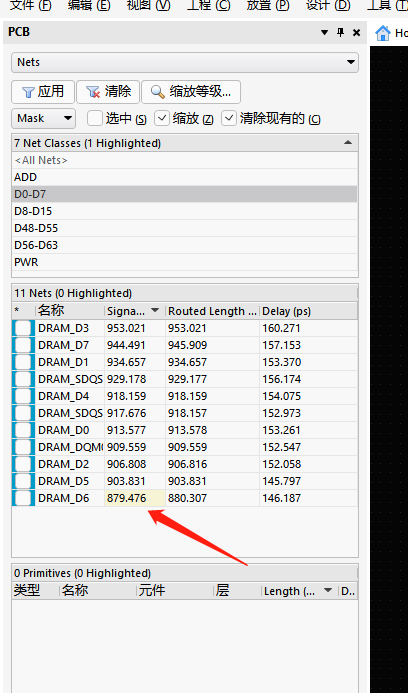

1、存在开路和短路。2、地址线的等长是ic到DDR的长度。3、时钟线布线错误,应该从u16到r46再到u1。4、时钟线等长错误,是SDRAM段到电阻和电阻段ic的线一样长。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PC

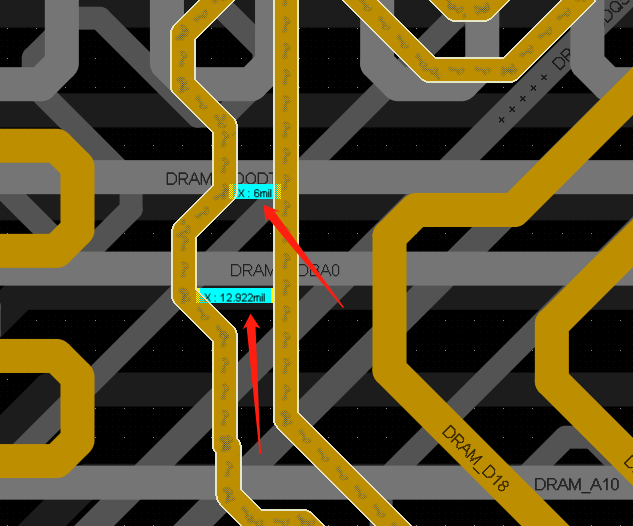

数据线等长存在报错2.走线尽量不要走直角,建议钝角3.此处走线需要优化一下4.走线未连接到过孔中心,存在开路5.此处出线载流瓶颈,自己加宽铜皮6.注意过孔不要上焊盘7.地和电源都需要加粗8.地就近打孔,缩短回流路劲9.差分出线要尽量耦合10

电感所在层的内部需要挖空处理2.差分线处理不当,锯齿状等长不能超过线距的两倍3.走线未连接到过孔中心,存在开路4.VREF的线宽需要加粗到15mil以上5.焊盘需要开窗处理6.器件干涉7.此处出线载流瓶颈,自己加宽一下铜皮以上评审报告来源于

差分线处理不当,锯齿状等长不能超过线距的两倍2.注意地址线之间等长需要,满足3W规则3.差分对内等长不满足误差范围4.走线未连接到过孔中心,存在开路5.滤波电容法放置尽量保证一个管脚一个6.此处不满足载流,建议铺铜处理7.数据线之间等长也需

扫码关注

扫码关注