- 全部

- 默认排序

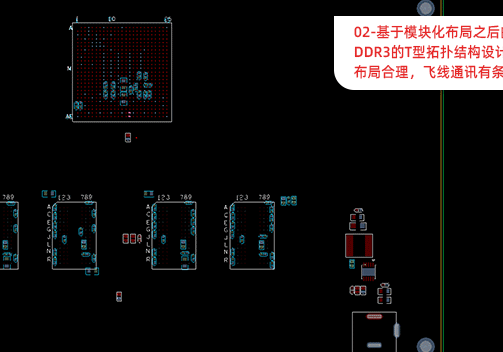

一、PADS8层DDR3 Fly-by拓扑结构视频课程详情本pads视频课程基于飞思卡尔 i.MX6 处理器的 8层PCB设计,重点介绍 DDR3 内存的设计思路,一共四颗 DDR3,采用菊花链(Fly-By)的拓扑结构。讲解了 DDR3 设计的信号 class分组,信号的同组同层布线、信号时序等长及常用规则注意事项、信号完整性、电源完整性的规划等。

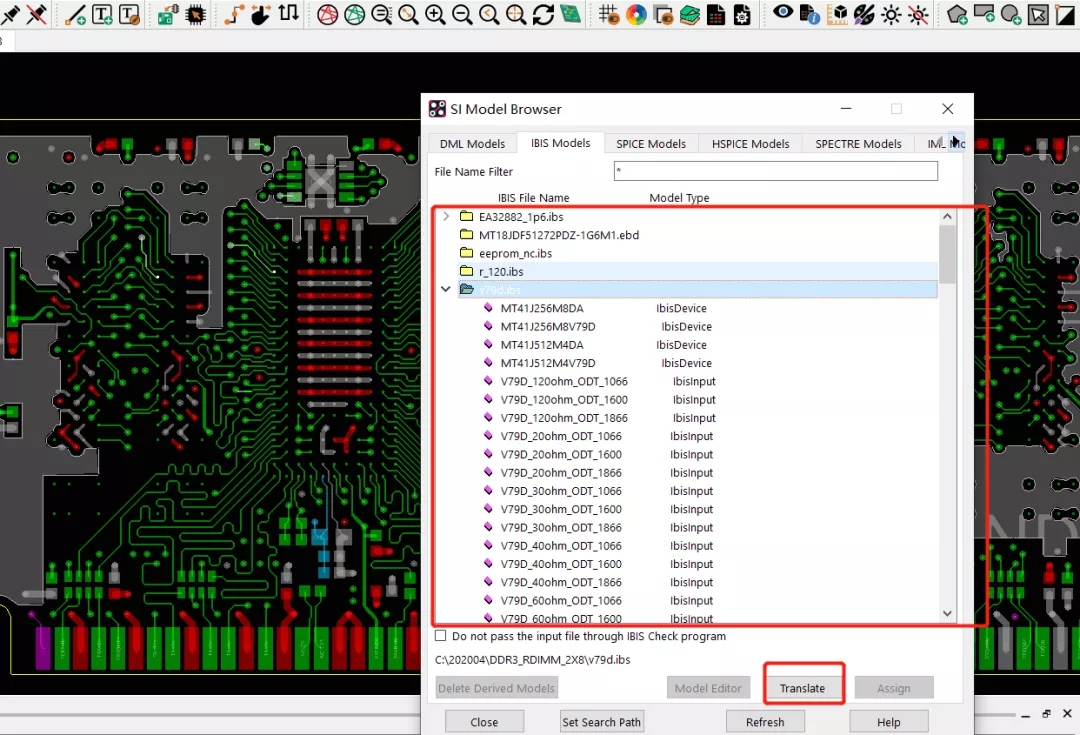

Allegro的全称是Cadence Allegro PCB Designer,是Cadence公司推出的一套完整的、高性能印制电路板设计套件。它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段进行定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。Allegro印制电路板设计提高了PCB设计效率和缩短设计周期,让您的产品尽快进入量产。Allegro是我们目前高速PCB设计中使用最多的工具。

内存条,我们都知道它是电脑平台里不可缺少的一部分,最早开始到现在的DDR2、DDR3、DDR4一类的内存条。随着科技的发展,DIY各类产品层出不穷,而镁光成为内存的老啊·牌厂家,为无数王佳提供纵横游戏的尖端装备,据10月份的消息,Cadence和镁光公布了自己的DDR5内存研发进度,两家厂商一起开始研发16GBDDR5的产品,并计划在2019年年底之前实现量产目标,

据外媒报道,三星已通知客户,DDR3内存芯片最后接单时间将截止到2022年末,并承诺会在2023年完成所有内存订单。凡亿教育带你走进DDR3:>>8层DDR3全流程PCB设计实战>>8层DDR3FLY-BY拓扑结构实战这意味着,从2024年

自DDR内存问世以来,由于它的大容量、高带宽、兼容性好等诸多特点,DDR产品很快占领内存市场并沿用至今。从DDR发展到DDR5。现在的DDR主流产品主要以DDR4为主,DDR3产品正走向落幕。今天将以DDR3和DDR4为主,重点谈谈它们之间

自Intel 12代酷睿处理器问世以来,因全面支持PCle5.0协议和引入DDR5内存协议,而备受关注,这也宣告者内存更新换代的时代即将来临,DDR3和DDR4将连续走上舞台的落幕。凡亿教育DDR产品开发课程如下:>>Allegro 8层D

DDR5内存都来了,DDR3内存是不是要彻底退出历史舞台了?那得看什么应用场景。华邦电子今日宣布,将在未来10多年内继续供应DDR3 DRAM内存芯片产品,并且会持续扩产,以确保满足客户的长期使用需求。目前,DDR3出货量占华邦DRAM总收

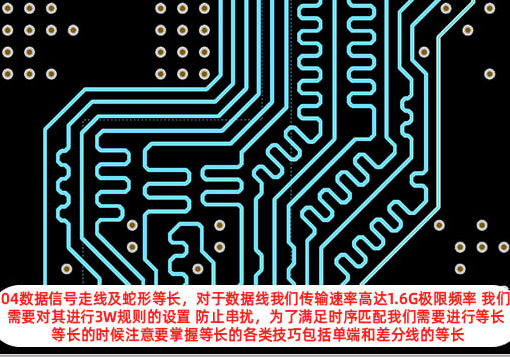

在现代电子设计领域,随着计算机性能的不断提升,高速数据传输变得越来越重要,DDR(双倍数据率)内存模块作为计算机系统的重要器件,其高速PCB布局布线显得尤为关键,正确的布线设计可提升DDR的稳定性、性能和可靠性,下面来总结下DDR模块的高速

随着半导体技术高速发展,越来越多电子产品迭代更新速度加快,高速度的数据传输及内存支持,这些都离不开DDR产品的支持,DDR产品已成为了大部分电子工程师的日常设计产品之一。然而DDR产品的设计是具有挑战性的,因为它涉及到高速数字电路和复杂的时

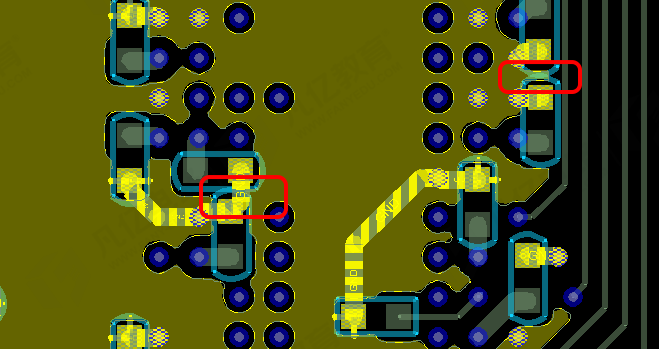

器件摆放注意不要干涉最多两个电容用一个地过孔过孔不要打到小焊盘数据线等长组以DQS 为基准线,地址线以时钟线为基准线以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://

扫码关注

扫码关注