- 全部

- 默认排序

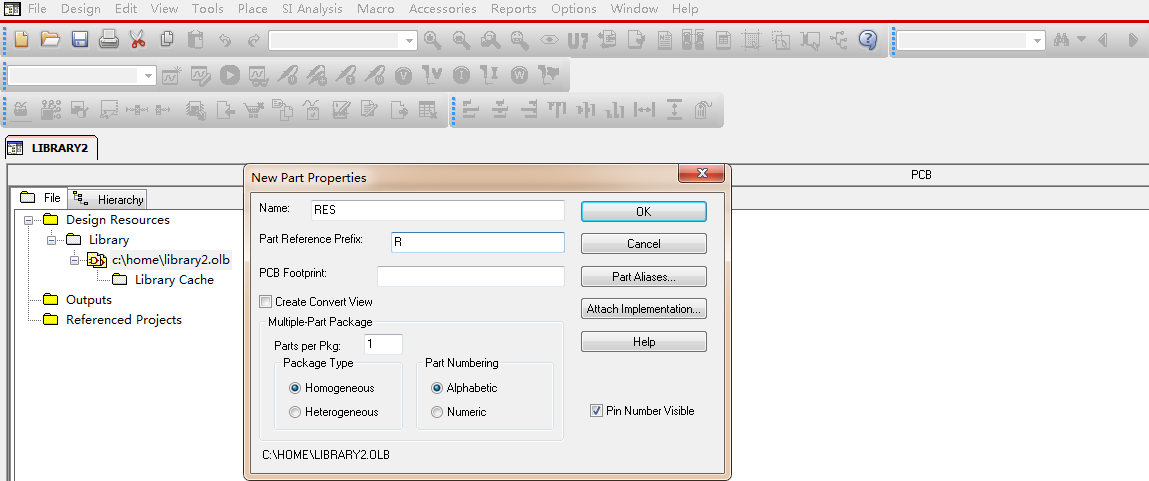

我们以一个电阻的封装为例,详细讲解创建一个简单分立元器件步骤:第一步,按照我们前面的问答中详细介绍,新建一个库文件,如图2-11所示,填写名称为RES,起始名称为R,PCB封装那一栏先可以不用填写,分立器件,Part选择1即可,其它按照默认设置; 图2-11 新建RES的库文件是示意图第二步,在弹出的R?的虚线框,在右侧栏选择Place ReCTangle,绘制一个合适的矩形框在虚线内部,运用菜单栏上的Snap To Grid,关掉格点,将矩形框调整到合适的位置,然后将虚线框缩小至跟矩

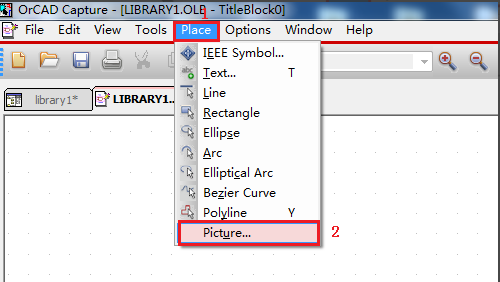

一般来说,Title Block都是调用系统本身自带的,或者是修改自带的文件,所以这里我们直接复制一个系统自带的Title Block,修改后保存在路径下,进行关联即可。 第一步,从系统自带的模板Capsym.olb中复制一个TitleBlock0到自己创建的库的路径下,选中这个元件,按CTrl+C进行复制,然后复制到自己创建的库路径下,如图2-33所示: 图2-33 复制系统自带库示意图第二步,将复制的Title B

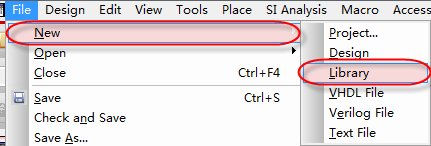

第一种方法:orcad档的原理图是支持跨原理图进行拷贝的,可以点击元器件,按CTrl+C与CTrl+V进行元器件的拷贝与粘贴。第二种方法,可以将整个原理图所用到的库文件全部拷贝到自己的库中,操作的方法与步骤如下所示:第一步,点击File→New Library,新建一个库文件,做为自己的封装库,如图2-61所示; 图2-61 新建封装库示意图第二步,选中原理图中所用到的封装库文件,在Design Cathe中,全部选中,先选中第一个,然后按住Shift,选中最后一个,这样全部

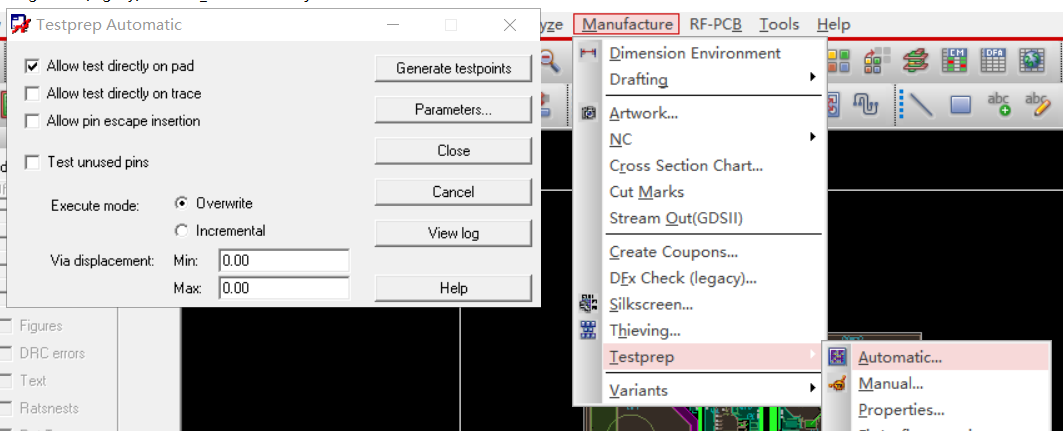

cadence allegro Allow test direCTly on pad:允许测试点在焊盘上,允许时将自动替换已有的过孔。Allow test direCTly on trace:允许测试点在信号线上,允许时测试点可以直接在信号线上。Allow pin escape insertion:允许从引脚上自动引出测试点。Test unused pins:无网络引脚添加测试点。

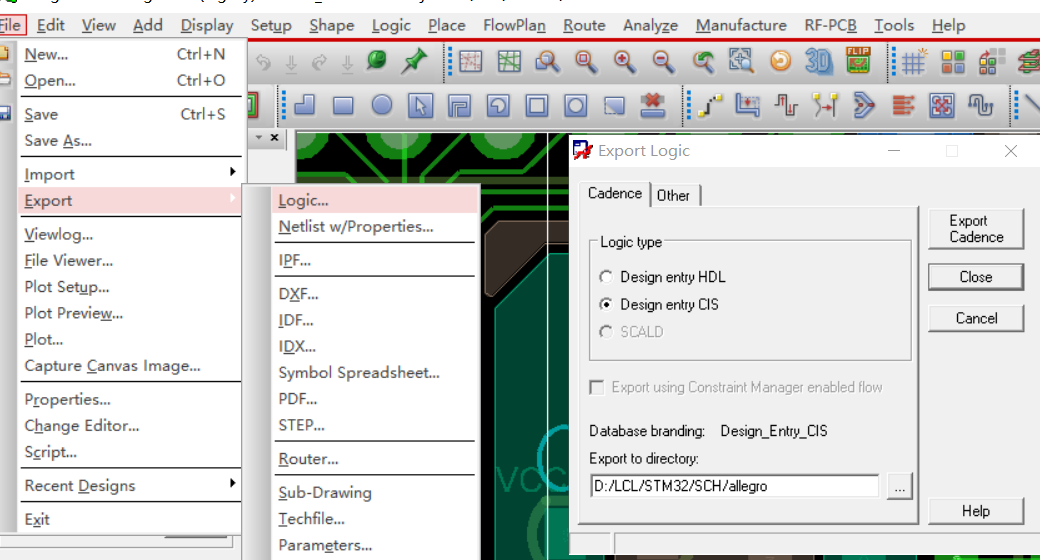

弹出export logic对话框,选择design entry CIS选项,export direCTory选择输出网表的路径,然后单击export direCTory按钮。导出完毕后,单击close按钮,关闭对话框。用orcad打开与PCB相对应的原理图,执行菜单命令tools→back annotate.....,在弹出的back annotate对话框中打开PCB editor选项卡,如图:

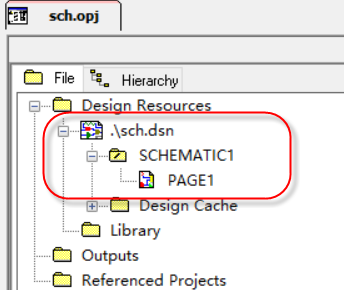

在orcad中创建原理图工程的步骤如下:第一步,打开orcad软件,执行菜单File→New ProjeCT…,如图3-1所示,在弹出的界面中选择输入工程的名称,选择工程的类型是原理图Schematic,Location选择工程文件需要存储的位置; 图3-1 新建工程文件示意图第二步,点击OK以后,创建好工程文件,工程文件下面会自动产生一个后缀为DSN的文件,DSN文件下有一个SCHEMATIC1文件,文件下面是PAGE1的原理图页面,如图3-2所示,在DNS文件右键可以创

[导读] EMC( EleCTromagnetic Compatibility) 电磁兼容性对于一个产品而言是一个非常重要的性能指标,一个产品遇到EMC的坑,很多测试很难通过,很多软件同学可能会觉得EMC更多的是硬件攻城师要去应对的难题,与软件没毛关系。

对于orcad中原理连接关系中的空管脚或者是不连接的管脚,我们的处理办法如下:Ø 非电源类型管脚空置的,放置不连接的符号,执行菜单Place→No ConneCT、或者会是按快捷键X、或者是点击右侧的不连接菜单,如图3-13所示,为了是原理图绘制规范,没有连接的网络建议都加上不连接的符号,如图3-14所示; 图3-13放置不连接符示意图 图3-14不连接符号示意图(以上内容来源于凡亿教育)

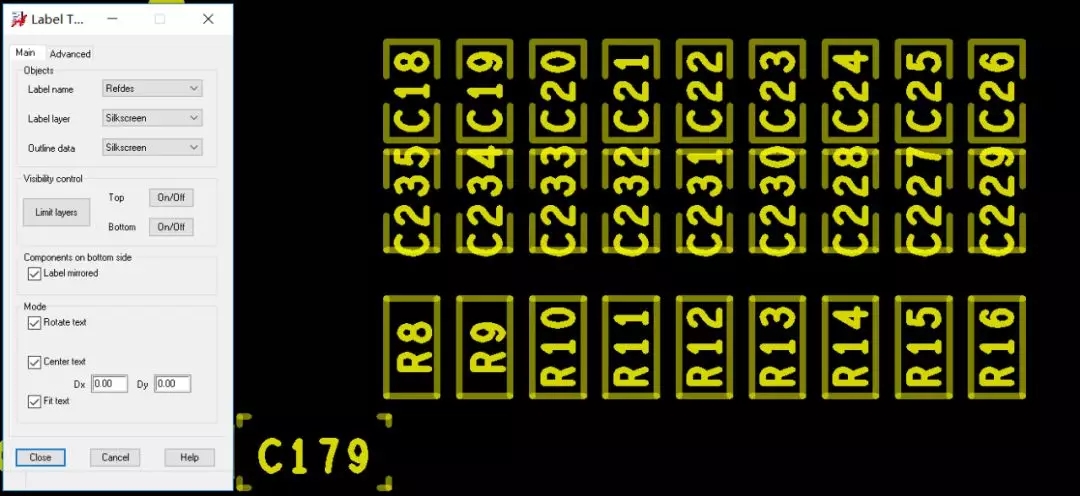

Allegro ProduCTivity Toolbox组件所带来了很多高级命令,今天我们一起学的Label Tune就是其中一个。Label Tune是用来做批量的元件字符对齐操作的命令,可以支持对丝印、显示、装配层的字符对齐操作。我们知道PCB设计里面,丝印可以给贴片和识图的工程师提供一个位置参考,可以让工程师能够快速的找到元件在PCB上的位置。如下图所示,这样整齐的丝印排列可以让工程师快速定位元件位置。

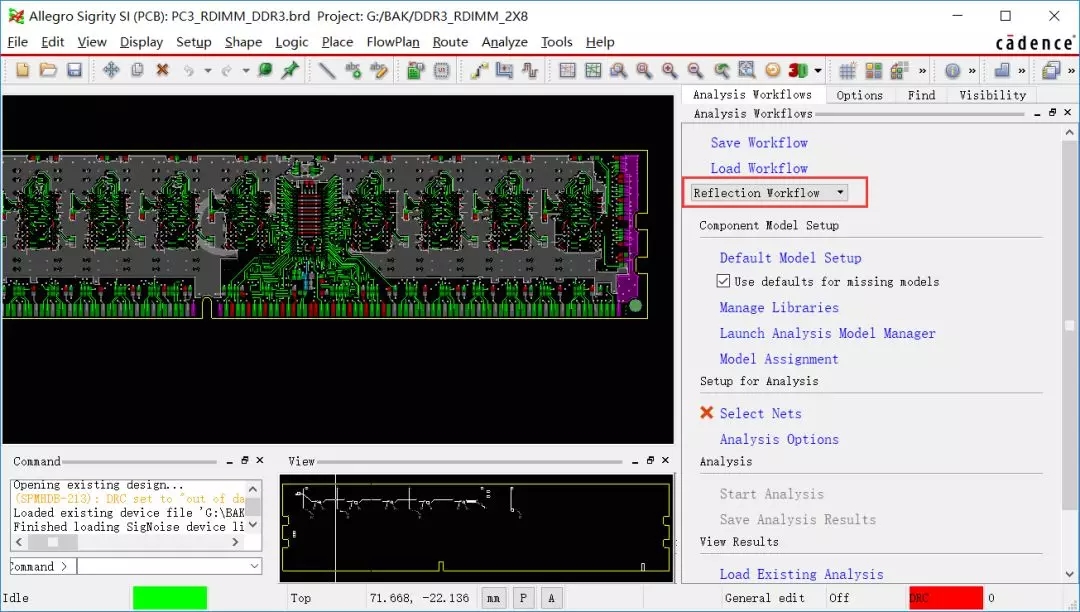

反射(refleCTion)和我们所熟悉的光经过不连续的介质时都会有部分能量反射回来一样,都是信号在传输线上的回波现象。此时信号功率没有全部传输到负载处,有一部分被反射回来现象。

扫码关注

扫码关注