- 全部

- 默认排序

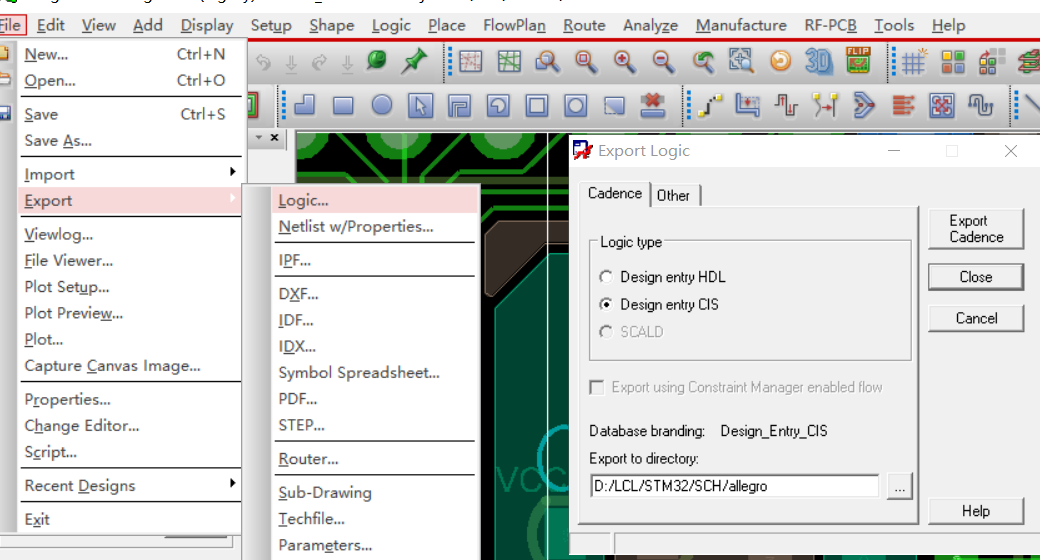

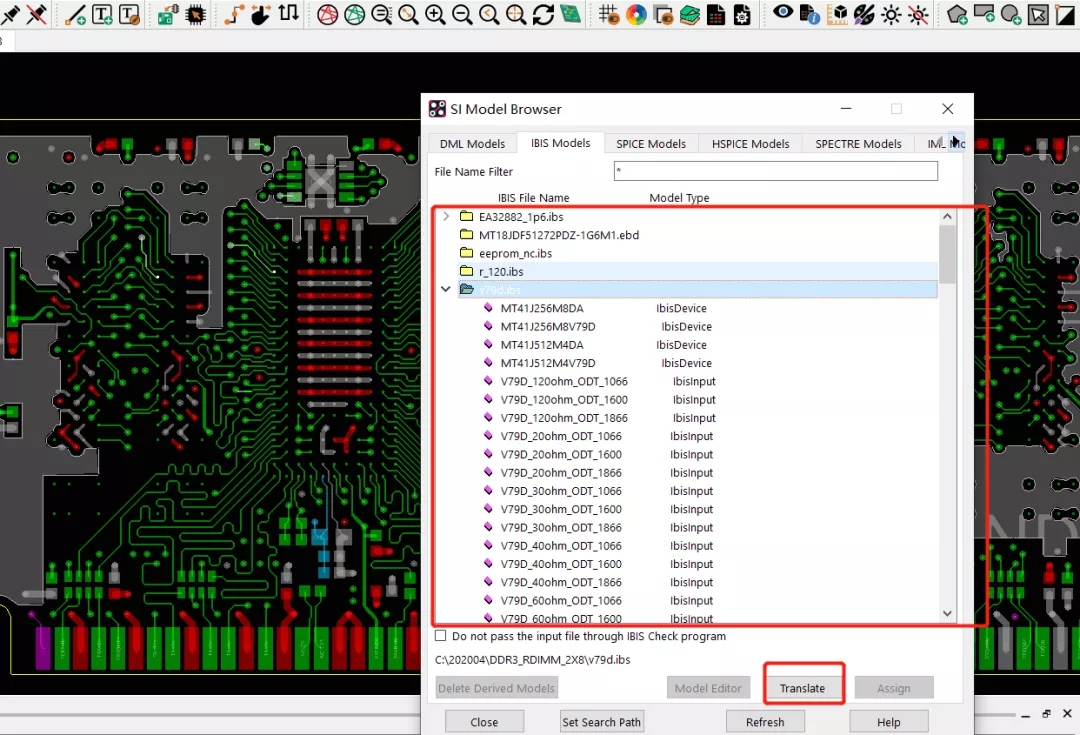

弹出export logic对话框,选择design entry CIS选项,export directory选择输出网表的路径,然后单击export directory按钮。导出完毕后,单击close按钮,关闭对话框。用orCAD打开与PCB相对应的原理图,执行菜单命令tools→back annotate.....,在弹出的back annotate对话框中打开PCB editor选项卡,如图:

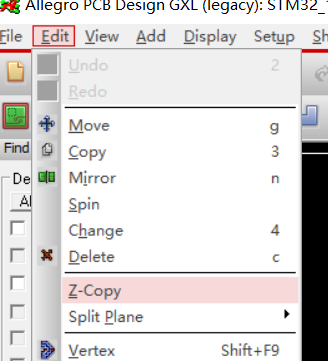

大面积敷铜就是将PCB上闲置的空间用铜箔填充,能起到美观和屏蔽噪声的效果,大面积敷铜可以直接使用CADence allegro敷铜命令,也可以用Z-Copy命令将地平面的铜箔直接复制到外层。Z-Copy的命令,执行菜单命令edit→Z-Copy,如图:

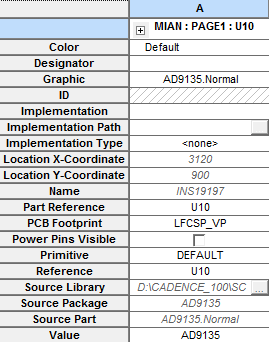

在使用orCAD绘制原理图的过程中,需要对每一个元器件进行封装的指定,否则没有指定封装,在输出网表的时,会产生错误。指定器件封装的方法如下:第一步,在orCAD原理图中,双击该器件,会弹出改器件的属性框,如图4-1所示; 图4-1 元器件属性框示意图第二步,在元器件的属性框中,我们可以找到有一栏叫做PCB Footprint,这一栏就是改器件的封装名称,我们只需要在这一栏填上相对应的封装名称即可;最后,在PCB Footprint这一栏所填写的封装名称必须与PCB建立的封装

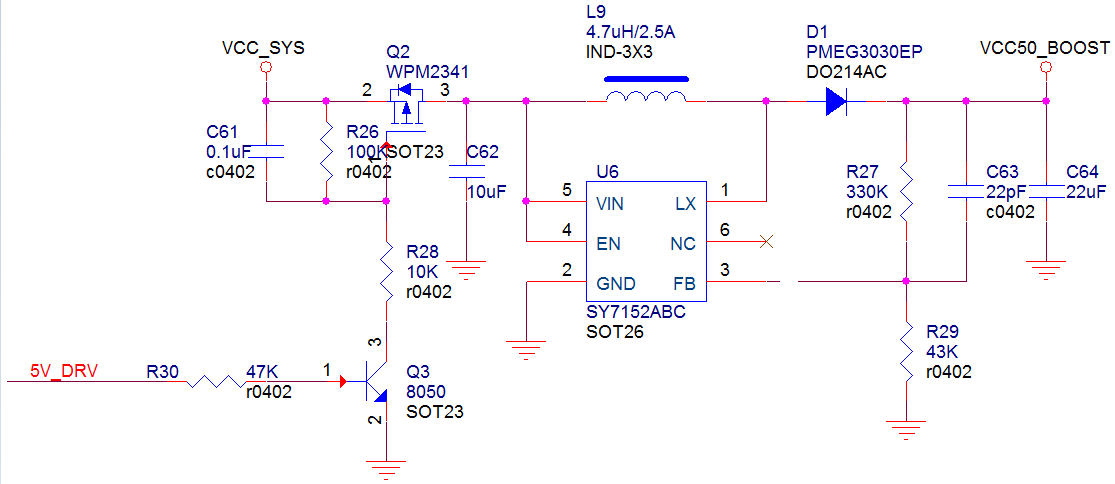

现在市面上用的最多的是,OrCAD软件绘制原理图,Allegro软件绘制PCB版图。我们现在讲解一下怎么使用OrCAD软件将绘制好的原理图,输出第一方的网表,然后将第一方的网表导入到Allegro软件中,具体操作如下:第一步,选中原理图根目录,执行菜单命令Tools-Create Netlist,创建网表,如图6-26所示; 图6-26 使用OrCAD软件创建第一方网表示意图第二步,执行上述命令之后,会弹出如图6-27所示的界面,在此界面中选择PCB Editor,进行第一

操作方法如下所示:第一步,按照前面所述的方法,新建一个库文件,绘制好外形框;第二步,点击右侧边栏Place Pin Array,按一定排列顺序来放置管脚,如图2-66所示, 图2-66放置序列管脚示意图第三步,弹出的Place Pin Array属性框编辑需要放置管脚的个数数目以及属性即可,参数设置含义如下所示:l Starting Name:起始管脚的名称,这个先设置数字,后面编属性统一更改;l Star

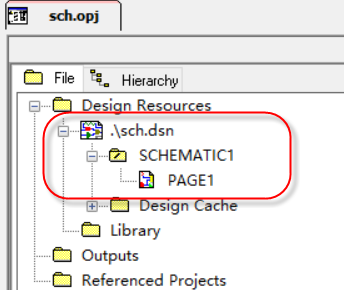

在orCAD中创建原理图工程的步骤如下:第一步,打开orCAD软件,执行菜单File→New Project…,如图3-1所示,在弹出的界面中选择输入工程的名称,选择工程的类型是原理图Schematic,Location选择工程文件需要存储的位置; 图3-1 新建工程文件示意图第二步,点击OK以后,创建好工程文件,工程文件下面会自动产生一个后缀为DSN的文件,DSN文件下有一个SCHEMATIC1文件,文件下面是PAGE1的原理图页面,如图3-2所示,在DNS文件右键可以创

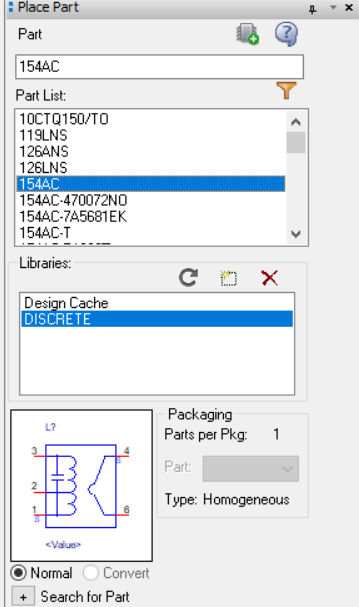

orCAD绘制原理图时怎么放置器件?orCAD在绘制原理图时,需要从库中把元器件放置到原理图中,放置的方法如下:第一步,执行菜单Place→Part,或者按快捷键P、或者点击右侧菜单栏放置元器件的图标,来调出放置元器件的窗口,如图3-9所示; 图3-9 放置元器件窗口示意图第二步,在放置元器件之前,需要在下面的库路径下指定封装库的路径,如图3-10所示,点击Add Library命令添加库路径; 图3-10 添加库路径示意图第三步,在库路径下选中改元器

对于orCAD中原理连接关系中的空管脚或者是不连接的管脚,我们的处理办法如下:Ø 非电源类型管脚空置的,放置不连接的符号,执行菜单Place→No Connect、或者会是按快捷键X、或者是点击右侧的不连接菜单,如图3-13所示,为了是原理图绘制规范,没有连接的网络建议都加上不连接的符号,如图3-14所示; 图3-13放置不连接符示意图 图3-14不连接符号示意图(以上内容来源于凡亿教育)

Allegro的全称是CADence Allegro PCB Designer,是CADence公司推出的一套完整的、高性能印制电路板设计套件。它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段进行定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。Allegro印制电路板设计提高了PCB设计效率和缩短设计周期,让您的产品尽快进入量产。Allegro是我们目前高速PCB设计中使用最多的工具。

HOT CHIPS大会上的演讲将设计分割成处理器本身和设计的I/O部分。处理器可以采用最先进、最昂贵的节点制造,而I/O则可以采用不够先进、较便宜的节点制造(通常落后一代)。下方图片是Intel的Lakefield芯片,它有一个I/O基片(采用非前沿的14纳米制程),10纳米制程的处理器,以及封装在顶部的动态随机存取存储器(DRAM)。这些都采用Intel的Foveros 3D技术组装。

扫码关注

扫码关注