- 全部

- 默认排序

orCAd中元器件应该怎么进行镜像与翻转呢? 答:orCAd的元器件,可以按照X轴或者Y轴进行左右镜像、上下镜像。操作方法如下: 第一步,选中元器件,按快捷键H即可对器件进行左右镜像,上下位置不变,如图3-11所示,对比镜像前后两个元器件的变化;

在orCAd软件中,同一页面的连接关系处理有两种方式,一种是直接连线的方式,一种是放置网络编号的方式使其连接在一起。详细的操作方式如下所示:

一、课程目录工具(Altium Designer、CAM350)1、PCB 设计软件中的拼板示意板框的绘制2、设计软件中的 Gerber 输出

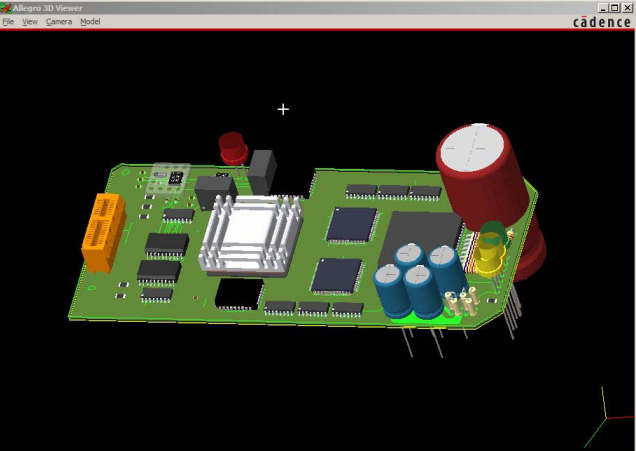

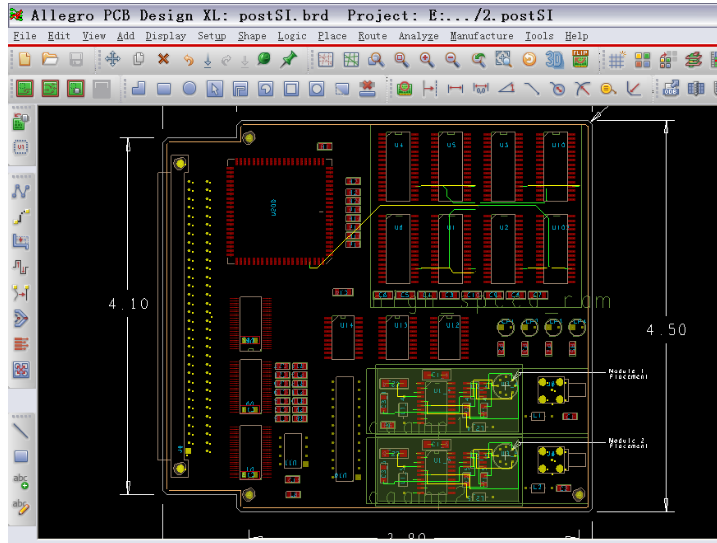

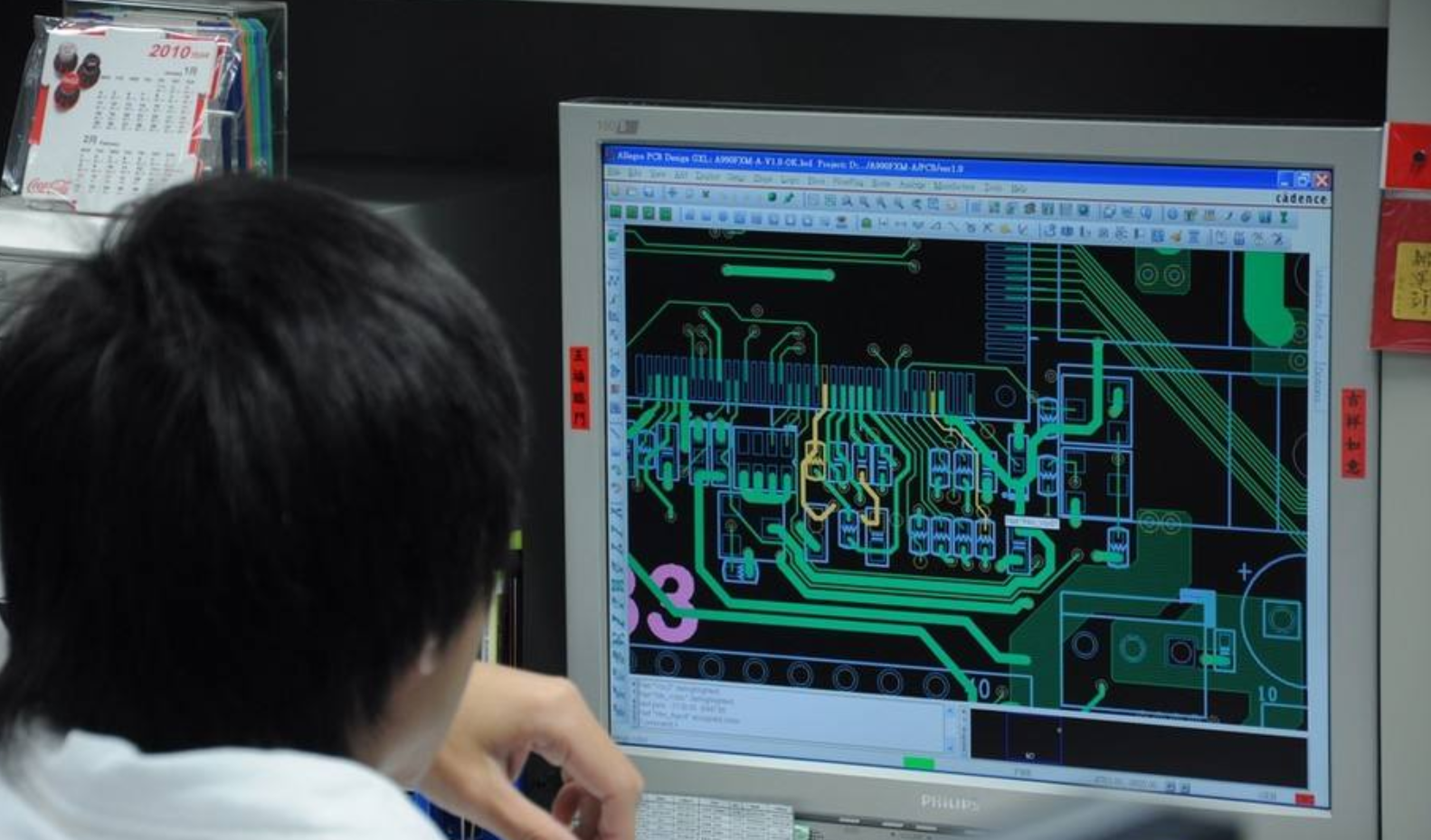

一、课程详情这个是一个CAdence Allegro非常经典的 6 层一阶盲打孔设计,基于三星系列 S3C6410 ,全程讲解了通过CAdence Allegro,运用-阶盲埋孔的技术进行工控核心板卡的 PCB 设计教程视频,从前期的原理图导入,到后期输出生产文件( GERBER)的全过程。

分别在上图示位置选择需要显示3d效果的器件进行匹配,对各参数进行设置以达到理想效果。设置好后点击Save进行保存。然后可点击Report进行查看匹配结果

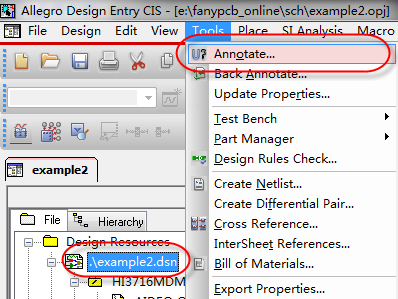

第一步,选中整个原理图的根目录,然后执行菜单Tools-Annotate,如图3-56所示,进行原理图选项的编辑; 图3-56 原理图进行编译示意图第二步,然后对器件的位号进行复位的操作。在弹出的原理图编译界面中,如图3-57所示,在Action选项中,现将原理图本身已经存在的位号全部复位,点击Reset Part References to “?”,则全部的位号则变成的问号,可参照图3-57所示。 图3-57 原理图编位号复位设置示意图第三步,把所有

高速高密度多层PCB板的SI/EMC(信号完整性/电磁兼容)问题长久以来一直是设计者所面对的最大挑战。然而,随着主流的MCU、DSP和处理器大多工作在100MHz以上(有些甚至工作于GHz级以上),以及越来越多的高速I/O埠和RF前端也都工作在GHz级以上,再加上应用系统的小型化趋势导致的PCB空间缩小问题,使得目前的高速高密度PCB板设计已经变得越来越普遍。许多产业分析师指出,在进入21世纪以后,80%以上的多层PCB设计都将会针对高速电路。

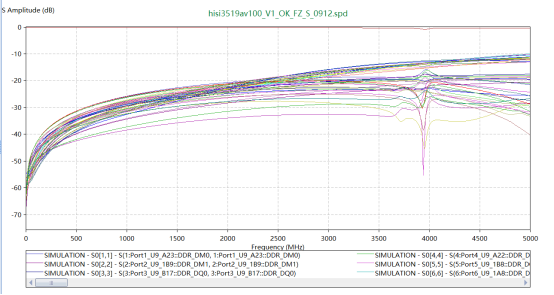

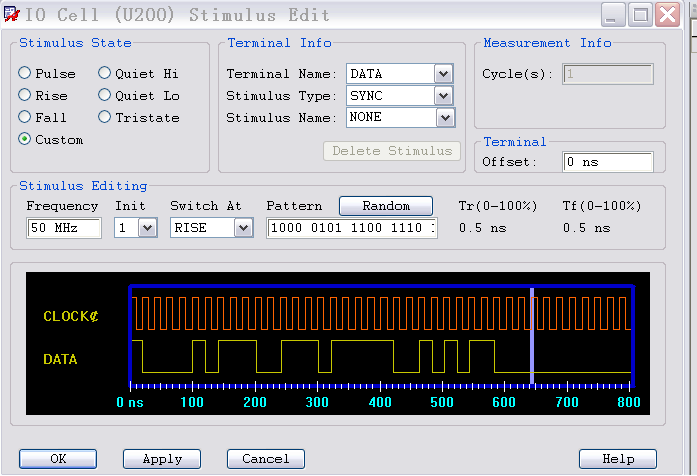

SI分析的前期准备完成之后,就可以进行信号完整性分析了,执行Analyze/SI EMI Sim/Probe命令,然后选择需要进行SI分析的网络或者差分对(模型分配中必须设置好差分对),如下图所示:

现在越来越多的高速设计是采用一种有利于加快开发周期的更有效的方法。先是建立一套满足设计性能指标的物理设计规择,通过这些规则来限制PCB布局布线。在器件安装之前,先进行仿真设计。在这种虚拟测试中,设计者可以对比设计指标来评估性能。而这些关键的前提因素是要建立一套针对性能指标的物理设计规则,而规则的基础又是建立在基于模型的仿真分析和准确预测电气特性之上的,所以不同阶段的仿真分析显得非常重要。

扫码关注

扫码关注