- 全部

- 默认排序

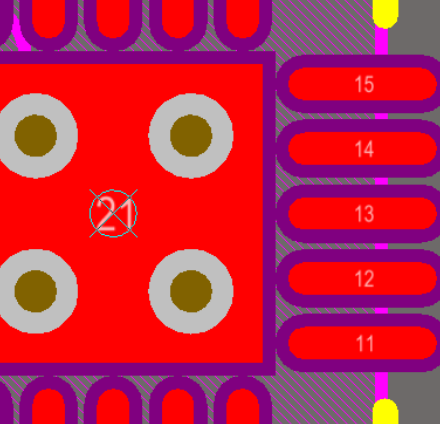

在收到其他人发来的一个PCB设计文件,但是没有封装库,需要如何从PCB板中去进行封装的提取?Altium Designer软件就提供了如此强大的功能。

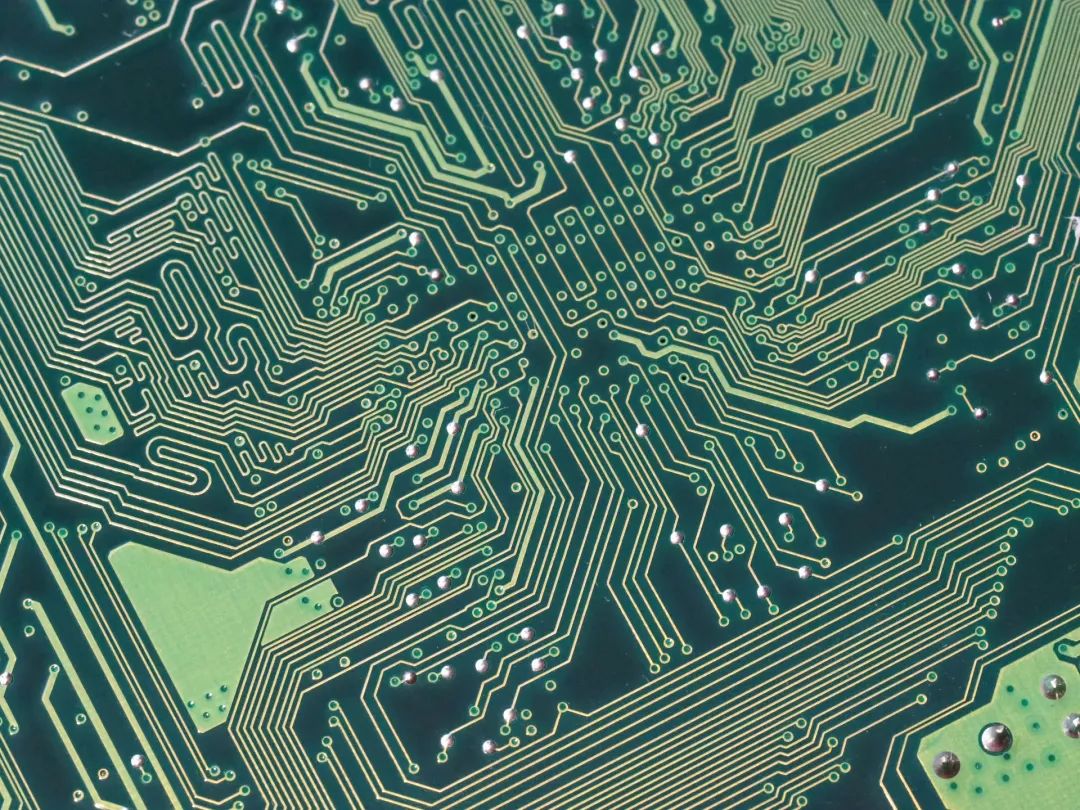

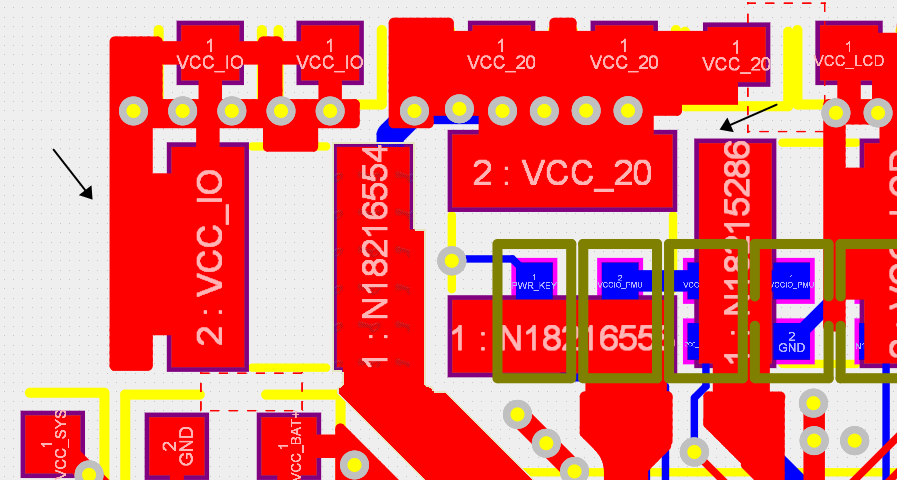

敷铜完整性的要求如图5-208与5-209所示,设计上保证主控下方敷铜的完整性及连续性,能够提供良好的信号回流路径,改善信号传输质量,提高产品的稳定性,同时也可以改善铜皮的散热性能。

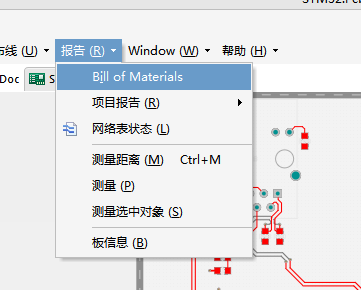

BOM表即物料清单,当原理图设计完成之后,就可以开始整理物料清单准备采购元件了,如何将被设计中用到的元件的信息进行输出以方便采购?这个时候就会用到BOM表了。

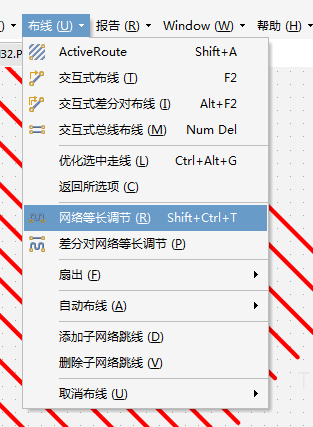

在PCB设计中,蛇形等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多条数据信号基于同一个时钟采样,每个时钟周期可能要采样两次甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序影响比重越来越大,为了保证在数据采样点能正确采集所有信号的值,就必须对信号传输延迟进行控制。

至于USB,SATA,PCIE等串行信号,并没有上述并行总线的时钟概念,其时钟是隐含在串行数据中的。数据发送方时钟包含在数据中发出,数据接收方通过接受到的数据恢复出时钟信号。这类串行总线没有上述并行总线等长布线的概念。但因为这些串行信号都采用差分信号,为了保证差分信号的信号质量,对差分信号对的布线一般会要求等长且按总线规范的要求进行阻抗匹配的控制

CadenCe Allegro现在几乎已成为高速板设计中实际上的工业标准,最新版本是Allegro 17.4。与其前端产品Capture相结合,可完成高速、高密度、多层的复杂 PCB 设计布线工作。

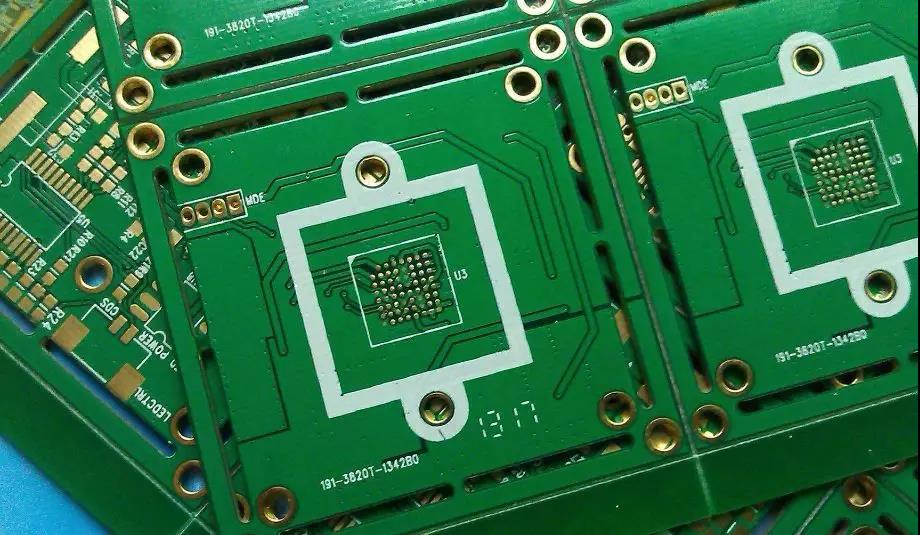

PCB在材料、层数、制程上的多样化以适不同的电子产品及其特殊需求,因此其种类划分比较多。 以下就归纳一些通用的区别办法,来简单介绍PCB的分类以及它的制造工艺。那么我们就从它的三个方面来分析一下吧。

扫码关注

扫码关注