- 全部

- 默认排序

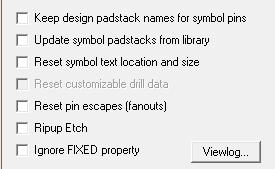

答:我们在进行PCB设计之前,会将所有的封装都处理好了,但是,中间难免会有封装更迭或者是物料更改的吗,这里就需要在PCB中对相同的PCB封装进行更新,具体的操作细节,我们这里详细讲述一下,如下所示:

答:在前面的问题中,我们讲述了对同一种类型的元器件进行封装的更新,有时候会出现这样的情况,出现错误的操作,误删除的其中一个器件的丝印或者是什么的,能否只更新这一个器件呢,其它的不进行更新,当然是可以的,具体的操作步骤如下所示:

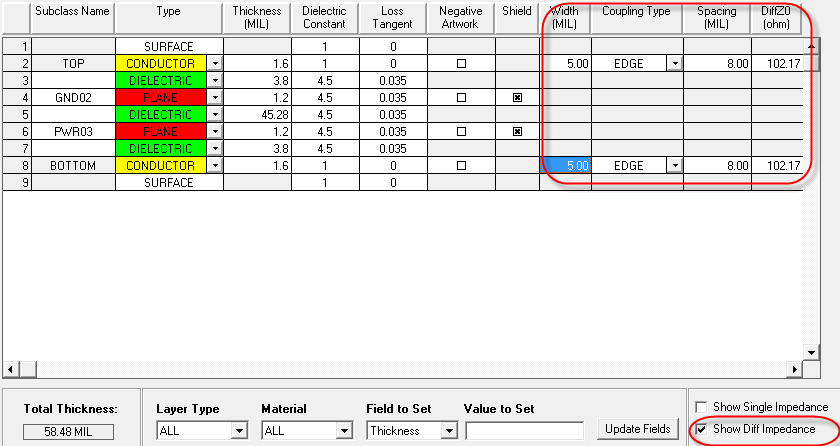

答:我们在Allegro软件中,新建的PCB文件,默认的模板都是只有两层,TOP层跟BOTTOM层,但是我们在实际的电子设计中,是有多层板的,比如4层、6层、8层,我们在PCB中如何添加层叠呢,具体的操作步骤如下所示:

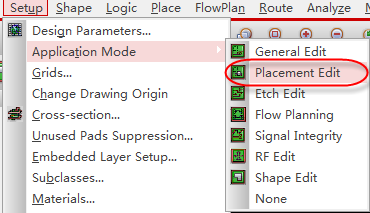

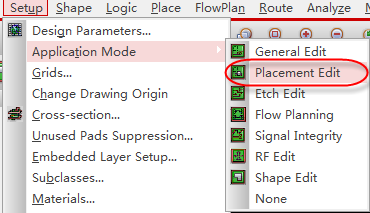

答:在上述的问答中,我们详细讲述了多层板应该如何进行层叠设置,并没有涉及对整个PCB板的阻抗设计,这一问呢,我们就介绍一下如何在Allegro软件中,输入参数,简单的对阻抗线宽做一个大概的估算,具体操作如下:

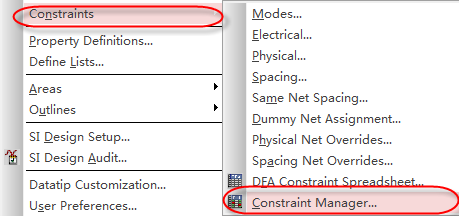

答:我们布局完成之后,计算好阻抗线宽之后呢,就要开始进行布线操作,在布线之前,我们需要添加走线的规则,这样走出来的线宽才是阻抗线宽,具体添加阻抗线宽的详细步骤如下所示:

答:添加完成走线的阻抗线宽之后,这样PCB板上信号走线就会按照所设置的物理走线线宽进行。除了添加走线的线宽之外,还需要添加间距规则,来规范不同元素之间的间距,满足生产的需求,添加间距的操作步骤如下所示:

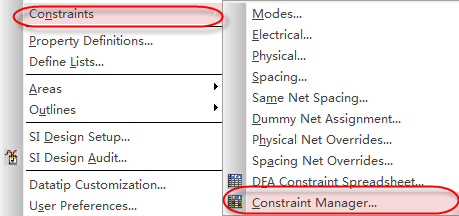

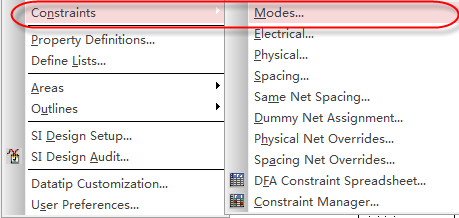

答:我们在时序等长时,除了考虑信号线的走线的长度以外,在高速设计领域里还需要考虑封装本身的引脚长度。所谓封装引脚长度,指的就是元器件封装内部的引脚长度,这个长度一般芯片的厂家会提供这数据,我们要做的就是将数据导入到规则管理器中,与等长一起处理,具体的操作步骤如下:

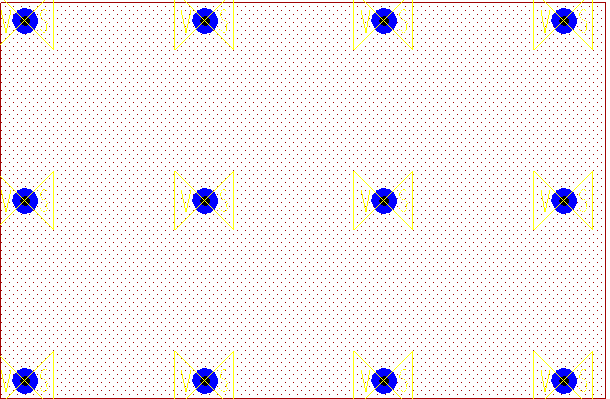

答:我们在Allegro软件中,铺铜的时候,有两种铜皮可以选择,一种是静态铜皮,一种是动态铜皮,如图6-101所示,是静态铜皮,如图6-102所示,是动态铜皮。

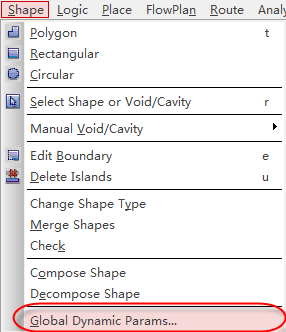

答:我们在Allegro软件中,我们在铺铜的时候,需要事先对铜皮与焊盘的连接方式进行设置,有全连接、十字连接等多种连接方式,我们需要对全局的铜皮的连接方式进行一个设置,具体的操作步骤如下所示:

答:我们在进行设计的时候,如果是在同一层进行铺铜处理,当出现有两个或者两个以上的铜皮重叠的情况出现,如图6-106所示,A铜皮与B铜皮重叠在一起,A铜皮的优先级要高于B铜皮,所以A铜皮是保持原来的形状的,B铜皮会自动避让一块。

扫码关注

扫码关注