- 全部

- 默认排序

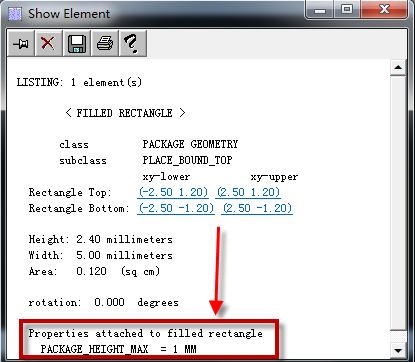

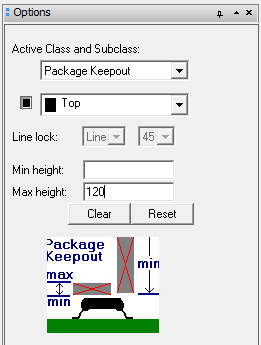

答:在做PCB设计时,有时结构上会对局部的器件布局有高度要求,不能将超过高度限制的器件放到限高区,否则会导致PCB装配问题。这个高度信息我们可以在做PCB封装时进行设置,设置好了就可以在设计时查看高度信息,辅助我们进行PCB设计。第一步,打开一个PCB封装,将Package Geometry-Place_Bound_top层显示出来,如图4-70所示, 图4-70 显示元器件占地面积示意图第二步,点击Setup-AreAS-Package Height选项,如图4-71所示

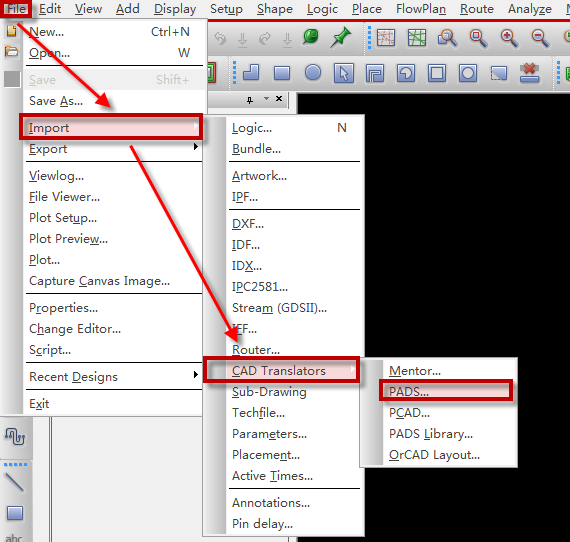

答:Pads封装导入到Allegro,一般先是通过Pads PCB转Allegro PCB,转换完成后,将封装导出,再逐个对PCB封装进行检查修改,修改为标准可用的封装。第一步,将Pads PCB导出ASC文件,打开PCB点击文件-导出选项,在弹出的对话框中设置好导出文件的文件夹和文件名,然后点击保存,如图4-78所示; 图4-78 导出ASc文件示意图第二步,在弹出的对话框中勾选所有内容,格式中选择PADS Layout V2007选项,然后点击确定,就能生成ASC文件,

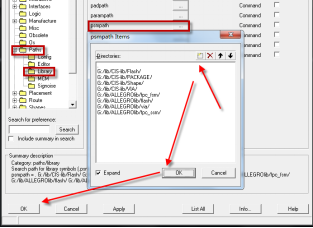

答:在将网表导入到PCB的过程中,常会由于带通孔的PCB封装内的焊盘中FlASh在相应的路径中找不到,而导致导网表报错,报错内容及提示如图4-93所示: 图4-93 错误提示示意图根据图4-93所示,我们可以分析得出以下几个结论:Ø 导网表时报错的器封装名是CON2X5_2P54M。Ø PCB封装中焊盘名为PAD100SQR165THR的焊盘不能被完整提取到,原因是在设置的库路径下找不到名为THR100X165C150X180X040的FlASh。对于此

答:根据器件规格书(DatASheet)制作封装时,一般做出来的封装焊盘管脚长度需要做适当的补偿,即适量地对器件原先的管脚加长一点,具体的补偿方法,是根据器件的管脚类型来补偿的,可按以下办法:第一类,无引脚延伸型SMD封装,如图4-100所示: 图4-100 无引脚延伸型SMD封装示意图A—零件实体长度 X—补偿后焊盘长度 H—零件脚可焊接高度

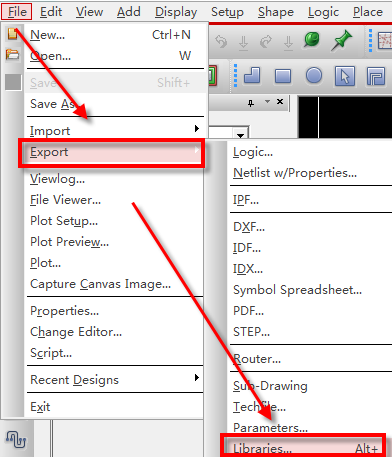

答:在导网表时,如果碰到有缺失FlASh的报错,而正好缺失的Falsh在另一个项目中使用过,我们可以从另一个PCB中调用,具体的步骤如下:第一步,打开PCB,点击File-Export-Libraries…,在弹出的对话框中勾选Shape and flASh symbols、No library dependencies选项,设置好导出的文件夹路径,点击Export导出,如图4-111所示;

答:椭圆形焊盘的FlASh一般可按以下公式进行计算尺寸:B = H’ + 0.5 mmD = W’ + 0.5 mm – B

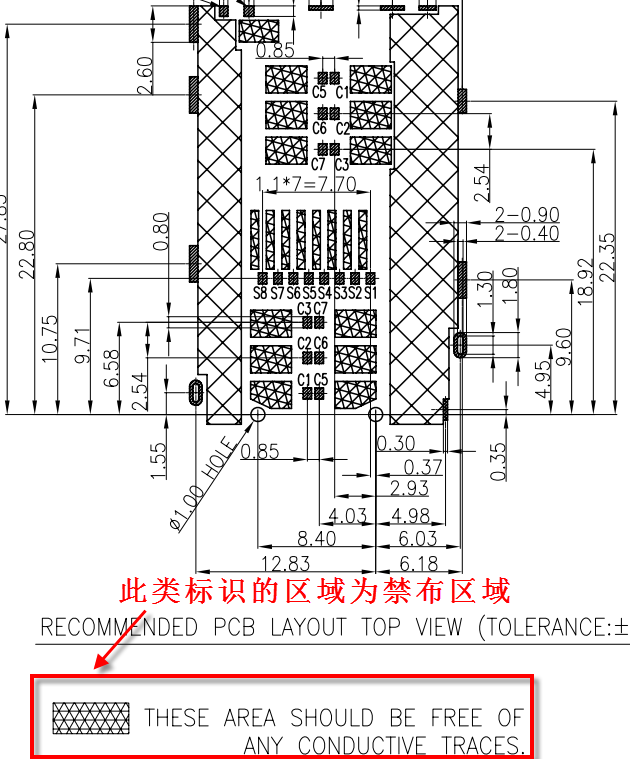

答:在PCB封装中,出现以下情况需要画Keepout层,一般绘制在Route Keepout、Via Keepout层。第一,如果DatASheet中指明了需要画Keepout层,则需要绘制Keepout层,绘制的大小按照DatASheet中指定的大小,如图4-122所示,

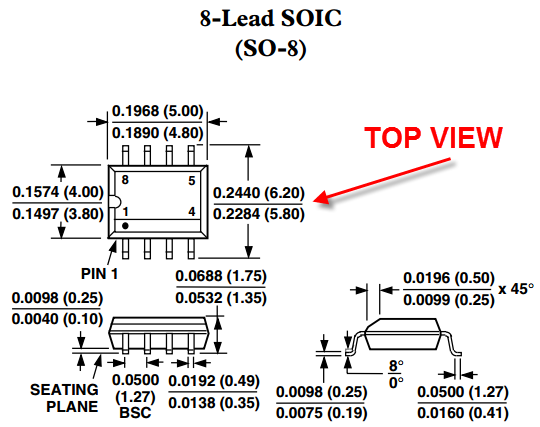

答:要分析DatASheet资料,分析资料中的以下内容:第一步,分析视图,分析DatASheet中所提供的图示,一般会提供几个视图,首先要分析出哪个图是TOP视图,哪个是BOTTOM视图,以免做封装时做反,如图4-126所示,

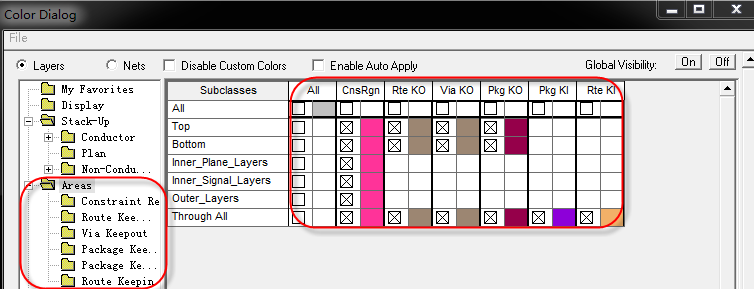

答:我们在进行PCB设计的时候,需要根据不同的PCB板结构以及一些电子产品的需求来进行各种不同区域的设计,包括允许布局区域设计、禁止布局区域设计。允许布线区域设计等等。在Allegro设计中,设置这些就在AreAS,如图5-60所示。

答:我们在进行一些复杂的PCB设计时,都会有很多结构限制,比如这里限高3MM等需求,为了辅助工程师们更好的进行设计,我们需要在PCB区域内绘制限高区域,并设置限高的参数,具体操作如下所示:第一步,在PCB板上绘制需要限高的区域,执行菜单命令Setup-AreAS,在下拉菜单中选择Package Keepout,如图5-66所示,显示器件禁布区。

扫码关注

扫码关注