- 全部

- 默认排序

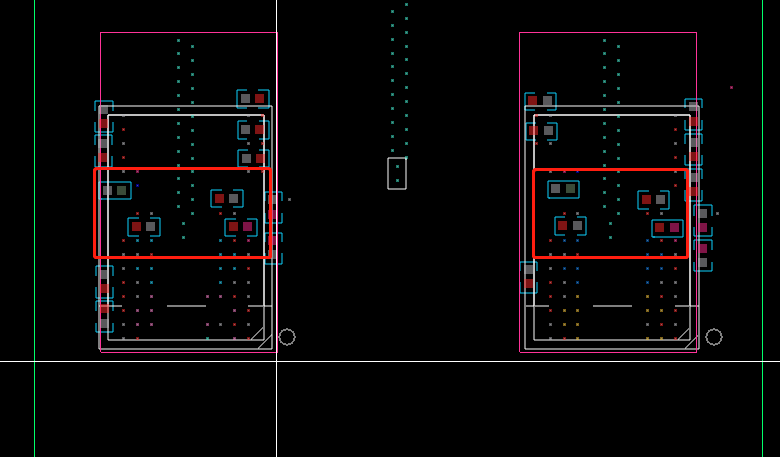

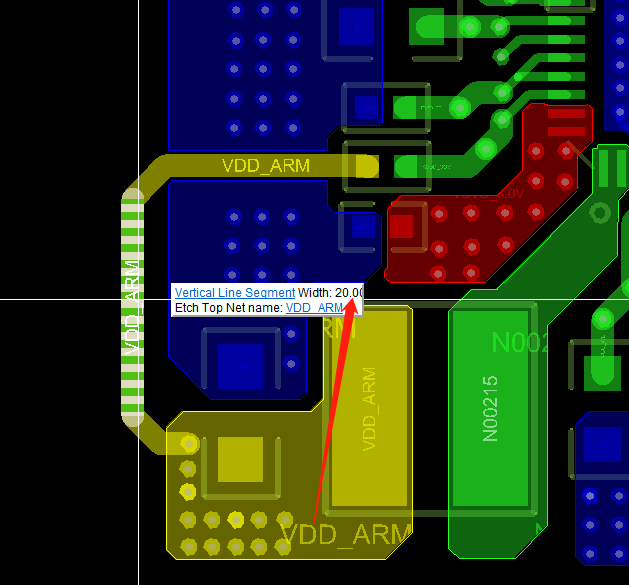

个别器件注意整体对齐:注意等长线之间需要满足3W间距原则:没满足的都自己优化下。数据线组内也需要满足3W:差分对内等长误差为5MIL:其他的没什么问题。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问

Cadence ALLEGRO是一款电子设计自动化工具,常用于原理图绘制和电路设计,在使用ALLEGRO画原理图时,电子工程师可能为了确保文件的准确性和稳定性,能够顺利进行后续的PCB设计和制造,需要注意这些非法字符,那么有哪些非法字符?1

晶振尽量靠近管脚放置包地要包全差分误差对内控制在+-5mil以内以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com/item.htm?s

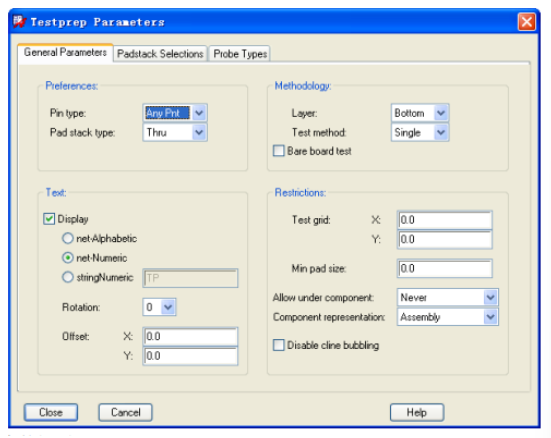

ALLEGRO因其功能强大、界面灵活、可适应切换复杂项目的需求,很快成为全球最受欢迎的EDA软件之一,而很多工程师在ALLEGRO软件中添加测试点,这样做的好处是为了进行电路的功能测试和故障诊断,那么如何在ALLEGRO添加/生成测试点?下

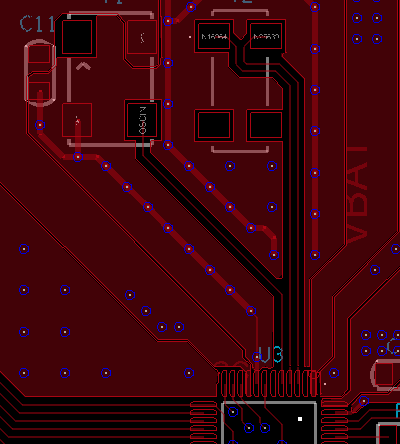

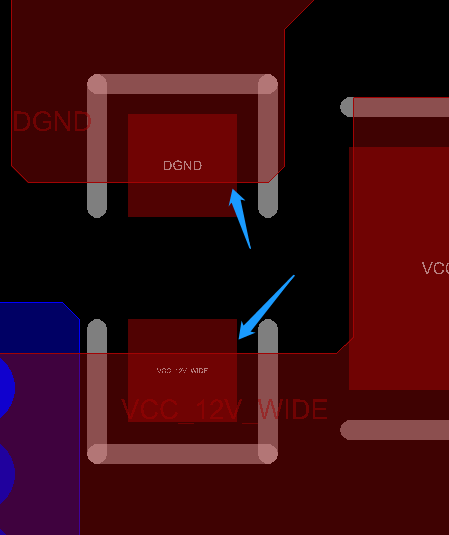

存在多处开路地网络后期自己在bottom层铺铜进行连接2.采用单点接地,此处可以不用打孔,只需要在芯片中心打孔进行回流即可3.输入打孔要打在滤波电容的前面4.输出打孔要打在滤波电容后面5.以上评审报告来源于凡亿教育90天高速PCB特训班作业

尽量包住焊盘丝印太乱了调整一下这个gnd要连上以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com/item.htm?spm=a1z10.

随着时代高速发展,Altium Designer(AD)、ALLEGRO、Pads等是全球主流的三大EDA软件,因此越来越多工程师被要求学习这些软件,在使用EDA软件设计PCB过程时,熟悉和合理配置快捷键是提高工作效率的关键之一,然而不记得

在ALLEGRO软件中,导出带有钻孔数据的DXF文件是一个常见的任务,特别是需要将涉及文件与其他CAD工具或PCB制造商共享时,所以下面将谈谈,如何在ALLEGRO软件中导出带有钻孔数据的dxf文件。1、打开设计文件首先,打开ALLEGRO

你这里底层铺铜打孔后你顶层也要铺铜才能连接这些地方都还有飞线没有连接起来你这里把器件放到底层打孔了要铺铜或者走线连接上。这个作业没有时间限制的,什么时候完成什么时候交就可以。把这个好好改一下连完线再交吧。

反馈线只用走10mil即可2.输出打孔要打在最后一个电容后面,反馈走线即可,不用铺铜输出打孔都需要再调整一下3.此处存在drc,短路了4.此处不满足载流,建议铺铜处理5.此处反馈器件要靠近管脚放置6.管脚滤波电容需要靠近管脚放置,保证一个管

扫码关注

扫码关注