- 全部

- 默认排序

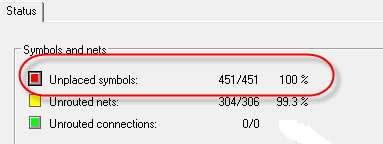

很多刚开始接触这个Allegro软件的同学,就有这样的疑问,我的原理图的网表都已经导入到PCB中了,为什么PCB板上什么都没有呢?元器件、飞线等都没有。其实,只要是网表导入到PCB中,器件都是在后台显示,需要指定元器件封装库,然后手动放置出来,下面我们详细介绍一下操作的办法:第一步,需要检查原理图的网表是否导入成功,执行菜单命令Display,在下拉菜单中选择Status,整个PCB文件的状态,如图324-1所示,进入到状态的界面,最上面一栏是Symbols and nets的选项,网表导入成功

MachXO3 FPGA 系列是最小、成本最低的 I/O 可编程平台,旨在扩展系统功能并使用并行和串行 I/O 桥接新兴的连接接口。 MachX03 简化了新兴连接接口 MIPI、PCIe 和 GbE 的实施,例如通过将先进的小尺寸封装与片

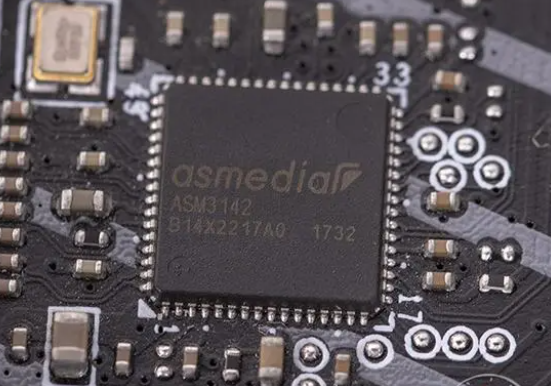

一、ASM3142 USB 3.1控制芯片介绍:ASM3142 是第三代USB 3.1 Gen 2芯片,将成为通过USB进行快速数据传输的新标准。是全球最快的USB解决方案, 可提高性能并实现更高的功效,节省高达50%的功耗。与ASM 21

一、5M1270ZF256I5N IC CPLD 980MC 6.2NS 256FBGA说明:与其他cpld相比,MAX V系列低成本和低功耗cpld提供更大的密度和每占地面积的I/ o。MAX V器件的密度从40到2210个逻辑元件(32

IC设计作为半导体供应链的上游部分,一直是半导体企业重点布局的战略产业之一,但由于其研发难度大,技术限制多,投入资金高,所以很少企业能够成功在IC设计市场打下一片天地,能够坚持到最后仅有少数人,那么我国的IC设计企业是怎么样的情况?近日,中

描述Artix-7 FPGA能够在多个方面实现更高的性价比,这些方面包括逻辑、信号处理、嵌入式内存、LVDS I/O、内存接口,以及收发器。Artix-7 FPGA非常适合用于需要高端功能的成本敏感型应用。功能亮点6.6Gb/s收发器,实现

5M2210ZF256I5N CPLD MAX V设备器件特点;低成本、低功耗、非易失性CPLD架构即时启动(0.5 ms或更短)配置时间待机电流低至25µA,快速下电/复位操作快速传播延迟和时钟到输出时间内部振荡器模拟RSDS输出支持,数

本文将为小伙伴们介绍紫光盘古系列22K(MES22GP)开发板。盘古22K开发板为紫光同创高校协同育人项目官方定制开发板。 * 盘古22(MES22GP) 开发板采用紫光同创logos pgl22g-6cmbg324器件为核心的开发板,板卡外挂HDMI输入输出、PMOD、LED数码管、

器件型号XC7A35T-1FTG256C和XC7A100T-2CSG324I同属于Xilinx Artix®-7 FPGA系列现场可编程门阵列,该Artix-7 FPGA能够在多个方面实现更高的性价比,这些方面包括逻辑、信号处理、嵌入式内存

全站最新内容推荐

- 1加码技术,打破困境,PSPice电路仿真助你解锁职场新高度!

- 2简谈稳压二极管和普通二极管的区别

- 3贴片元件如何拆卸及焊接?

- 4盘点电子工程师必须了解的21个电路

- 5英伟达GB300芯片受阻,存在过热问题

- 6WARELEO李增原创H04课程大纲的安排课程中内容及工具及课程的重点学习办法的讲解

- 7WARELEO李增原创H03根据自己的关注知识点和所需要的知识来选择需要的图书包邮递

- 8WARELEO李增原创H02理工男生李老师的介绍从51单片机驱动到FPGA到仿真设计之路

- 9WARELEO李增原创H01信号电源完整性设计与HFSS射频天线设计仿真验证研修课程主题

- 10WARELEO李增:反射仿真的信号观察办法及时域串扰的仿真设置及观察技巧

扫码关注

扫码关注