- 全部

- 默认排序

网口作为一种通讯接口,在电路中的应用也是越来越广泛,从以前的百兆WAN口,到现在的千兆WAN口,速度越来越快,对设计的要求也越来越高。怎样把网口的PCB部分设计好,提高信号质量,这就是本场直播,凡亿将给你带来的惊喜。

仅看近30年的发展,以PC为代表的行业几度繁荣而后归于平静,从最早的百兆级处理器速度倍频直到今天的几个GHz级别,总线位宽从16位扩展到今天的64位,以Intel为首的行业龙头公司将CPU的处理能力整整提升了成百上千倍。 在总线宽度和处理器速度达到瓶颈后的近10年里,整个行业将突破的战场放在了高速接口上,外部串行高速接口的速率从Gbps迅速飞升到几十个Gbps,为了实现更高的吞吐量,还采用了复杂的高阶调制和增加链路宽度的办法。这一切简直是以“迅雷不及掩耳盗铃之势”汹涌而至,作为“攻城狮”的你做

9月29日,由中国科学院大连化学物理研究所(以下简称“大连化物所”)李先锋研究员团队提供技术支撑的百兆瓦级大连液流电池储能调峰电站进入并网调试最后阶段,预计10月中旬正式投入使用。该电站是迄今为止全球功率最大、容量最大的液流电池储能调峰电站

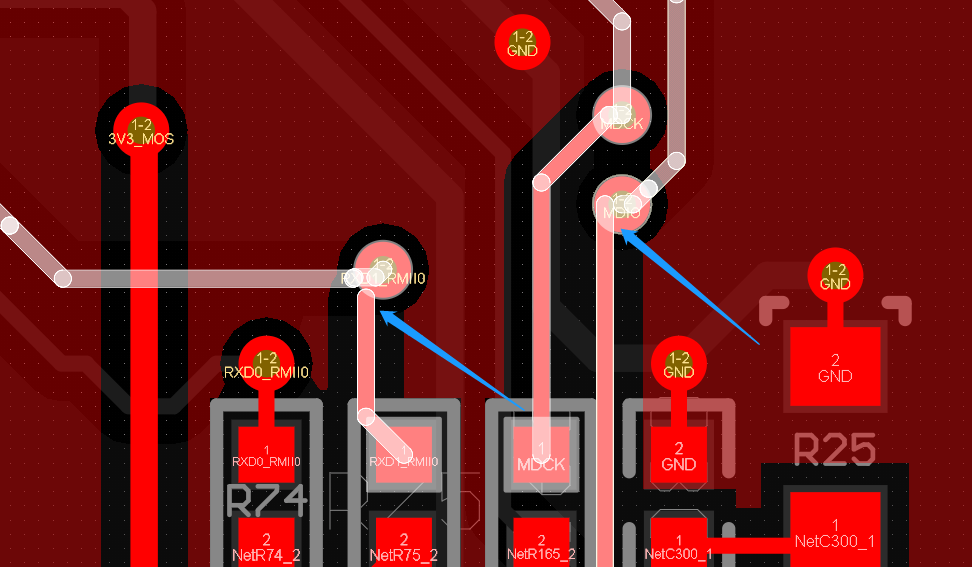

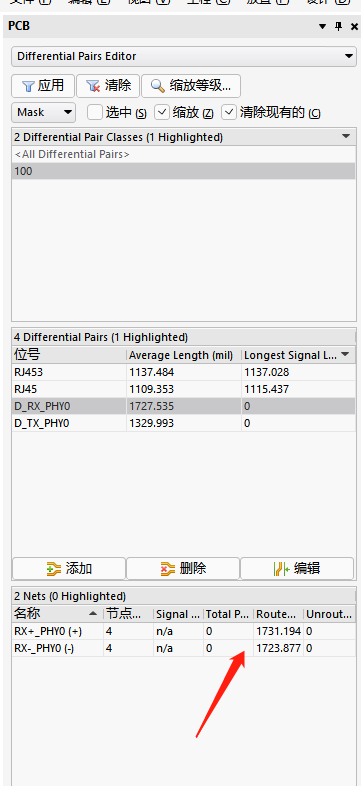

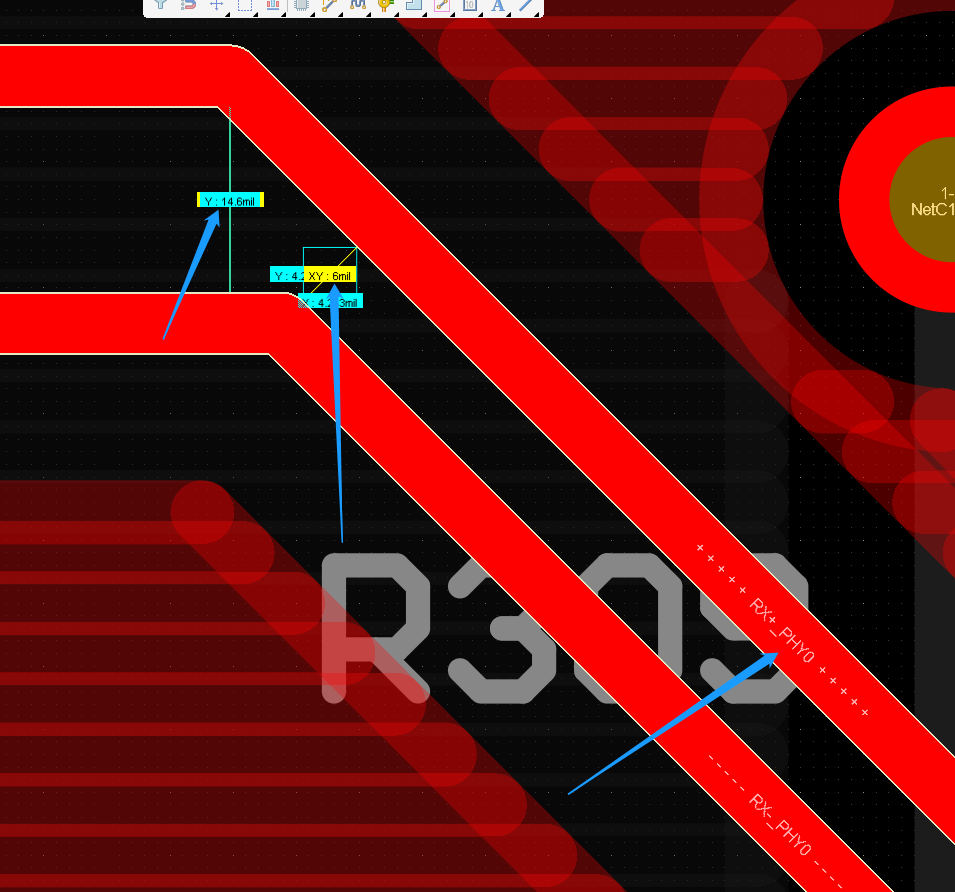

走线未连接到过孔中心2.差分出线需要优化一下3.线宽突变,确认一下具体线宽,尽量保持统一4.电源一层连通,无需打孔5.差分处理不规范,锯齿状等长不能超过线距的两倍6.pcb上存在开路7.RJ45座子需要挖空以上评审报告来源于凡亿教育90天高

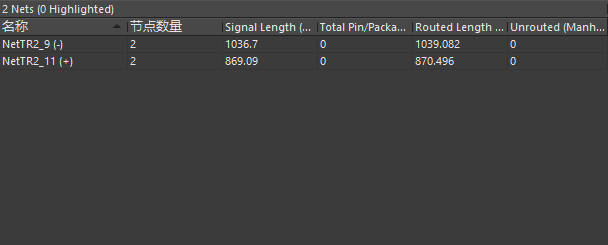

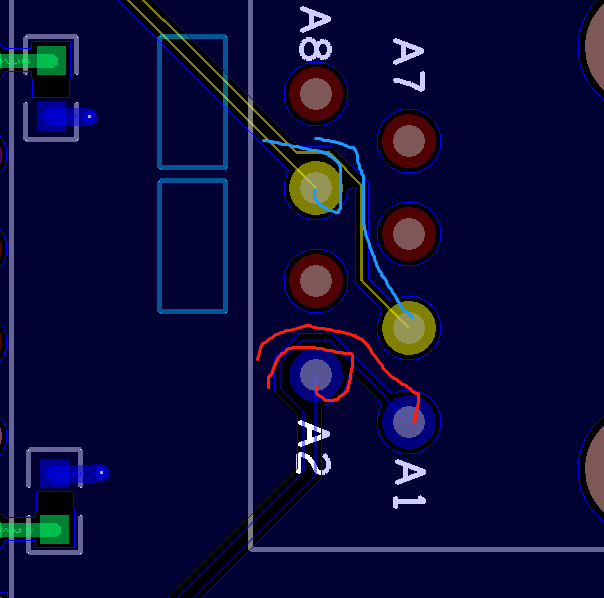

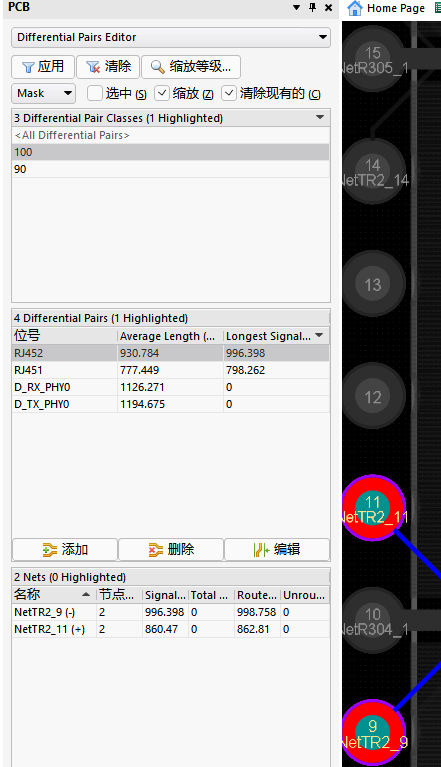

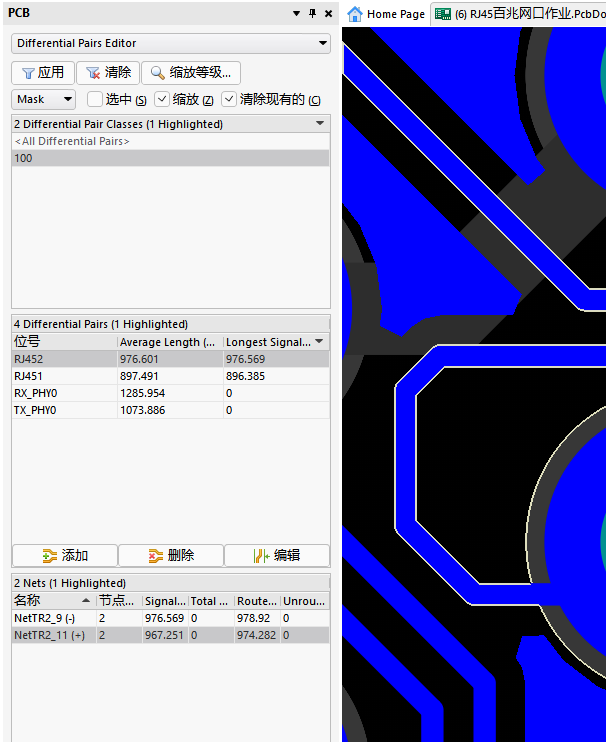

差分对内不等长这里差分不耦合这里rx,tx走线间距不满足3w以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com/item.htm?spm

差分出线尽量耦合2.打孔从底层进行连接即可3.滤波电容靠近管脚放置4.焊盘出线需要优化5.四组差分需要进行对内等长,误差5mil6.时钟信号需要单根包地处理以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以

网口的差分信号需要对内等长,误差5mil2.差分出线要尽量耦合3.走线未连接到过孔中心4.RJ45座子需要挖空5.pcb上存在短路6.差分走线不满足差分规则7.锯齿状等长不能超过线距的两倍8.出线宽度超焊盘宽度,与焊盘同宽即可9.时钟包地需

差分对内等长误差5mil2.未添加TR和RX的class3.包地要在地线上 打过孔4.器件干涉5.差分出线要尽量耦合6.时钟信号需要包地处理,并且打上地过孔7.pcb上存在两处开路以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需

差分对内等长误差5mil2.锯齿状等长不能超过线距的两倍3.走线未连接到过孔中心,容易造成开路4.线宽尽量保持一致5.pcb上存在4出开路以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系

差分走线不满足间距2.差分出线要尽量耦合,走线不要有直角差分走线都存在问题,自己后期重新优化一下3.网口差分要进行对内等长,误差5mil5.pcb上存在开路6.线宽尽量保持一致7.时钟信号包地可以在地线上多打地过孔8.确认此处是否满足载流9

扫码关注

扫码关注