- 全部

- 默认排序

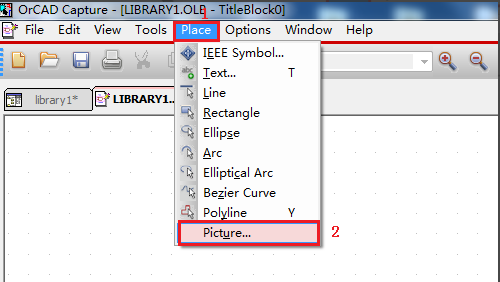

本视频主要给介绍了orcad里面怎么创建带图片的TitleBlock,这样一些不能用文字表达的图片log就能添加进去,使设计更加方便。

我们在进行PCB设计的时候,最后我们需要去进行DRC的检查,检查完成之后会出现各种总各样的报错,当然其中常见的间距报错,规则报错我们都知道怎么更改,也能看懂大概的意思。可以有时候碰到一些比较少见的报错,就会不知道这个报错的原因是什么 了。比如今天要讲解的DRC报错中的“Isolated copper:Split pllane....”的报错,为了方便大家了解这项报错,我们找到了素材图片如下:

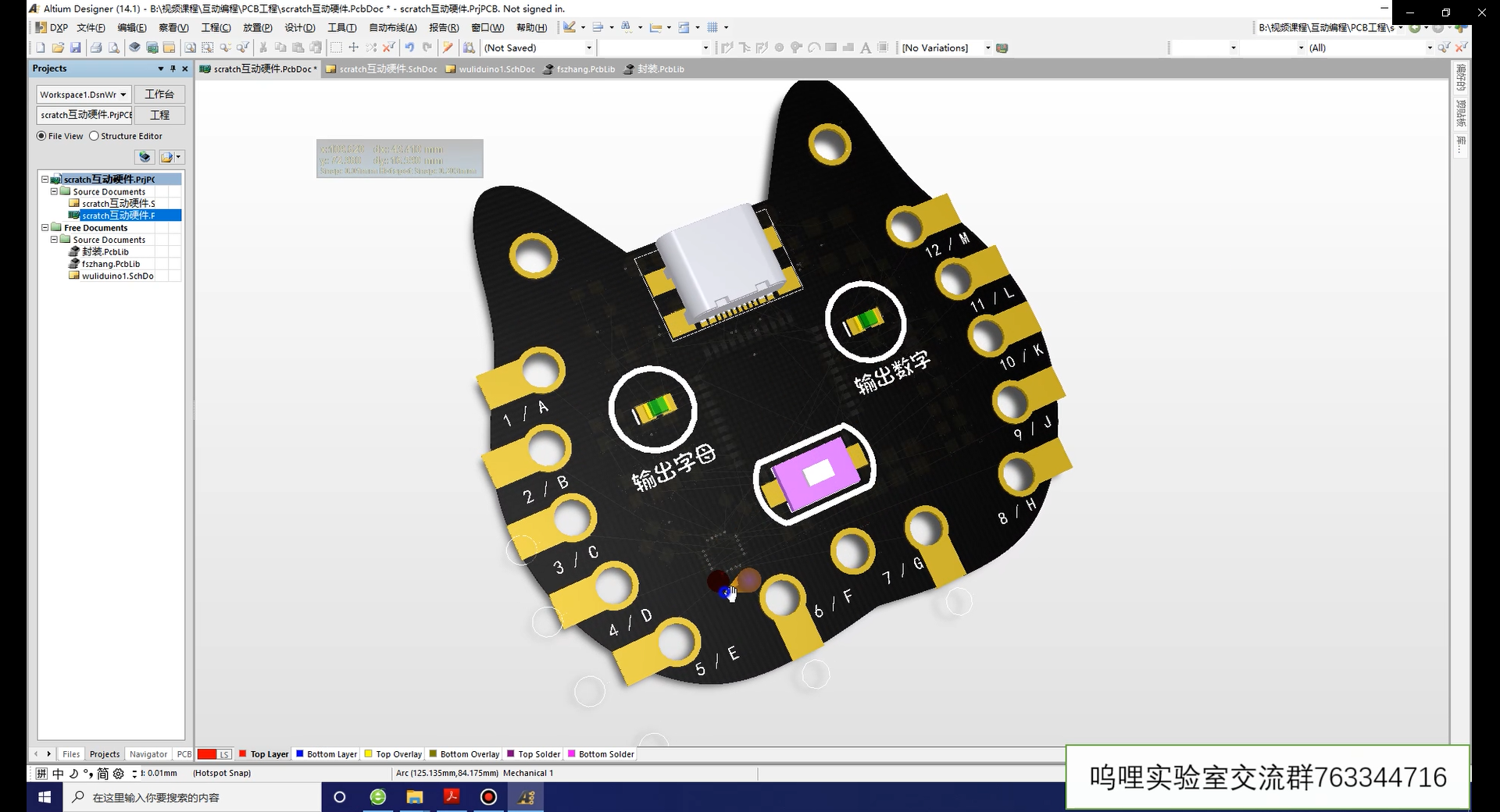

本系列课程将完成记录一款硬件应用产品开发全程,它涉及电路原理分析、AD元件绘制、PCB器件封装绘制、PCB布局布线、电路板打样、电路板调试、编程、产品3D建模、产品图片出图、动画宣传视频、品宣文案等全套内容。

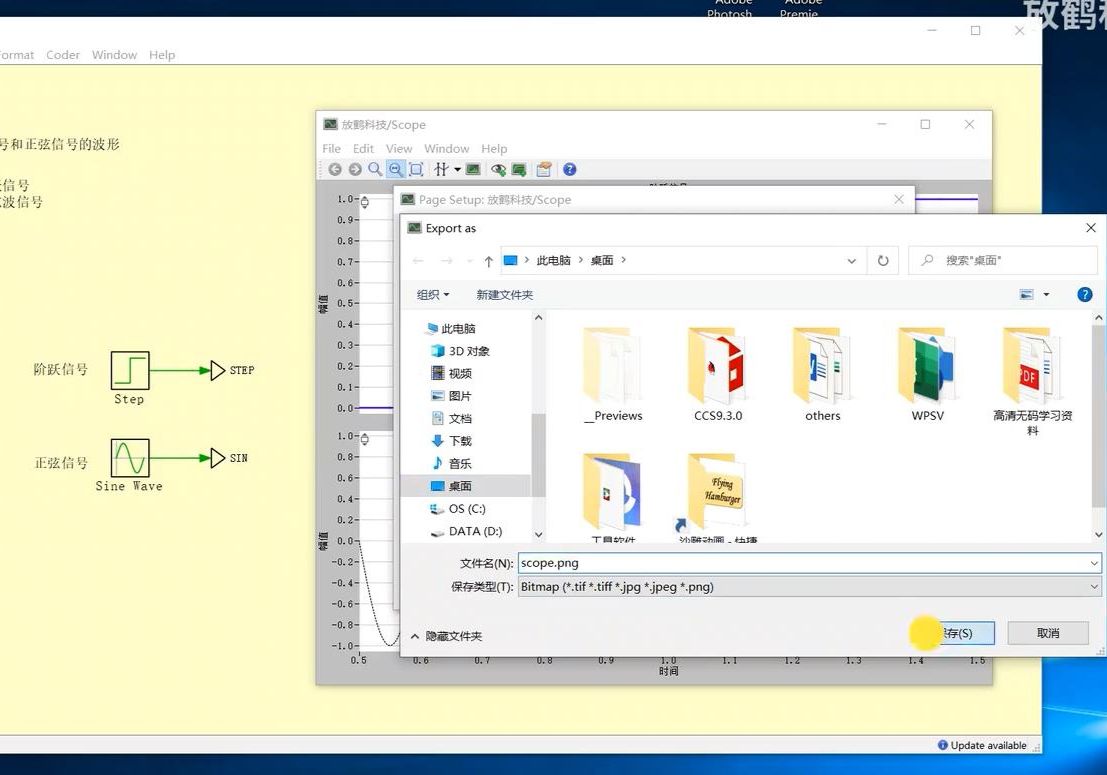

11. 将波形导出图片

小心翼翼走进学员教室,发现学员们都在非常认真的画板,完全没有注意到小编的存在~ 据可靠消息,凡亿会给线下实体学员提供免费住宿以及上课设备哦。

一般来说,Title Block都是调用系统本身自带的,或者是修改自带的文件,所以这里我们直接复制一个系统自带的Title Block,修改后保存在路径下,进行关联即可。 第一步,从系统自带的模板Capsym.olb中复制一个TitleBlock0到自己创建的库的路径下,选中这个元件,按Ctrl+C进行复制,然后复制到自己创建的库路径下,如图2-33所示: 图2-33 复制系统自带库示意图第二步,将复制的Title B

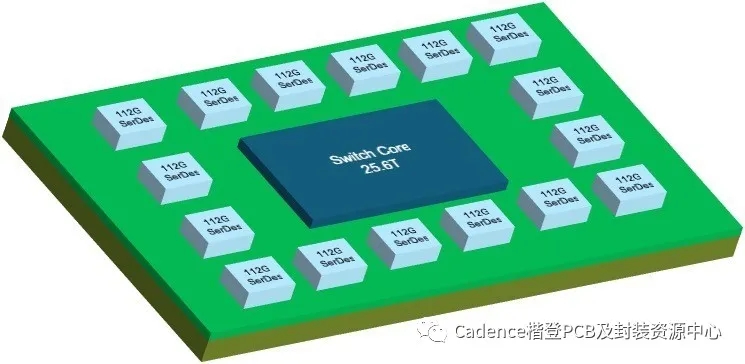

HOT CHIPS大会上的演讲将设计分割成处理器本身和设计的I/O部分。处理器可以采用最先进、最昂贵的节点制造,而I/O则可以采用不够先进、较便宜的节点制造(通常落后一代)。下方图片是Intel的Lakefield芯片,它有一个I/O基片(采用非前沿的14纳米制程),10纳米制程的处理器,以及封装在顶部的动态随机存取存储器(DRAM)。这些都采用Intel的Foveros 3D技术组装。

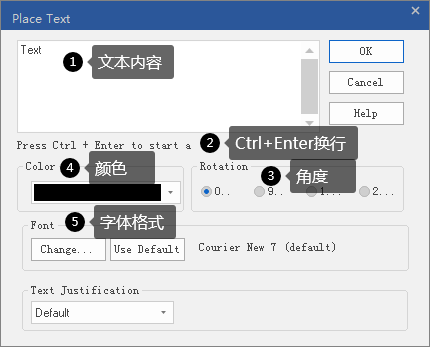

放置字符标注及图片

实际设计当中,经常需要对一些功能进行文字说明,或者对可选线路进行文字标注。这些文字注释可以大大增强线路的可读性,后期也可以让布线工程充分对所关注的线路进行特别处理。

答:一般来说,Title Block都是调用系统本身自带的,或者是修改自带的文件,所以这里我们直接复制一个系统自带的Title Block,修改后保存在路径下,进行关联即可。 第一步,从系统自带的模板Capsym.olb中复制一个TitleBlock0到自己创建的库的路径下,选中这个元件,按Ctrl+C进行复制,然后复制到自己创建的库路径下,如图2-33所示: 图2-33 复制系统自带库示意图第二步,将复制的Title

全站最新内容推荐

- 1加码技术,打破困境,PSPice电路仿真助你解锁职场新高度!

- 2简谈稳压二极管和普通二极管的区别

- 3贴片元件如何拆卸及焊接?

- 4盘点电子工程师必须了解的21个电路

- 5英伟达GB300芯片受阻,存在过热问题

- 6WARELEO李增原创H04课程大纲的安排课程中内容及工具及课程的重点学习办法的讲解

- 7WARELEO李增原创H03根据自己的关注知识点和所需要的知识来选择需要的图书包邮递

- 8WARELEO李增原创H02理工男生李老师的介绍从51单片机驱动到FPGA到仿真设计之路

- 9WARELEO李增原创H01信号电源完整性设计与HFSS射频天线设计仿真验证研修课程主题

- 10WARELEO李增:反射仿真的信号观察办法及时域串扰的仿真设置及观察技巧

扫码关注

扫码关注