- 全部

- 默认排序

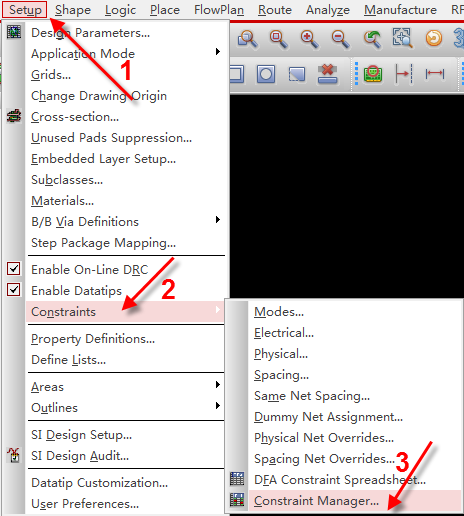

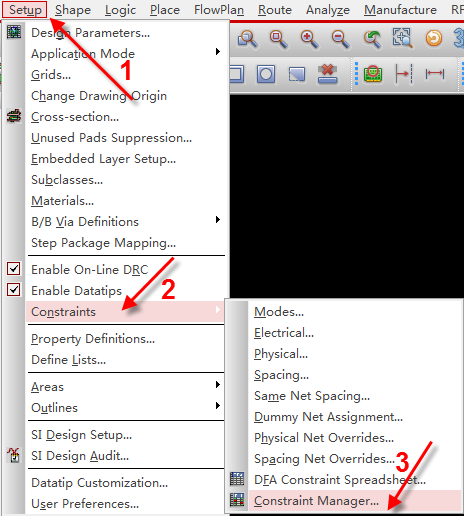

答:我们在设计完成以后,都需要对一组传输的总线进行时序等长,在做时序等长的时候,分为绝对传输延迟与相对传输延迟。绝对传输延迟,顾名思义,信号传输在PCB设计中都是有一个走线的长度,我们通过设置这个信号线传输的最大值与最小值,来实现等长的方法,就称之为绝对传输延迟。一般情况下如果信号是从一个点传输到另一个点,中间没有任何的串阻、串容,这个绝对传输延迟的方法还是非常有效而却直观的。具体在PCB中设置绝对传输延迟的方法如下所示:

答:在5.34问中,我们讲述了什么是相对传输延迟。这里呢,我们来具体讲述一下,怎么去添加相对传输延迟的等长规则,首先讲述的是通过直接添加法去添加,直接添加法只适用于点对点的传输模式,中间没有任何串阻、串容的情况,具体操作如下所示:

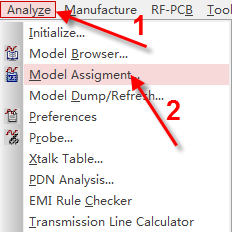

答:所谓的Xnet,是指在无源器件的两端,两个不同的网络,但是本质上其实是同一个网络的这种情况。比如一个源端串联电阻或者串容两端的网络。在实际设计情况中,我们需要对这种进行Xnet的设置,方便进行时序等长的设计,一般信号传输要求都是信号的传输总长度达到要求,而不是分段信号等长,这时采用Xnet就可以非常方便的实现这一功能,在Allegro软件中添加xnet的具体步骤如下所示:

USB 接口 静电整改

#凡亿7月星企划#手持设备,打USB接口静电时,发现异常,于是开始整改,设备整体如下:塑料外壳,没法接大地,只能将静电引入PCB的参考地或者堵住。先看下原理图,VBUS /D+/D-/ID 脚都加了TVS防护静电,信号上也加了串阻。再看下

Xnet关联网络

部分网络在原理图设计时需要添加串阻等器件进行信号阻抗匹配,此时,需要将串联器件2端网络进行关联,以方便等长规则设置。1)执行菜单命令命令“设置-电气网络”,打开对应的电气网络对话框,如图5-144所示。图5-144“电气网络”菜单命令2)在

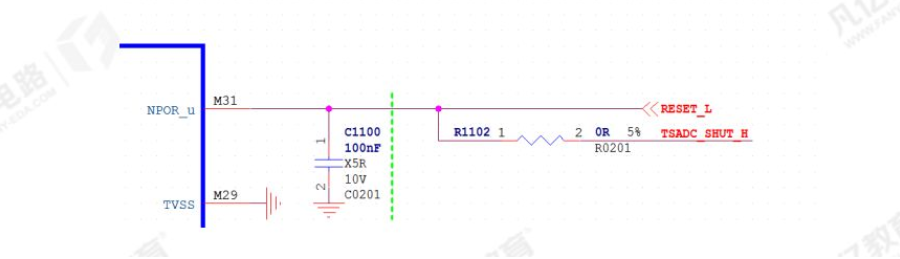

Reset复位电路的PCB布局布线要求—来源:瑞芯微RK3588 PCB设计白皮书Reset复位电路是一种用来使电路恢复到起始状态的电路设计,一般简单的复位电路由电容串阻电阻构成,再复杂点就有三级管等配合进行,RK3588内置复位电路,如下

扫码关注

扫码关注