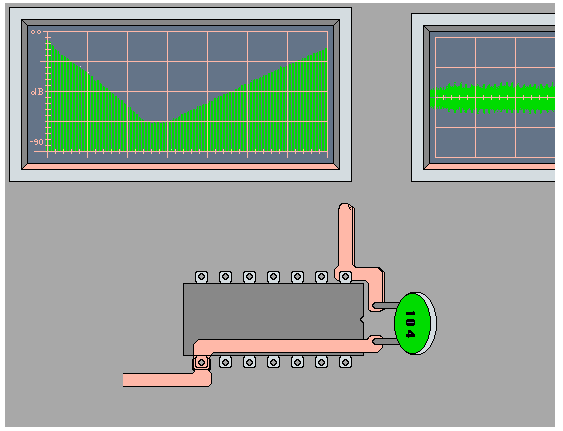

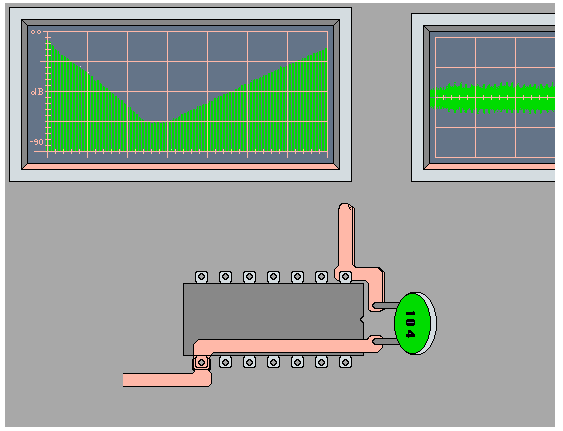

首先观察一个动图,了解去耦的概念以及一些注意事项,然后再对四个选项进行分析。

在电源引脚放置100nF的电容能够有效抑制电源上的噪声; “电源-去耦电容-地”三点一线的距离越近,则去耦的效果越好; 等容值SMD封装的电容比直插电容去耦效果好; 电源平面和地平面可以进一步降低电源噪声。

首先观察一个动图,了解去耦的概念以及一些注意事项,然后再对四个选项进行分析。

RTOS,实时系统(Real-time operating system),实时系统能够在指定或者确定的时间内完成系统功能和外部或内部、同步或异步时间做出响应的... 详情>>

2024-03-27 11:20:23

作者:电子硬件攻城狮链接:https://www.zhihu.com/question/379341025/answer/2367344052来源:知乎著作权归... 详情>>

2023-11-27 11:02:57

static 全局变量与普通的全局变量有什么区别?static 局部变量和普通局部变量有什么 区别?static 函数与普通函数有什么区别? 全局变量(外... 详情>>

2023-09-09 16:44:19

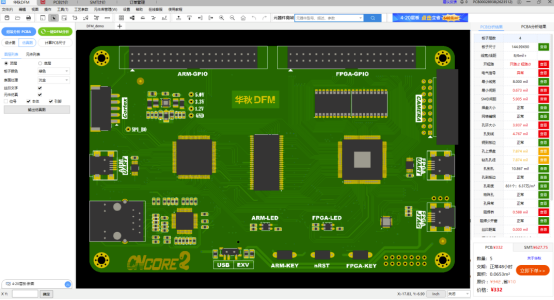

华秋DFM软件最新版→下载地址电子产品的Bill of Materials是一简单而又繁琐的工作,零件繁多,稍有不慎就可能会导致采购错误的元器件, 人工匹配,出... 详情>>

2024-03-29 09:41:17

1系统内核小。2专用性强。3系统精简。4高实时性的系统软件(OS)是嵌入式软件的基本要求。而且软件要求固态存储,以提高速度;软件代码要求高质量和 高可靠性。5嵌... 详情>>

2024-03-27 11:15:11