原理图设计完成后,需要将原理图中的设计内容导入到PCB中,以方便后续PCB设计工作,PADS Logic与layout进行同步过程,可以完成。

1)执行菜单栏命令“工具”→“PADS Layout链接”或者点击快工具栏的快捷键,点击完成会弹出“PADS Layout链接”界面,如图4-59所示。一般进行同步操作时会打开原理图和对应的PCB,且只打开一个,不打开多个,以免出现同步文件错误。同步操作之前须先指定封装库内容,将对应的封装库顺序移到封装库列表最上方

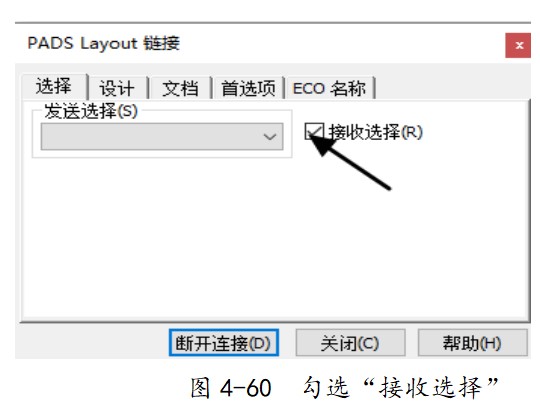

PADS Layout链接界面包含5个标签页:分别是选择、设计、文档、首选项、ECO名称。

l 选择标签页:勾选“接收选择”选项,可以使Layout中选择的元件对应在Logic中也为高亮状态,一般需要勾选,如图4-60所示。

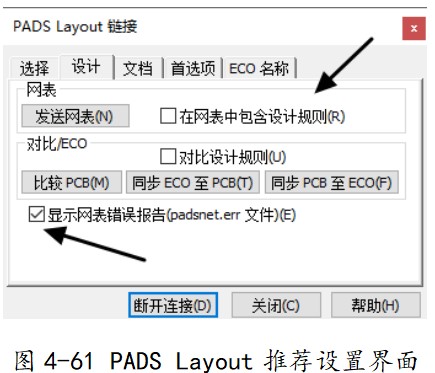

设计标签页:主要实现PADS Logic与layout之间的更新,建议不勾选“在网表中包含设计规则”和“对比设计规则”,设计规则一般会在后续的PCB设计时在Layout组件或者Router组件进行设置,不会在原理图中设置。勾选“显示网表错误报告”,如图4-61所示。

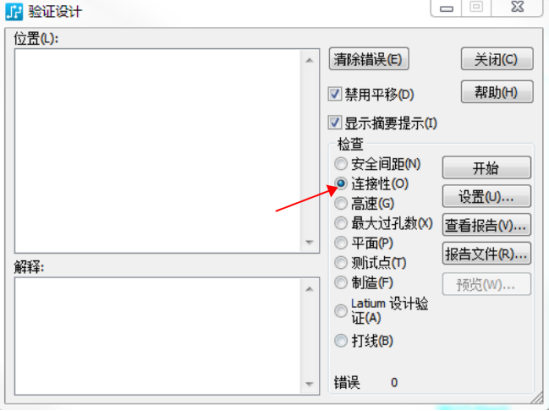

此页面包含三个ECO的操作按键,主要是下面三个:

① 比较PCB:比较Logic与Layout中是否有差异,如果有,会弹出一个TXT文本提示差异列表。

② 同步ECO至PCB:将Logic中的ECO更新到Layout中,是常用的同步功能按键。

③ 同步PCB至ECO:将Layout中的ECO更新到Logic,一般此功能不用。

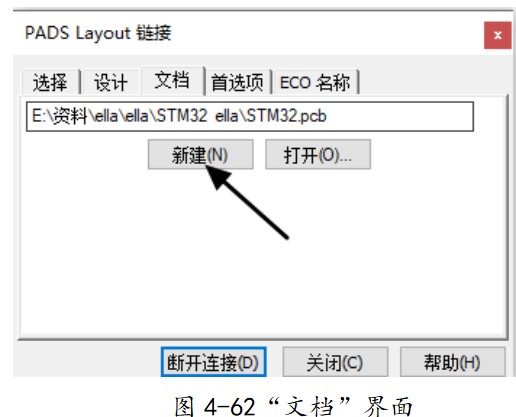

l 文档标签页:文档标签页显示的是用与Logic链接的对应PCB文档名称及其路径,也可以用鼠标左键单击“新建”选项,新建PCB进行导网表操作,如图4-62所示。

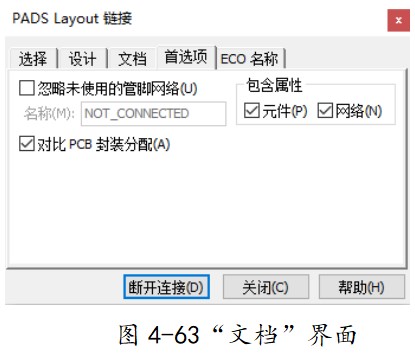

l 首选项标签页:必须勾选“对比PCB封装分配”“元件”“网络”三个选项,“忽略未使用的管脚网络”项可不勾,不影响。如图4-63所示。

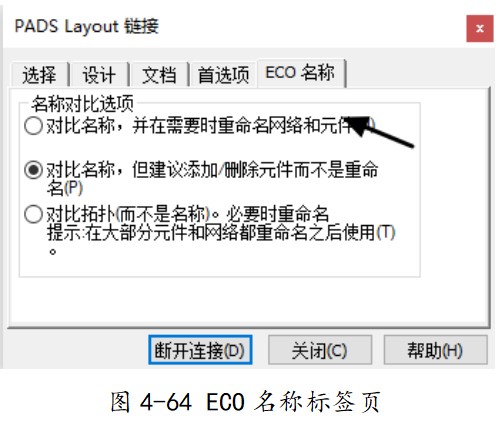

l ECO名称标签页:“对比名称,并在需要时重命名网络和标签页”选项在首次导入网表时需要勾选。如原理图在设计过程中有修改需要更新到PCB时,需要勾选“对比名称,但建议添加/删除元件而不是重命名”,第三项一般不使用。如图4-64所示。

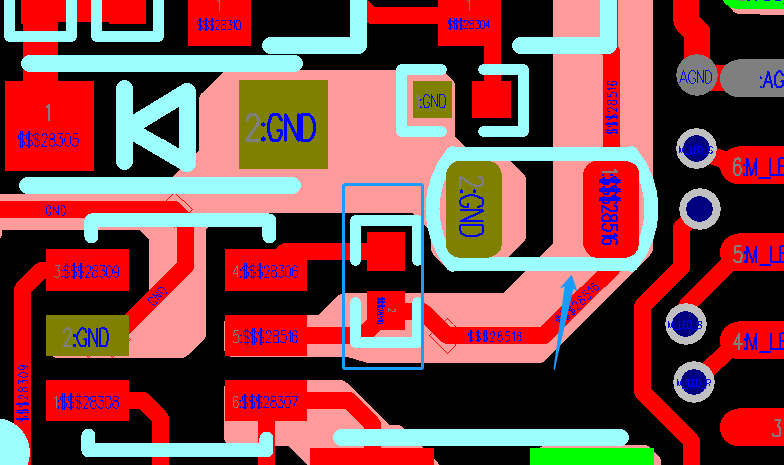

PADS Logic与layout同步过程:首先按上示把5个标签页设置好,把选项勾上,然后在“设计”界面点击“发送网表”按键,完成后再点击“同步ECO至PCB”按键将原理图同步到Layout里,最后点击“比较PCB”按键查看是否有未同步过去的内容,若有,会有报告弹出。

扫码关注

扫码关注

![电子设计:时域处理知识小结 [学以致用系列课程之数字信号处理]](https://api.fanyedu.com/uploads/image/fe/99e439f4b2c8deac5efb272581d4db.png)