近年来,随着科技迭代速度加快,EMC设计已成为电子工程师必备技能之一,但有很多人不清楚,在面对不同的电子产品或系统该如何进行EMC设计,所以本文将回答这个问题。

EMC设计,简单地说,就是预测可能发生的各种EMC问题,进行方案和电路的优化选型,寻找一种优化电路、机械结构和PCN的设计解决方案,提高产品的设计质量,确保达到功能和性能指标的情况下,兼顾成本效益,避免EMC问题。

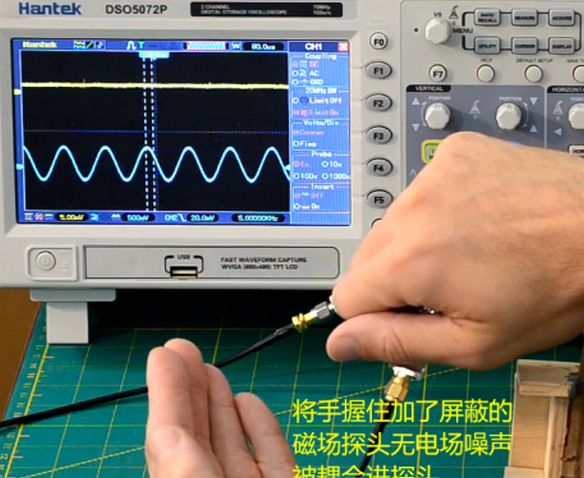

为抑制和消除骚扰源,减小高频信号频率、减小高频电流回路面积、减小共阻抗耦合或感应耦合,选用低速、低辐射器件,选用屏蔽机箱、屏蔽电缆和I/O滤波器是常用的措施,一般来说,EMC设计可分为五个层次。

1、方案选择、主要部件、集成电路的选型、电路和机械结构设计

对于产品的成功与否,第一层次设计是最基本、最重要的,任何错误都意味着该产品项目彻底失败。这一层主要EMC考虑体现在:

对于产品的成功与否,第一层次设计是最基本、最重要的,任何错误都意味着该产品项目彻底失败。这一层主要EMC考虑体现在:

①方案选择、主要部件、集成电路的选型主要考虑减少辐射骚扰或提高射频辐射抗干扰能力,尽量选用本身发射小的芯片,如翻转时间长、工作速率低的器件,多地线脚的芯片(芯片实质就是集成度较高的电路模块,封装时多装地线脚,可以减小高速差模电流环面积S,相应地减小芯片的发射);避免使用大功率、高损耗器件,它们往往是大的辐射源

②保证所选器件不工作在非线性区,以免产生谐波分量成为干扰源。

③电路和机械结构设计除考虑减少辐射骚扰或提高射频辐射抗干扰能力外,主要考虑电源电路防外部骚扰包括浪涌、快速脉冲群、静电、电压跌落、电压变化等;

④电路设计或方案应不使数字信号波形产生过冲,应使无用的谐波振荡幅度最小,使无用的高次谐波成分最少,避免引发强烈的电磁骚扰;

⑤对集总参数电路,增加阻尼、减小Q值,防止振荡;

⑥电路设计或方案应不使数字信号波形产生过冲,应使无用的谐波振荡幅度最小,使无用的高次谐波成分最少,避免引发强烈的电磁骚扰;

⑦对集总参数电路,增加阻尼、减小Q值,防止振荡;

2、PCB的EMC设计

对于产品的成功与否,PCB的EMC设计是重要的一环。PCB设计不合理,会产生无法补救的后果;PCB良好的EMC设计,有事半功倍的效果。PCB的EMC设计应遵循以下内容:

①尽量减小所有的高速信号及时钟信号线构成的环路面积,连接线要尽可能短,并使信号线紧邻地回路;

②使用小型化器件和多层线路板,多层印制板可紧缩布线空间,高频特性好,容易实现EMC;

③印制板层数选择考虑关键信号的屏蔽和隔离要求,先确定所需信号层数,然后考虑成本的前提下,增加地平面和电源层是PCB EMC设计最好的措施之一;

④印制板分层原理与布置印刷电路、布置排线的原理一样,元件面下面为地平面,关键电源平面与其对应的地平面相邻,相邻层的关键信号不跨区,所有的信号层特别是高速信号、时钟信号与地平面相邻,尽量避免两信号层相邻;

⑤个别电源层、地层不能作为一个连续的平面时,采用多网孔连接形成地格蜂窝网,有效减小电流环路面积,减小公共阻抗R,加大信号与地层分布电容;

⑥线路板布线设计时顺序考虑:电源和地/时钟线/信号线,布线应该短、直、粗、匀,不要直角和突变,不应有“之”字形,用圆角代替尖锐走线,尽可能加宽电源和地的布线,电源和地层的分割,尽量符合微带线和带状线要求;

⑦走线尽可能远离骚扰源,布线考虑铁氧体材料的使用,预留磁珠和贴片滤波器的位置,以备按需加减;

由于文章篇幅所限,将此文分为上下两篇,欲看下篇可点击《不同产品系统如何进行EMC设计?(下)》。

扫码关注

扫码关注

![电子设计:时域离散系统的网络结构[学以致用系列课程之数字信号处理]](https://api.fanyedu.com/uploads/image/22/60c44e92fd54d2c18ebf300907108e.png)