在日常的电源设计中,半导体开关器件的雪崩能力、VDS电压降额设计是工程师不得不面对的问题,本文旨在分析半导体器件击穿原理、失效机制,以及在设计应用中注意事项。

一、半导体器件击穿原理

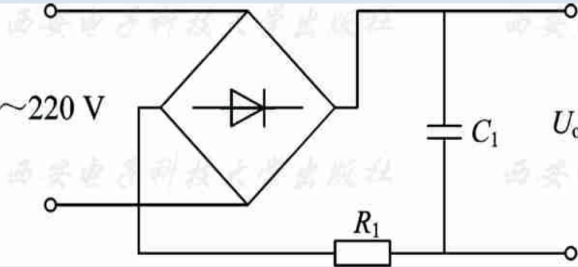

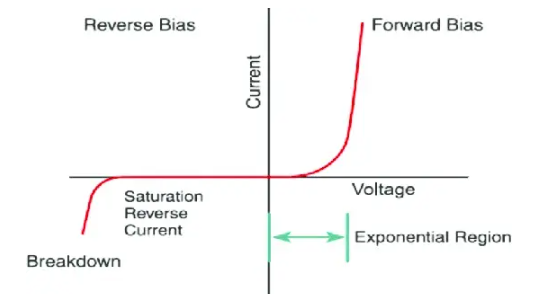

PN结I-V曲线如图[1]所示:

PN结正向导通,反向截止;

反向电压超过一定限值VBR,器件发生电击穿;

正向导通时,电流超过一定限值(图示绿色区域之外),器件发生热烧毁。

图[1]:PN结I-V曲线

PN结的击穿原理分为:电击穿和热击穿(二次击穿)。

1)电击穿

电击穿:指强电场导致器件的击穿,过程通常是可逆的。当电压消失,器件电学特性恢复。电击穿又分为:

a)雪崩倍增效应

雪崩倍增效应:(通常指电压>6V时发生,)原理如下:

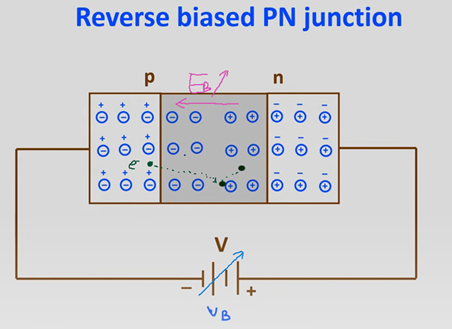

图[2]:PN结反偏示意图

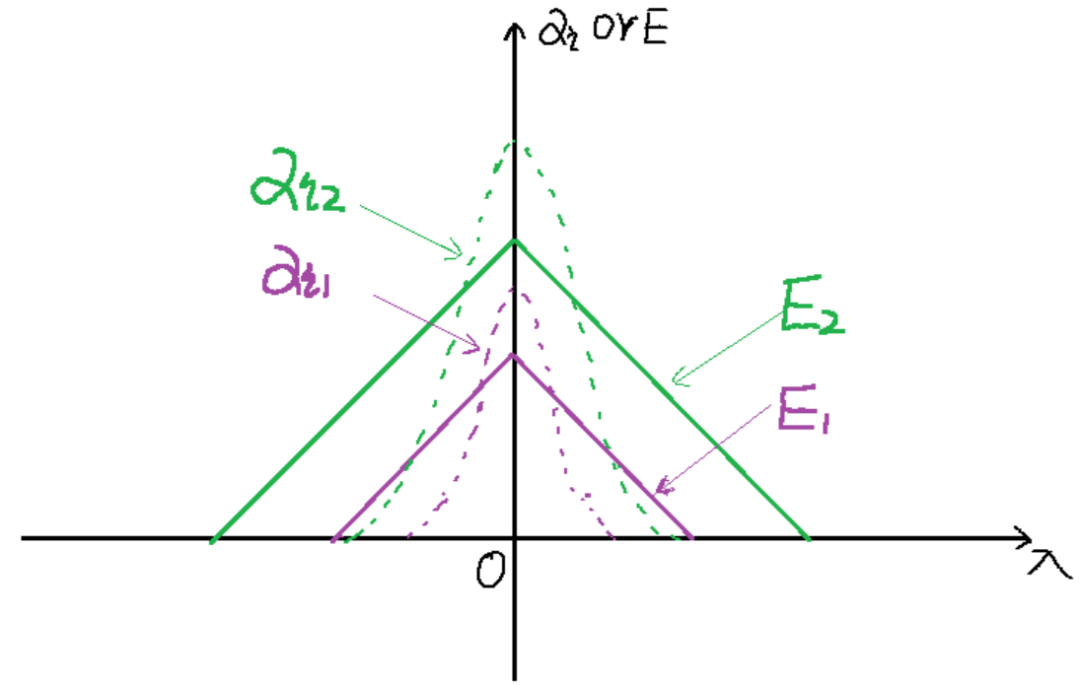

如图[2]所示:在PN结两端加反向电压,随着反向电压增加,PN结耗尽区反向电场增加,耗尽区中电子(或者空穴)从电场中获得的能量增加。当电子(或者空穴)与晶格发生碰撞时传递给晶格的能量高于禁带宽度能量(Eg),迫使被碰撞的价带电子跃迁到导带,从而产生一堆新的电子空穴对,该过程叫做碰撞电离;课本里把一个自由电子(或者空穴)在单位距离内通过碰撞电离产生的新的电子空穴对的数目称为电子(或者空穴)的碰撞电离率,表示为αin(or αip)。

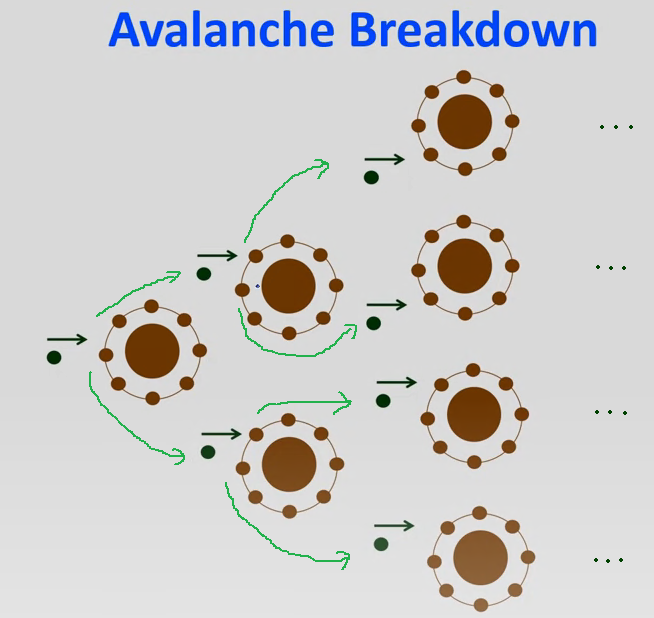

当耗尽区电场增加到一定程度,碰撞电离激发出的新电子-空穴对,即“二次载流子”,又可能继续产生新的载流子,这个过程将不断进行下去,称为雪崩倍增。如果由于雪崩倍增效应导致流出PN结的电流趋于无穷大,则发生了所谓的雪崩击穿,该过程简单示意如图[3]所示。

图[3]:雪崩击穿示意图

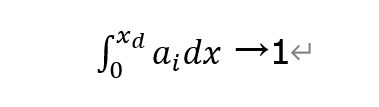

发生雪崩击穿的条件是:

其物理意义是碰撞电离率在整个耗尽区积分趋于1。由于αi随电场的变化强相关(如图[4]所示),因此可以近似的认为当耗尽区最大电场EMAX达到某临界电场Ec时,即发生雪崩击穿。Ec与结的形式和掺杂浓度有一定关联,硅PN结典型值为Ec = 2×105 V/cm。

图[4]:电场的强相关函数图

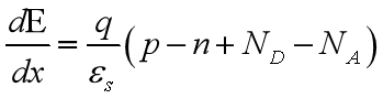

为了更好地理解PN结电场强度Ec随耗尽区XD的关系,我们在这里简单讨论下泊松方程:在一维情况下(PN结/BJT)泊松方程的表达形式为:

等式右边第一项“q”为电荷量,介电常数“εs”为电通量密度与电场的映射关系,括号内表示自由离子的加和。从直观来看,该式反映电场(或者电通量密度,两者从某种角度上可以理解为反映着同一种东西)的源是电荷,如果是记公式:泊松方程表示的是,单位体积内对电通量密度(电位移)求散度,结果为体积内的电荷。除了从电磁学理论出发的分析,该式从数学上也可以看成是:电场与位置的函数关系。通过解泊松方程,便可以得到随着位置变化时,电场、电势的变化情况。

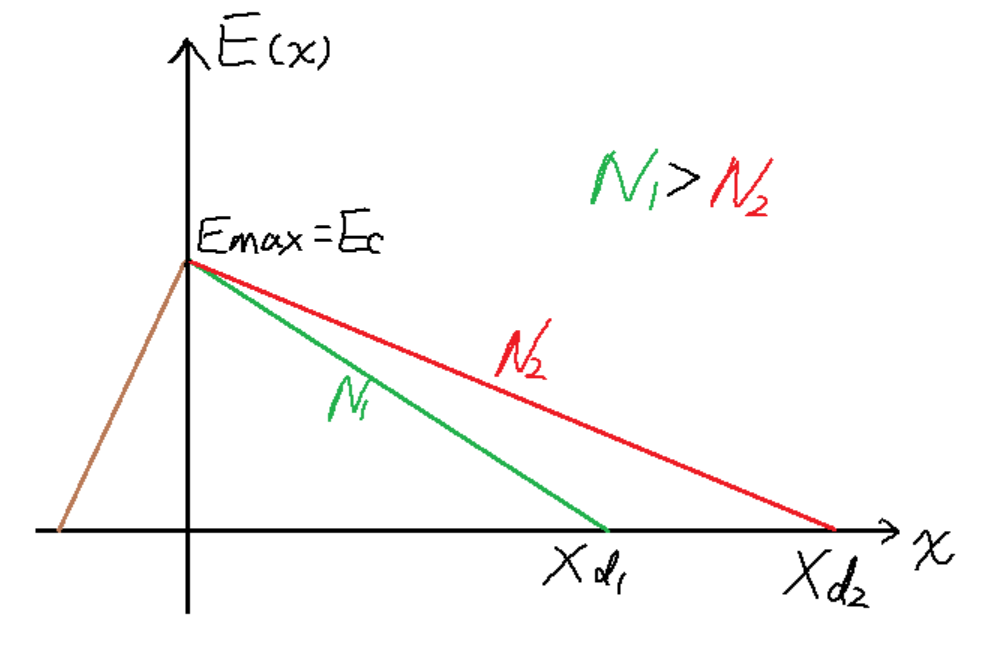

接下来我们通过举例来看击穿电压VB与哪些因素相关:图[5]所示为两种掺杂浓度材料的Ec VS Xd曲线关系(其中,N1>N2)。

图[5]不同掺杂浓度Ec VS Xd曲线关系

分析该图可知:

禁带宽度Eg越大,则击穿电压VB越高;比如Si (Eg=1.12 eV) VS SiC (Eg=3.23 eV)

掺杂浓度越低,VB越高;

击穿电压主要取决于低掺杂一侧,该侧的杂质浓度越低,则VB越高。

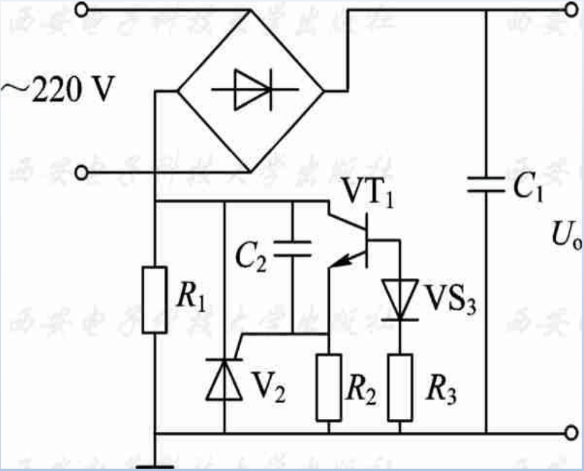

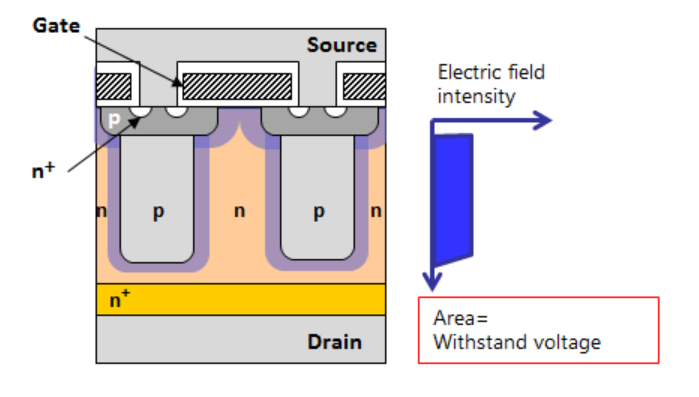

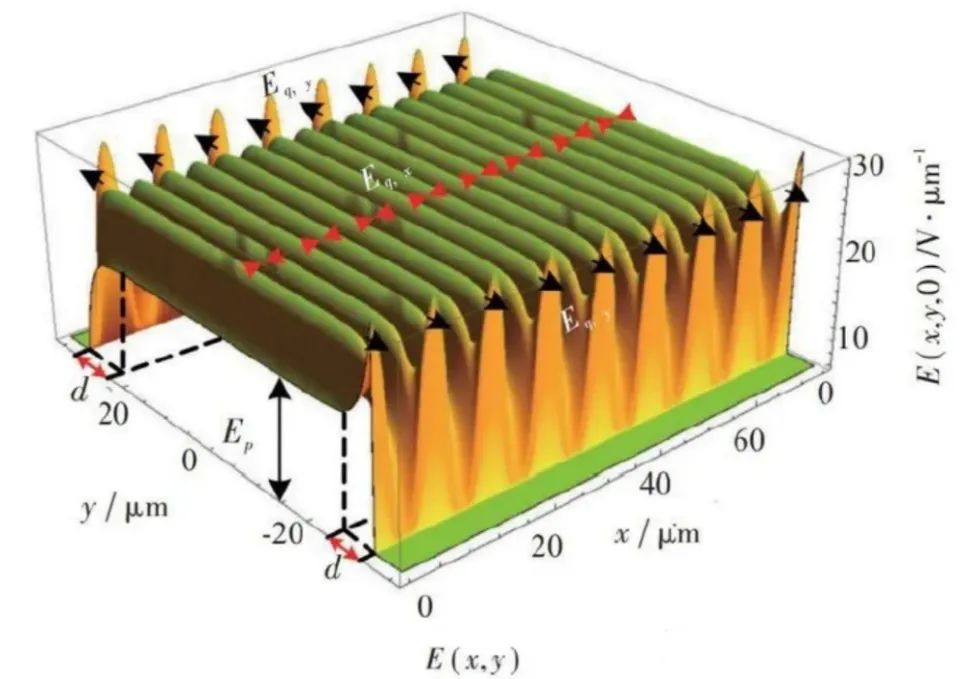

除了上述方法可以提高击穿电压VB,还可以通过增加电场维度,改变电场强度分布(如图[6]、图[7]所示):比如英飞凌的CoolMOSTM系列产品,通过在N-耗尽区掺入P柱结构(引入横向电场分布),大幅提高VB。这里不再赘述其机理,感兴趣的读者可在英飞凌官网查阅相关文献资料。

图[6]SJ MOSFET剖面示意图

图[7]SJ MOSFET内部电场仿真示意图

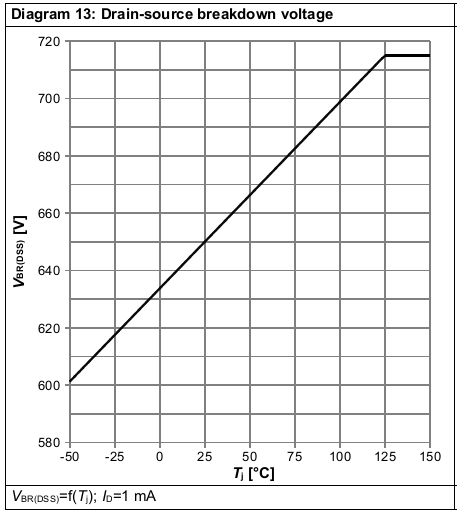

综上所述,PN结的雪崩击穿电压VBR还与PN结结温(Tj)呈现正相关性(如图[8]):

图[8]:IPL65R065CFD7 VBR(DSS) VS Tj

其主要原因是:随着温度升高,晶格振动加剧,价带电子跃迁到导带需要的能量Eg更高,因此需要更强的电场。

b)隧道效应

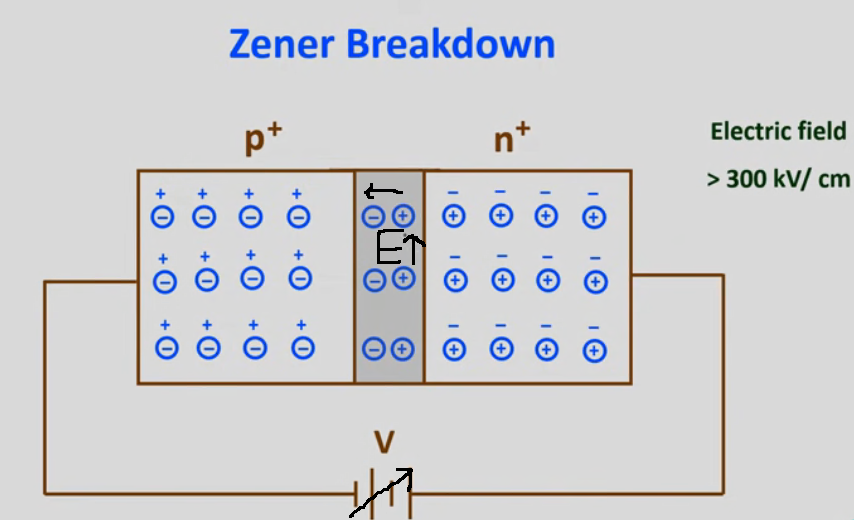

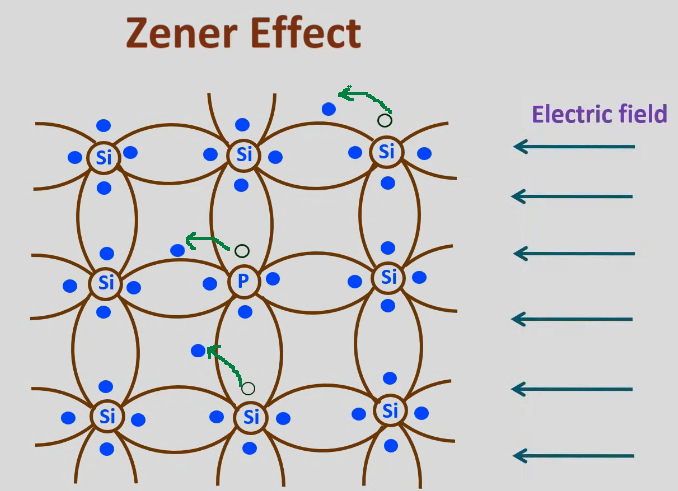

隧道效应又称为齐纳击穿、隧道穿通,(一般发生在击穿电压VB<4v时,)其原理如下:<>

图[9] PN结电压反偏示意图

将两块重掺杂的P、N半导体材料结合在一起,由于耗尽区两侧P 、N载流子浓度更高,因此形成耗尽区宽度,较普通PN结更薄,耗尽区带电离子浓度更高,内建电场Eb更强。当在PN结两端加反向偏压如图[9]所示,该电压产生的电场与内建电场同向叠加,当耗尽区电场强度>300kV/cm时,电子空穴对在电场力的作用下挣脱原子核束缚,自由的穿过耗尽区,形成电流。顾名思义:叫做隧穿效应,该过程微观过程如图[10]所示。当PN结两端反向电压进一步增加时,流过PN结电流增加,电压基本保持不变。齐纳二极管(稳压二极管)即是利用该效应制作的一种稳压元器件。

图[10] 隧穿效应示意图

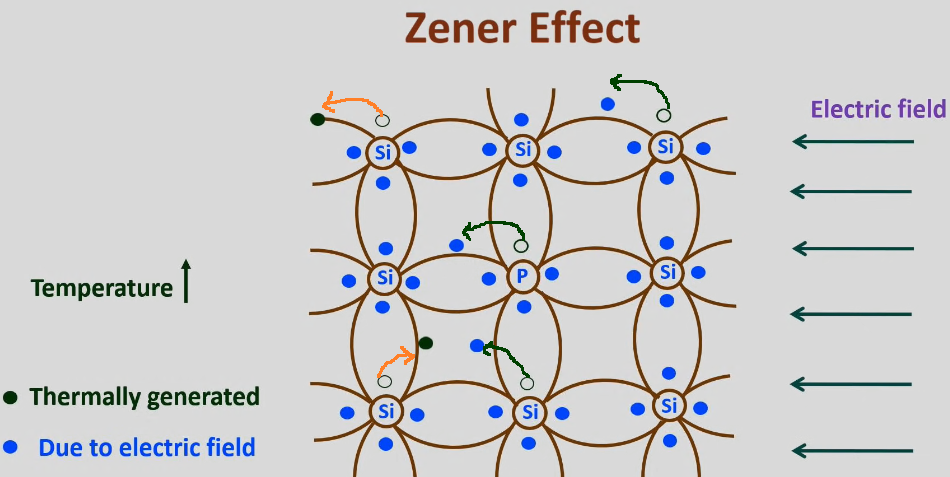

由于隧穿效应的导电离子是来自于挣脱原子核束缚的电子(或者空穴),因此,随着温度的升高,PN结内部产生热电子浓度增加,进而导致击穿电压VB降低,使得宏观上击穿电压VB呈现负温度特性。该过程微观示意如图[11]。

图[11] 隧穿效应VS温度示意图

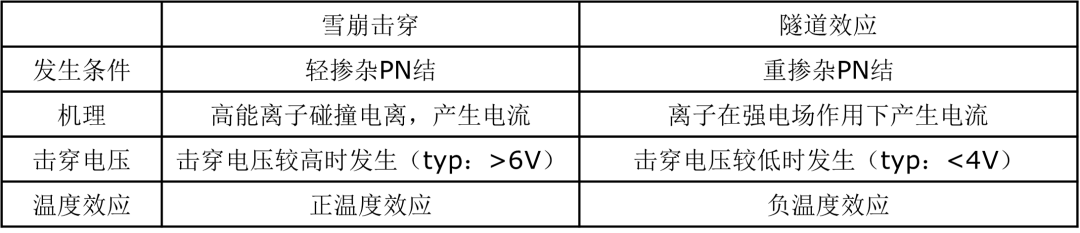

在这里简单的对两种电压击穿做对比总结以方便读者记忆:

2)热击穿(二次击穿)

热击穿(二次击穿)指器件由于过电压、过电流导致的损坏,结果不可逆。通常情况下是先发生了电击穿,产生的高压大电流没有得到及时控制,进一步导致过热使得器件发生烧毁。

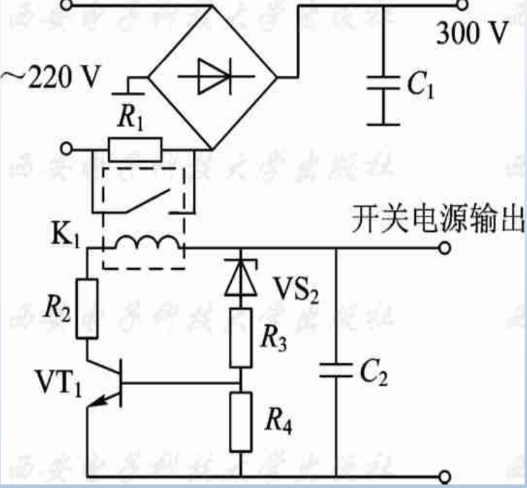

二、设计应用注意事项

通过以上分析,我们可以得出结论:对于硅材料的半导体功率器件(碳化硅材料器件由于其原理、结构与硅材料相似,因此有着相似的物理规律,这里不再做分析,氮化镓器件由于其器件结构与传统硅差别较大,因此不具备类似的规律,后续文章可以涉及,敬请关注),在驱动电压Vgs可控的情况下,主要失效模式两种:

一种是:过电压应力导致器件发生雪崩,雪崩过程本身是可逆的,但如果由于雪崩行为没有被及时控制,导致器件出现过热,进一步导致器件封装烧毁、bonding材料或者结构毁坏、甚至芯片半导体结构损坏,该过程不可逆。

第二种是:过电流应力导致器件温升超过其极限值,进一步导致器件封装烧毁、bonding材料或者结构损坏、甚至芯片半导体结构破坏,该过程亦不可逆。

因此,我们在设计使用半导体功率器件电路时,必须严格的遵照相关的标准(例如IPC9592B-2012),规范化降额设计,以保证产品在整个生命周期内,半导体器件可以运行在规格书的范围内,以显著降低产品的失效率。更多的关于半导体器件雪崩设计应用指南请参考英飞凌应用笔记:AN_201611_PL11_002,本文不再赘述。

后记

随着半导体产业竞争趋于白热化,在半导体器件设计中,一个不争的事实:对于相同的技术下,Rds(on)越小,芯片尺寸越大,器件热阻越小,抗雪崩能力越强。但是对于半导体器件来讲,并不是芯片尺寸越大越好,更大的尺寸意味着更大的寄生参数,更大的开关损耗,因此限制了电源朝着高频高密的方向发展以进一步降低系统成本。因此,在设计器件过程中,需要综合性的权衡各项参数,以设计出综合能力更全面的产品。英飞凌公司作为全球功率器件的领头羊,一直致力于设计更全面的产品以完成其“低碳化”的使命!

扫码关注

扫码关注