之前我们分析了信号完整性和电源完整性,引起了很多读者的积极反响,所以今天来更新该系列的下篇,谈谈它们的重要因素,小伙伴要是想看上篇,可点击右侧链接《走进了解信号完整性和电源完整性(上)》。

3、信号的振荡和环绕

振荡和环绕的表现形式是信号反复出现过冲和下冲,在逻辑电平的门限上下抖动,振荡属于欠阻尼状态,而环绕属于过阻尼现象,信号的振荡和环绕主要是由传输线上过渡的寄生电感和电容引起终端和源端的阻抗均衡失配所造成的。通常周期脉冲信号(如时钟信号)包含丰富的高次谐波而容易发生信号完整性故障,振荡和环绕同反射一样也是由多种因素引起的,可通过适当的端接子抑制,但无法完全消除。

4、信号延迟

信号延迟是表明数据或时钟信号没有在规定的事件内以一定的持续时间和幅度到达终端。由于集成电路是按规定的时序接收数据,过长的信号延迟可能导致时序违背和功能混乱。信号延迟是由驱动过载、走线过长的传输线效应引起的。传输线上等效电容、电感会对信号的切换产生延迟,影响集成电路的建立时间和保持时间,延迟足够长会导致集成电路无法正确判断数据。

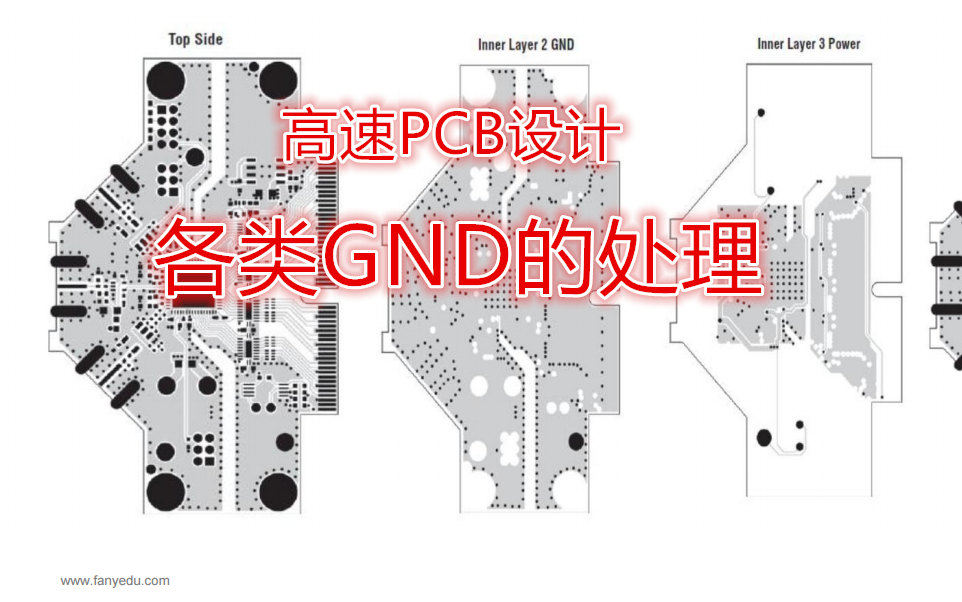

5、地电平面反弹噪声和同步切换噪声

接地反弹指由于电路中较大的电流涌动在电源与接地平面间产生大量噪声的现象(简称为地弹)。同步切换噪声是指大量芯片同步切换时,会产生一个较大的瞬态电流从芯片与电源平面间流过,芯片封装与电源平面间的寄生电感、电容和电阻会引发电源噪声,使得零电位平面上产生较大的电压波动,也称为Ai噪声。

6、衬底耦合

在硅片设计中,由于衬底具有一定的电阻率,电流通过时会产生压降。而MOSFET管的阅值电压(开启)取决于栅区下面村底的有效电压,底电流产生的压降可能会超过 MOSFET 管的值电压,而且可能会超过逻辑门或时钟电路的闽值电压,使工作很不稳定。随着芯片特征尺寸的减小,衬底的电阻增大,问题更加突出。

7、串扰

串扰是没有电气连接的信号线之间电磁耦合导致的感应电压和感应电流,信号线之间的互感和互容引起线上的噪声。容性糊合引发耦合电流,感性耦合引发耦合电压,并且随着时钟速率的升高和设计尺寸的缩小而加大。

8、EMI

EMI有传导干扰和辐射干扰两种传导干扰是指通过导电体把一个电网络系统上的信号耦合(千扰)到另一个电网络。辐射于扰是指干扰源通过空间把其信号耦合(干扰)到另一个电网络系统。在高速PCB及系统设计中,高频信号线集成电路的引脚、各类接插件等都可能成为具有辐射特性干扰源,影响其他系统或本系统内其他子系统的正常工作。

扫码关注

扫码关注