- 全部

- 默认排序

众所周知,PCB设计总是有一系列原则要遵守,若是不好好照做,可能降低PCB设计的成功概率,影响到产品的性能,甚至信号完整性、电磁辐射的控制及系统可靠性都有一定消极影响,今天本文将针对这些原则进行分析,希望对小伙伴们有所帮助。原则1:高频信号

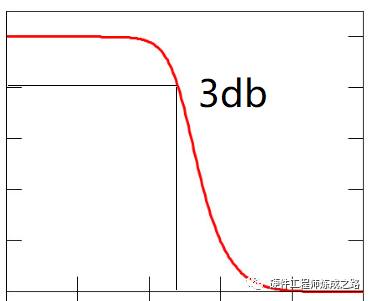

上期说到了换示波器探头,第一次使用需要对探头进行补偿电容的调节。使用示波器还有一个重要的点需要知道,那就是测试高频的时候需要用x10档,而不要用x1挡。这一点可能很多人都知道,但并不一定知道更深一点的原因,那么,我们就来说一说。 无缘高阻示波器探头带宽提一下,示波器探头的带宽也类似一个通滤波器,一般

电源电路为什么要退耦?

电源退耦是电子设计中一项至关重要的技术,旨在优化电路性能,减少信号干扰,确保系统稳定运行。以下直接列出电源需要退耦的具体原因。1、去除高频纹波切断多级放大器间通过电源的高频信号串扰通路。2、降低大信号电源波动影响减少大信号工作时电源波动对输

电源线路详解

下图为一款简单的电源线路图: 电源输入端采用的单级EMI抗干扰电路由C1和L1组成,主要目的就是为了减小电源内的高频信号对电网的辐射干扰。 市电经过整流桥BD1和C2滤波后得到一个大约300V的直流电压,这个电压一路经过变压器的一次绕组后加到开关管VT1的漏极

高频晶振如何隔离?

请问一下板子上有一块高频的有源晶振,但是同一块板子上还有其他的信号,低于晶振100倍~200倍 隔离晶振的话是直接在晶振周围铺一圈铜吗?这个铜是闭合的回路还是不闭合的?网上还有说要在晶振下面铺铜的,不知道应该如何隔离晶振

不还是会要出现从总线上分线头出来的问题所以个人认为在非必要情况下,只要不小于90°,都是可接受的DDR3/4里面,多片FLASH,这种情况很常见

扫码关注

扫码关注