- 全部

- 默认排序

在高速PCB电路设计过程中,经常会遇到信号完整性问题,导致信号传输质量不佳甚至出错。那么如何区分高速信号和普通信号呢?很多人觉得信号频率高的就是高速信号,实则不然。我们知道任何信号都可以由正弦信号的N次谐波来表示,而信号的最高频率或者信号带宽才是衡量信号是否是高速信号的标准。在高速PCB电路设计过程中,经常会遇到信号完整性问题,导致信号传输质量不佳甚至出错

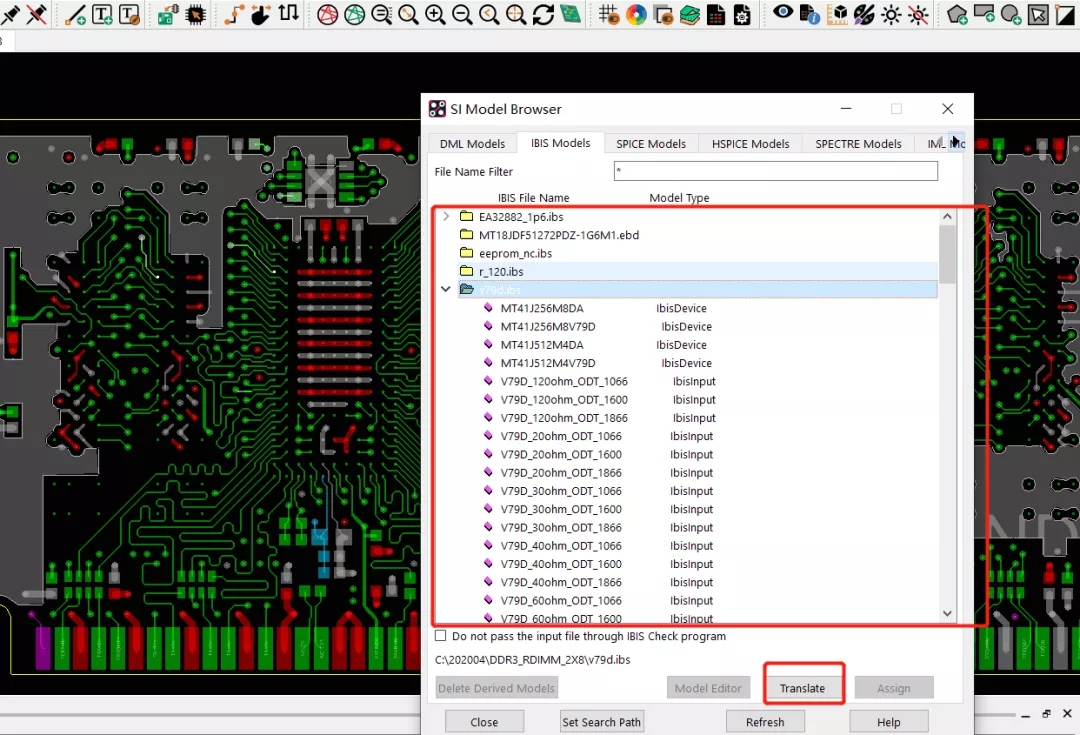

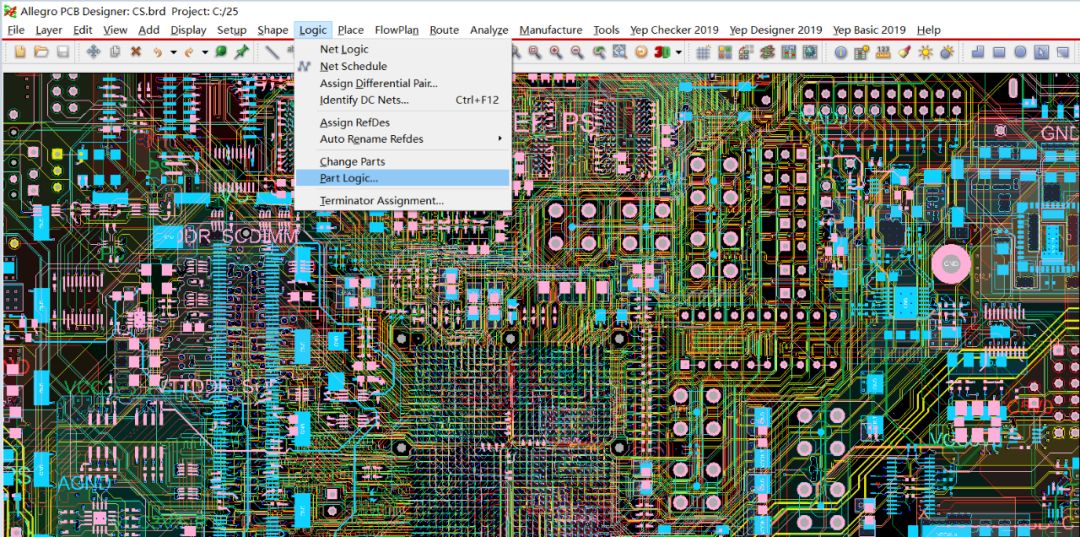

Allegro的全称是Cadence Allegro PCB Designer,是Cadence公司推出的一套完整的、高性能印制电路板设计套件。它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段进行定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。Allegro印制电路板设计提高了PCB设计效率和缩短设计周期,让您的产品尽快进入量产。Allegro是我们目前高速PCB设计中使用最多的工具。

Allegro的全称是Cadence Allegro PCB Designer,是Cadence公司推出的一个完整的、高性能印制电路板设计套件。通过顶尖的技术,它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。Allegro印制电路板设计提高了PCB设计效率和缩短设计周期,让您的产品尽快进入量产(目前高速PCB设计用的最多工具,就是Allegro)。

Allegro的全称是Cadence Allegro PCB Designer,是Cadence公司推出的一个完整的、高性能印制电路板设计套件。通过顶尖的技术,它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。Allegro印制电路板设计提高了PCB设计效率和缩短设计周期,让您的产品尽快进入量产(目前高速PCB设计用的最多工具,就是Allegro)。

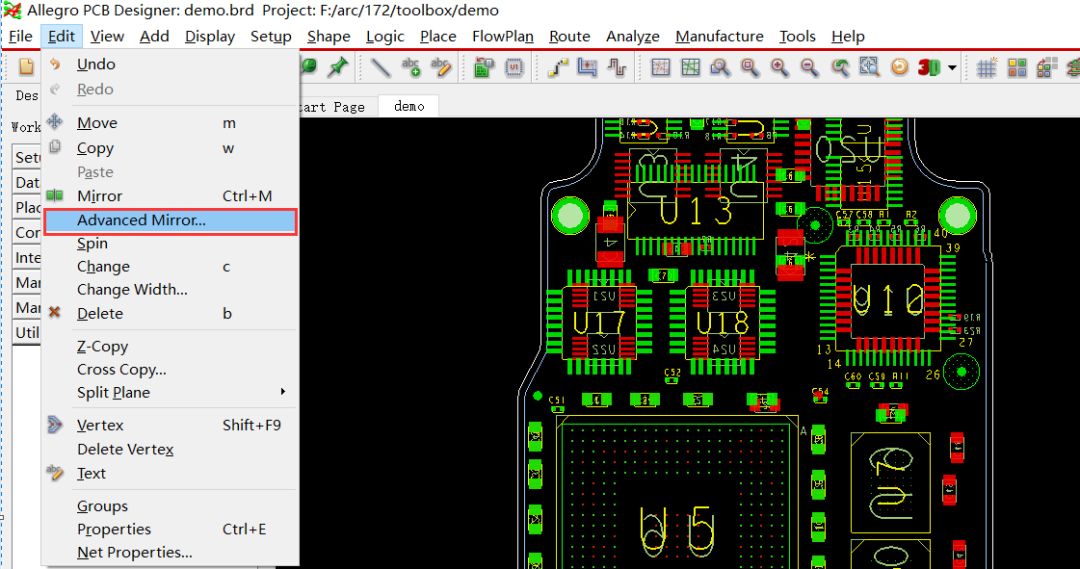

Allegro PCB Designer是一个完整的、高性能印制电路板设计套件。通过顶尖的技术,它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。 在这个专题中,我们将介绍在该套件下的一个Toolbox选项组件下的Advanced Mirror高级镜像功能。

判断一个信号是否为高速信号首先要区分几个误区。误区一:信号周期频率FCLOCK高的才属于高速电路设计其实我们在电路设计时考虑的最高频率往往取决于信号的有效频率(亦称转折频率)Fknee。 如上图信号周期频率与有效(转折)频率定义为:(实际中多数信号)误区二:电容、电感式理想器件在低速领域,电容、电感工作频段比较低,可以认为他们是理想器件。但在高速领域,PCB上的电容电感等已经不能简单的视为纯粹的电容电感了。例如:在低速领域电容我们可以视为断路,而在高速电路中,假设工作频率为F,则电容C

答:我们PCB中的信号都是阻抗线,是有参考的平面层。但是由于PCB设计过程中,电源平面的分割或者是地平面的分割,会导致平面的不完整,这样,信号走线的时候,它的参考平面就会出现从一个电源面跨接到另一个电源面,这种现象我们就叫做信号跨分割。跨分割的现象如图1-52所示。跨分割,对于低速信号,可能没有什么关系,但是在高速数字信号系统中,高速信号是以参考平面作为返回路径,就是回流路径。当参考平面不完整的时候,会出现如下影响:Ø 会导致走线的的阻抗不连续;Ø 容易使信号之间发生串扰;Ø

答:高速信号、低速信号的区分取决于以下两个因素:信号的有效频率F;信号走线的有效长度U。一般来说,信号的有效频率F约等于信号频率的5倍,信号走线的有效长度等于U=(0.35/F)/D,其中D是PCB上的走线延迟,在FR4的材质中D约等于180,得出的结论就是在信号走线的长度小于有效长度的1/6,信号为低速信号;反之,信号为高速信号。所以我们判定信号是否为高速、低速信号的步骤如下:Ø 获取信号的有效频率与信号走线的长度;Ø 计算出信号走线的有效长度;Ø 比较信号长度与

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。等长走线的目的就是为了尽可能的减少所有相关信号在PCB上的传输延迟的差异。高速信号有效的建立保持窗口比较小,要让数据和控制信号都落在有效窗口内,数据、时钟或数

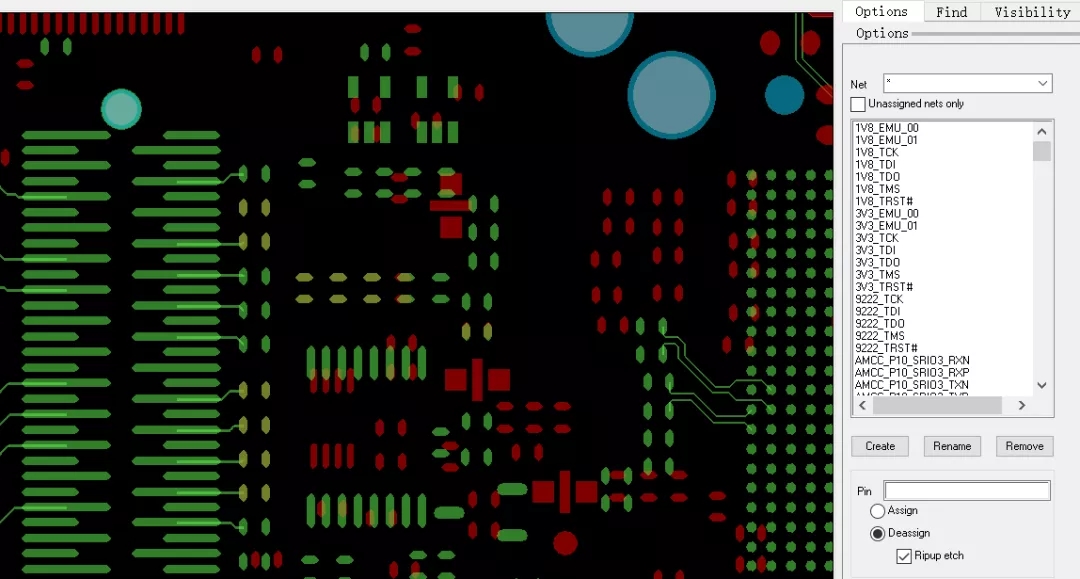

答:我们对于高速信号传输,比如差分信号、一组总线传输,都需要对其进行时序等长处理,在16.6版本以上,Allegro软件推出了自动等长的功能,在空间足够的情况下,是可以采用自动等长的功能,省去手动绕等长的时间,具体操作步骤如下所示:

扫码关注

扫码关注