- 全部

- 默认排序

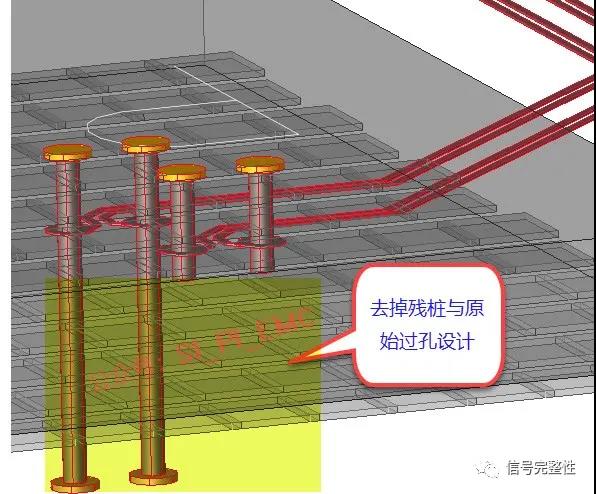

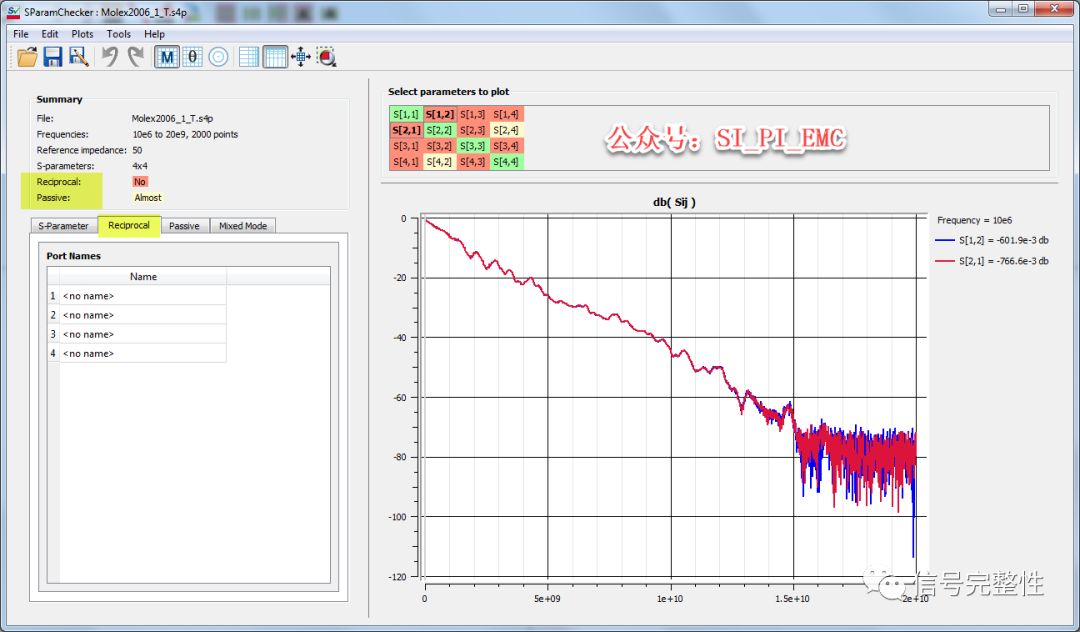

编者注:记得在2017年的时候,起码在不同的场合介绍过孔的相关的内容超过10次,但是从最近遇到一些项目上的问题来看,还是很多人不太了解过孔。本文就给大家介绍下影响过孔性能的因素之一—过孔的残桩。

S参数被大量应用于高速电路和高频电路设计和仿真中。对于越来越高速的电子产品,以及不仅仅是信号完整性和电源完整性工程师需要了解S参数,对于电子工程师、测试工程师和EMC工程师等等都需要了解。

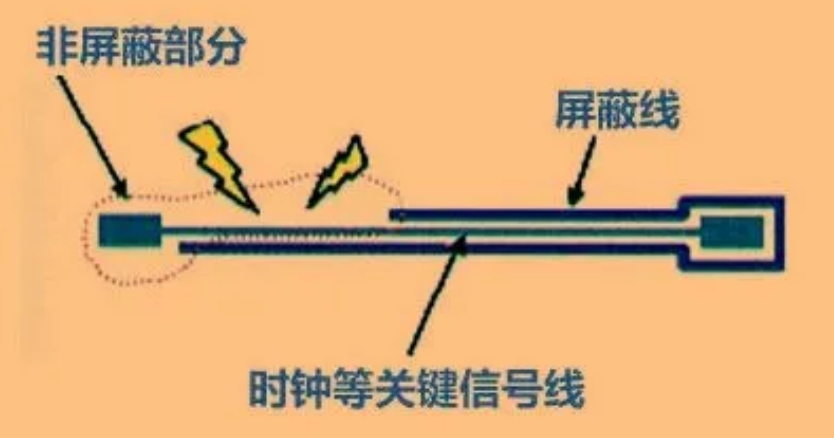

随着信号上升沿时间的减小及信号频率的提高,电子产品的EMI问题越来越受到电子工程师的关注,几乎60%的EMI问题都可以通过高速PCB来解决。以下是九大规则:

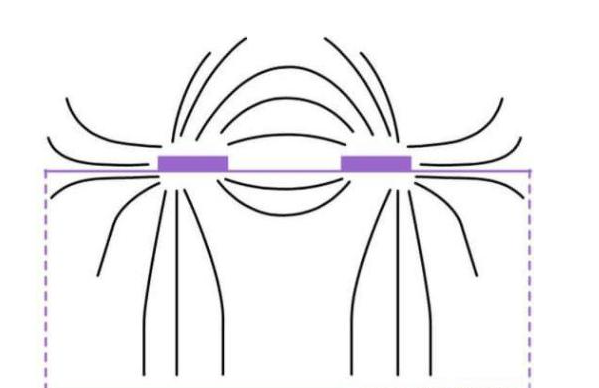

答:串扰,就是指一条线上的能量耦合到其他传输线,它是由不同结构引起的电磁场在同一区域里的相互作用而产生的。串扰在数字电路中非常普遍地存在着,如芯片内部、PCB板、接插件、芯片封装,以及通信电缆等等。 串扰可能是数据进行高速传输中最重要的一个影响因素了。它是一个信号对另外一个信号耦合所产生的一种不受欢迎的能量值。根据麦克斯韦定律,只要有电流的存在,就会有磁场存在,磁场之间的干扰就是串扰的来源。这个感应信号可能会导致数据传输的丢失和传输错误。 所以串扰对

答:我们PCB中的信号都是阻抗线,是有参考的平面层。但是由于PCB设计过程中,电源平面的分割或者是地平面的分割,会导致平面的不完整,这样,信号走线的时候,它的参考平面就会出现从一个电源面跨接到另一个电源面,这种现象我们就叫做信号跨分割。跨分割的现象如图1-52所示。跨分割,对于低速信号,可能没有什么关系,但是在高速数字信号系统中,高速信号是以参考平面作为返回路径,就是回流路径。当参考平面不完整的时候,会出现如下影响:Ø 会导致走线的的阻抗不连续;Ø 容易使信号之间发生串扰;Ø

答:高速信号、低速信号的区分取决于以下两个因素:信号的有效频率F;信号走线的有效长度U。一般来说,信号的有效频率F约等于信号频率的5倍,信号走线的有效长度等于U=(0.35/F)/D,其中D是PCB上的走线延迟,在FR4的材质中D约等于180,得出的结论就是在信号走线的长度小于有效长度的1/6,信号为低速信号;反之,信号为高速信号。所以我们判定信号是否为高速、低速信号的步骤如下:Ø 获取信号的有效频率与信号走线的长度;Ø 计算出信号走线的有效长度;Ø 比较信号长度与

答:高速电路设计中电容的作用有如下几个:Ø 电荷缓冲池。电容的本质是储存电荷与释放电荷,当外界环境变化时,使得驱动器件的工作电压增加或者减少时,电容可以通过积累或者释放电荷来吸收这种变化,即将器件工作电压的变化转变为电容中电荷的变化,从而保持器件工作电压的稳定;Ø 高频噪声的重要泄放通路。高速运行的电路,时刻存在着状态的改变,这些改变将在电路上产生大量噪声干扰,我们需要将这些干扰泄放到相对稳定的地平面上,以免影响器件工作,因为电容在频率较高时表现为低阻抗,所以可以作为泄放通路

答:端接,Butt Joint,是指消除信号反射的一种方式。在高速PCB设计中,信号的反射将给PCB的设计质量带来很大的负面影响,采用端接电阻来达到线路的阻抗匹配,是减轻反射信号影响的一种有效可行的方式。端接,分为一下两类:Ø 源端端接,接在信号源端或信号发送端的端接,一般与信号走线串接;Ø 终端端接,接在信号终端或信号接收端的端接,一般与信号走线并接。源端端接的优点是接供较慢的上升时间,减少反射量,产生更小的EMI,从而降低过冲,增加信号的传输质量。我们在PCB设计中处理源

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。等长走线的目的就是为了尽可能的减少所有相关信号在PCB上的传输延迟的差异。高速信号有效的建立保持窗口比较小,要让数据和控制信号都落在有效窗口内,数据、时钟或数

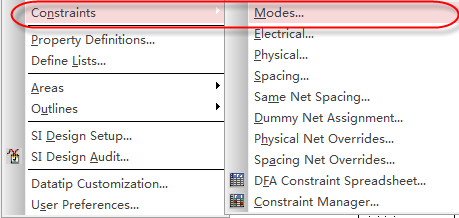

答:我们在时序等长时,除了考虑信号线的走线的长度以外,在高速设计领域里还需要考虑封装本身的引脚长度。所谓封装引脚长度,指的就是元器件封装内部的引脚长度,这个长度一般芯片的厂家会提供这数据,我们要做的就是将数据导入到规则管理器中,与等长一起处理,具体的操作步骤如下:

全站最新内容推荐

- 1加码技术,打破困境,PSPice电路仿真助你解锁职场新高度!

- 2简谈稳压二极管和普通二极管的区别

- 3贴片元件如何拆卸及焊接?

- 4盘点电子工程师必须了解的21个电路

- 5英伟达GB300芯片受阻,存在过热问题

- 6WARELEO李增原创H04课程大纲的安排课程中内容及工具及课程的重点学习办法的讲解

- 7WARELEO李增原创H03根据自己的关注知识点和所需要的知识来选择需要的图书包邮递

- 8WARELEO李增原创H02理工男生李老师的介绍从51单片机驱动到FPGA到仿真设计之路

- 9WARELEO李增原创H01信号电源完整性设计与HFSS射频天线设计仿真验证研修课程主题

- 10WARELEO李增:反射仿真的信号观察办法及时域串扰的仿真设置及观察技巧

扫码关注

扫码关注