- 全部

- 默认排序

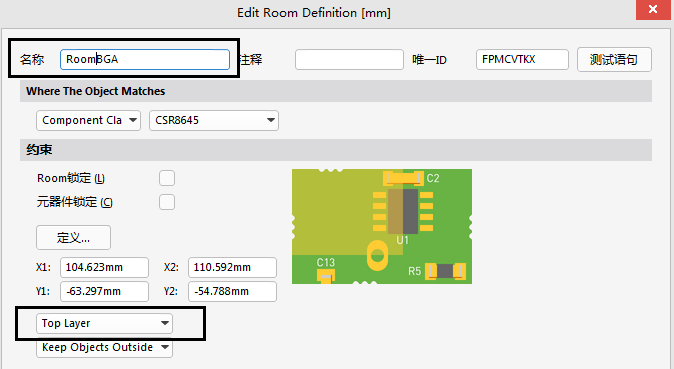

区域(Room)规则设置是针对某个区域来设置规则。为了满足设计阻抗和工艺能力的要求,需要对个别区域设置特殊的线宽走线或者间距或者过孔大小等,这时可以对这个区域进行特殊规则设置,常用于各类不同Pitch间距的BGA。

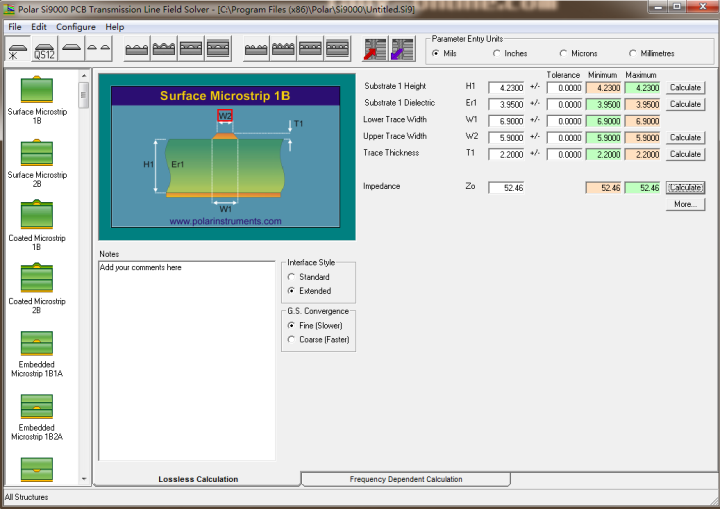

一般来说,影响PCB特性阻抗的因素:介质厚度H、铜的厚度T、走线的宽度W、走线的间距、叠层选取的材质的介电常数Er、阻焊的厚度。一般来说,介质厚度、线距越大阻抗值越大;介电常数、铜厚、线宽、阻焊厚度越大阻抗值越小。这些因素与特性阻抗的关系如图1-20所示。 图1-20 影响PCB特性阻抗分布图第一个:介质厚度,增加介质厚度可以提高阻抗,降低介质厚度可以减小阻抗;不同的半固化片有不同的胶含量与厚度。其压合后的厚度与压机的平整性、压板的程序有关;对所使用的任何一种板材,要取得其可生产的介质

特性阻抗,体现在PCB板上,主要是通过叠层、线宽、线距。在PCB版图布局完成以后,我们要对PCB板进行层叠设计,将PCB板按照一定的厚度叠好以后,根据层叠结构,通过SI9000这个软件来进行阻抗线宽的计算,然后根据计算好的线宽来进行布线,即可达到控制特性阻抗的效果。如图1-21所示,1.6MM的厚度的PCB板的层压结构。TOP0.5oz +PlatingPP(2116)4.23GND021ozCore20.08ART031ozPP(1080*2)4.59PWR041ozCore20.08GND0

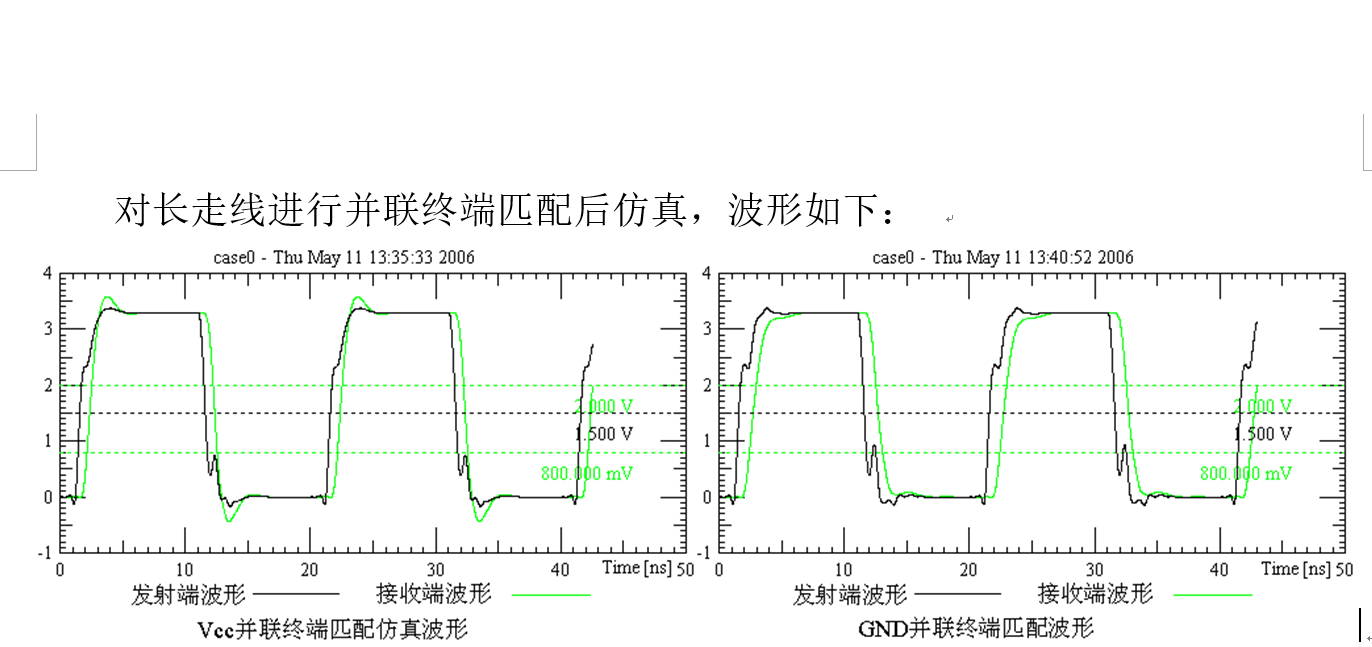

并联终端匹配是最简单的终端匹配技术:通过一个电阻R将传输线的末端接到地或者接到VCC上。电阻R的值必须同传输线的特征阻抗Z0匹配,以消除信号的反射。如果R同传输线的特征阻抗Z0匹配,不论匹配电压的值如何,终端匹配电阻将吸收形成信号反射的能量。终端匹配到VCC可以提高驱动器的源的驱动能力,而终端匹配到地则可以提高电流的吸收能力。

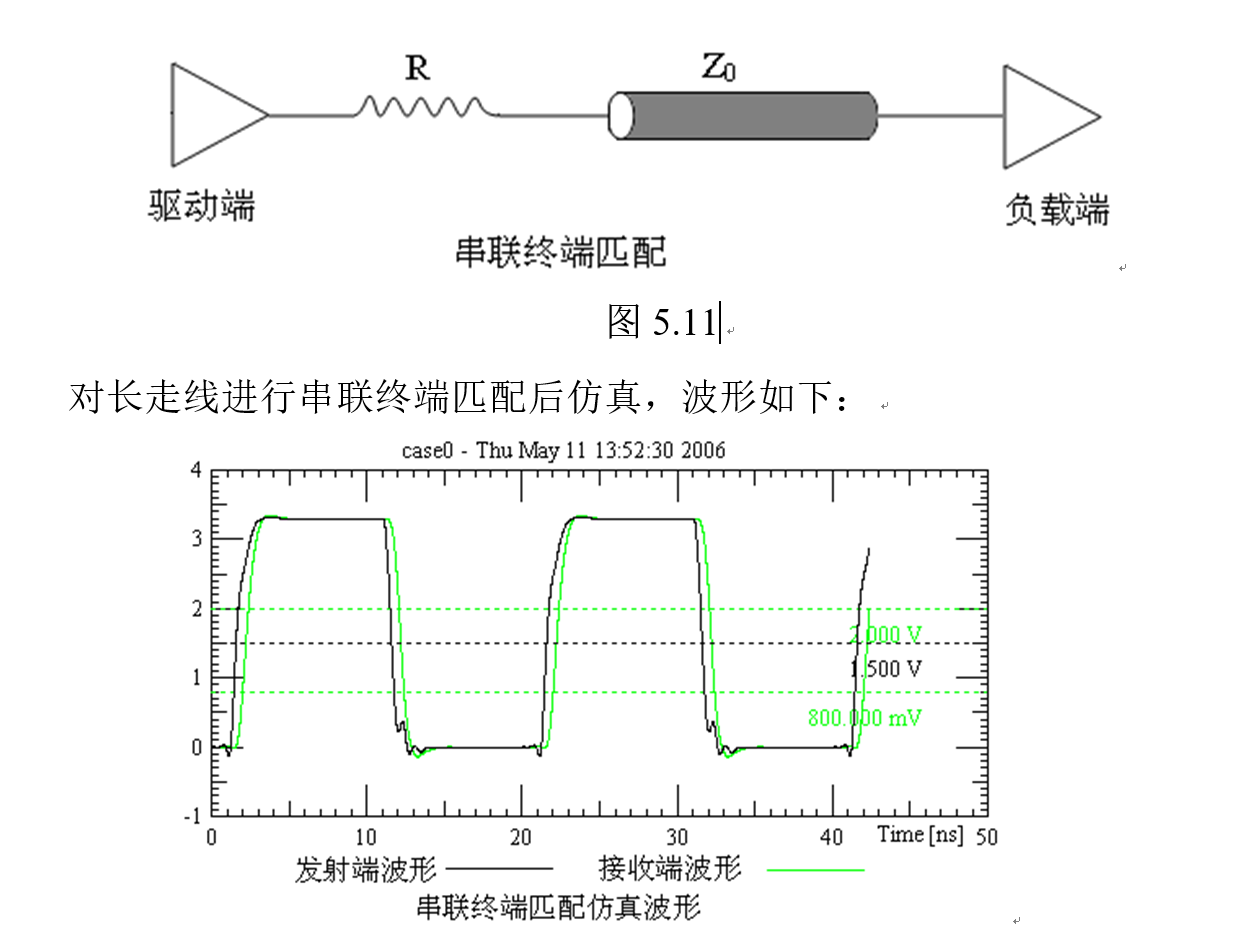

串联终端匹配技术,也称之为后端终端匹配技术,不同于其它类型的终端匹配技术,是源端的终端匹配技术。串联终端匹配技术是在驱动器输出端和信号线之间串联一个电阻。驱动器输出阻抗R0以及电阻R值的和必须同信号线的特征阻抗Z0匹配。对于这种类型的终端匹配技术,由于信号会在传输线、串联匹配电阻以及驱动器的阻抗之间实现信号电压的分配,因而加在信号线上的电压实际只有一半的信号电压。

戴维南终端匹配技术或者也叫做双电阻终端匹配技术,采用两个电阻来实现终端匹配,R1和R2的并联组合要求同信号线的特征阻抗Z0匹配。R1的作用是帮助驱动器更加容易地到达逻辑高状态,这通过从VCC向负载注入电流来实现。与此相类似,R2的作用是帮助驱动器更加容易地到达逻辑低状态,这通过R2向地释放电流来实现。

物理约束规则介绍

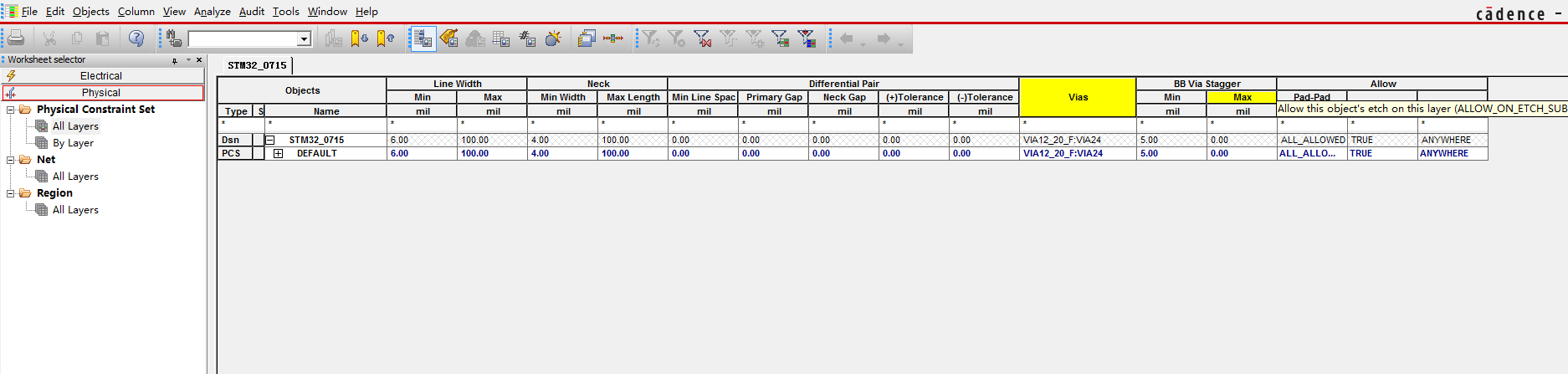

物理规则包括设置线宽和指定过孔库等的属性规则,在设置规则之前,需要把层叠等参数设置好。默认的为default规则。Default规则是指铺铜的单线50Ω阻抗的信号线规则,通常需要设置以下参数。(1)Line width:线宽根据阻抗计算结构进行设置,Min问默认线宽,Max为允许的最大线宽,默认为0表示不限制最大线宽,通常Min的数值不小于4mil。

一直有个疑惑:电容感抗是1/jwC,大电容C大,高频时 w也大,阻抗应该很小,不是更适合滤除高频信号?然而事实却是:大电容滤除低频信号。

电路磁珠的滤波机理

磁珠的外形与电感相似,其主要功能是吸收电源、信号上的噪声等干扰。请注意到“吸收”俩个字。电容本身就可以起到滤波作用,电感和电容配合也能起到滤波作用,但这种滤波,并没有真正的将噪声消除。例如,电容的滤波其原理是在高频时建立一条通往地平面的低阻抗通道,以便将噪声泄放到地平面。而电感和电容配合的滤波,其原理是构建成一个低通滤波器,是让频段比较低的信号顺利而衰减的通过,而阻断频段比较高的噪声,低通滤波器对高频噪声而言,近似一个极大的电阻。高频段噪声遇到这个极大的电阻,只能是被反射回去,基于该原理,应用低

扫码关注

扫码关注