- 全部

- 默认排序

什么是TDR

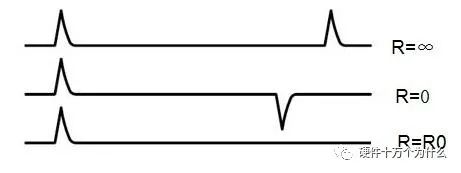

1、TDR时域反射技术原理TDR (Time Domain Reflectometry)时域反射技术的原理是,信号在某一传输路径传输,当传输路径中发生阻抗变化时,一部分信号会被反射,另一部分信号会继续沿传输路径传输。TDR是通过测量反射波的电压幅度,从而计算出阻抗的变化;同时,只要测量出反射点到信号

阻抗,工程师们都接触过,但能把阻抗说清楚的工程师少之又少。阻抗看似简单,实则难以言表。下面我们用快问快答的方式,轻松帮你搞懂阻抗!01 问:什么是阻抗?答:在有电阻、电感和电容的电路里,对交流电所起的阻碍作用叫做阻抗。阻抗常用Z表示。阻抗由

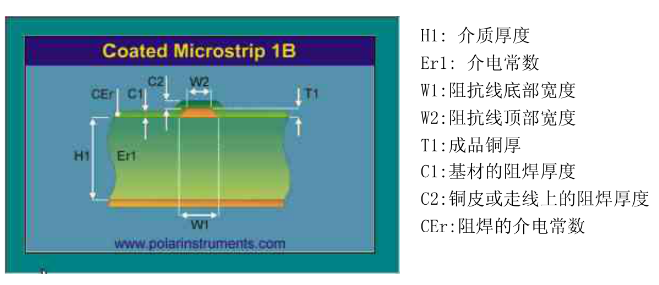

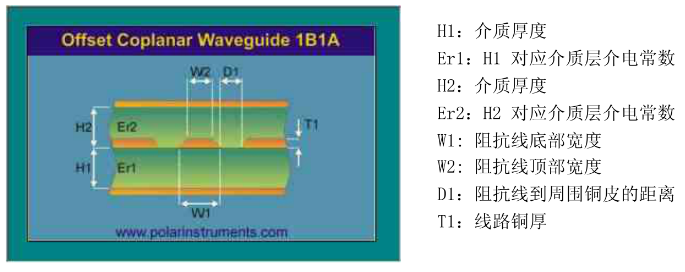

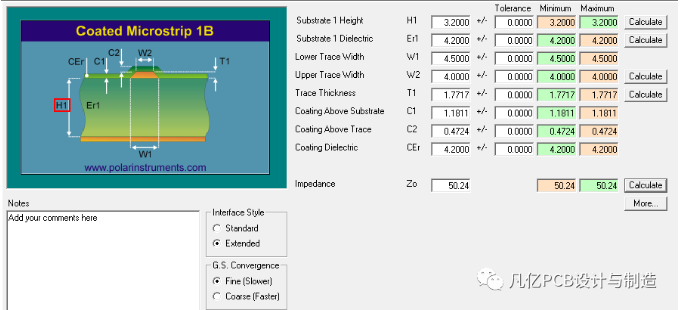

随着信号传输速度的提高,高频电路应用广泛,对PCB板提出了更高的需求,必须让PCB板提供的电路性能保证信号在传输过程中不发生反射现象,信号完整,传输损耗低,起到匹配阻抗的作用,因此,阻抗计算及模型知识点必须掌握!下面将列出大部分的阻抗计算模

PCB设计,细节要牢记,技巧规范,别忘记。元件选择,要慎重权衡,性能优化,细节考虑。电路布局,尺寸精确,差分信号,清晰准确。地平面铺,阻抗匹配,多层堆叠,功耗降低。信号路径,长度平等,串扰减小,信噪比增。参考设计,莫忽略,静电防护,接地要密

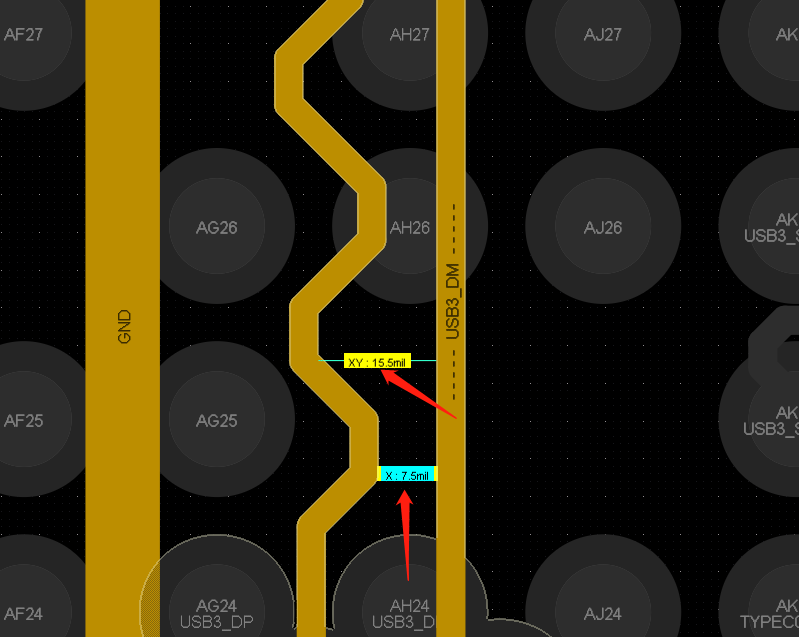

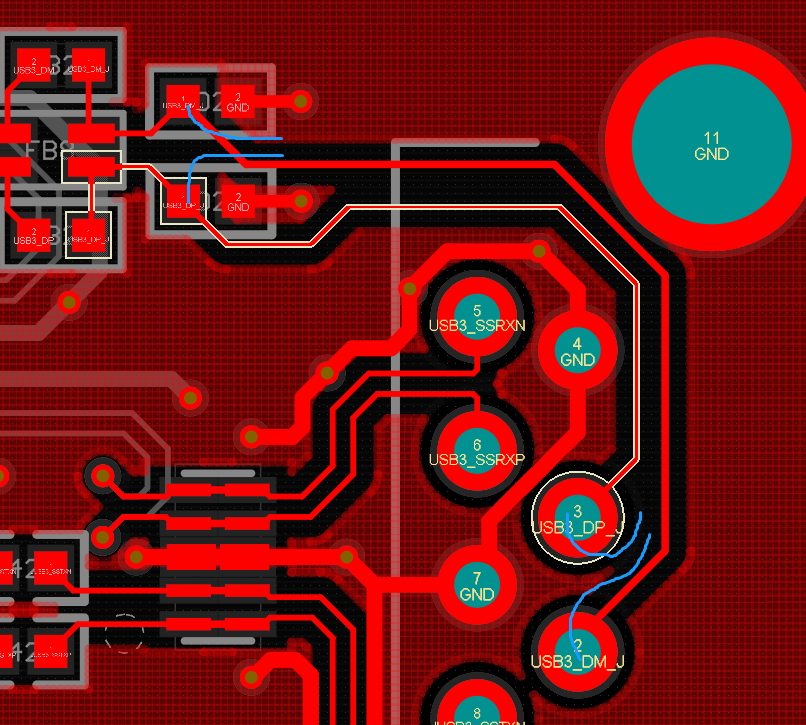

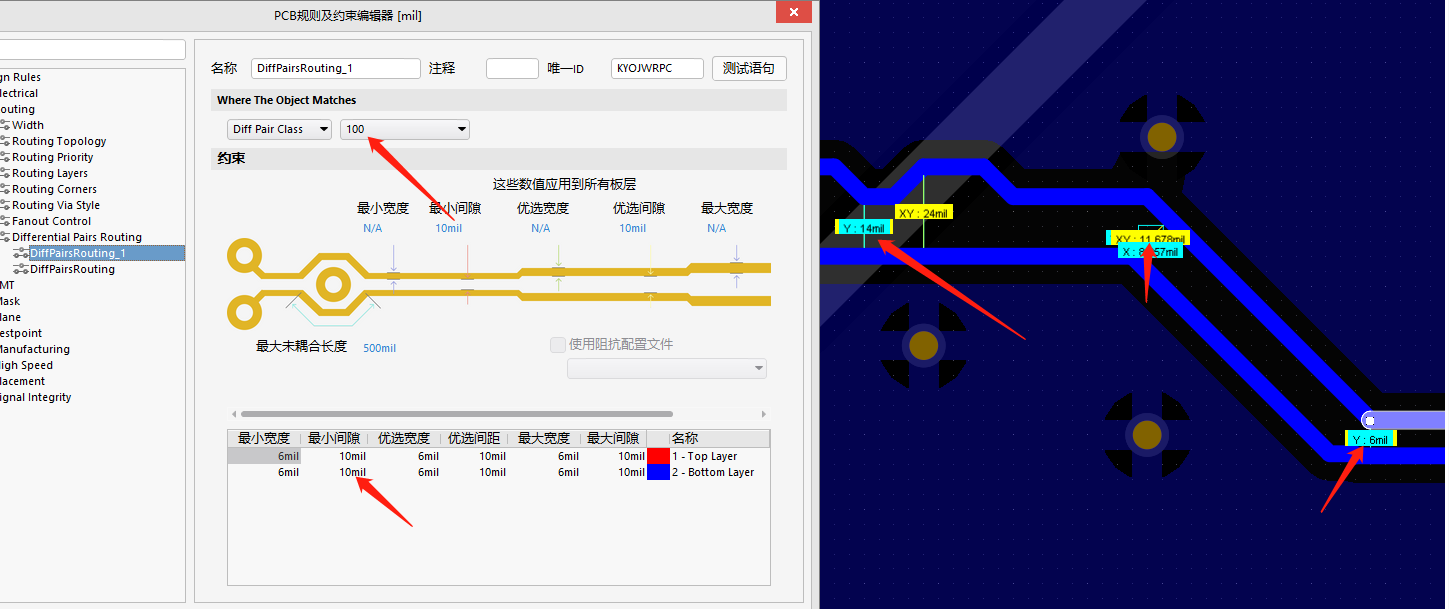

差分对内等长凸起高度不能超过线距的两倍2.焊盘出线可以在优化一下3.差分走线需要按照阻抗线宽线距进行走线4.pcb上不要存在stub线5.注意差分对内等长误差5mil6.存在多处开路,后期自己检查一下drc7.过孔到焊盘间距太近,间距最少6

由于文章篇幅限制,将此文分为上中下,欲看上下篇可点击右侧链接《不能错过!阻抗计算模型超全必看!(上)》。7、内层单端阻抗共面计算模型适用范围:内层单端共面阻抗计算。8、内层差分阻抗共面计算模型适用范围:内层差分共面阻抗计算。9、嵌入式单端阻

PCB是现代电子设备的核心组成部分,其设计和制造对设备性能和可靠性至关重要。在 PCB 设计中,阻抗控制和叠层设计是关键因素之一。本文将深入研究 PCB 的阻抗知识,并探讨八层板与“假八层板”之间的区别,分析它们各自的优劣势。1. PCB阻

注意差分出线要尽量耦合,走一起2.注意差分走线需要按照阻抗线宽线距走线,否则容易产生阻抗突变3.打孔要打在ESD器件前面4.走线一层连通不用打孔差分需要进行对内等长,误差5mil差分对内等长凸起高度不能超过线距的两倍注意器件摆放不要干涉一脚

在电子元件中,金属-氧化物半导体场效应晶体管(MOS管)是独特且重要,然而相比其他元件,MOS管很容易失效,导致电路无法正常运行,因此工程师必须查找原因并解决问题。1、MOS管为什么很容易失效?①静电放电(ESD)MOS管的输入阻抗极高,使

差分走线不符合规范,要按照差分阻抗线宽线距进行走线2.对内等长凸起高度不能超过线距的两倍3.差分走线需要在优化一下4.此处存在短路5.存在多处开路6.一层连通不用打孔,差分要按照阻抗线距走线7.时钟信号尽量单根包地处理8.差分对内等长误差5

扫码关注

扫码关注