- 全部

- 默认排序

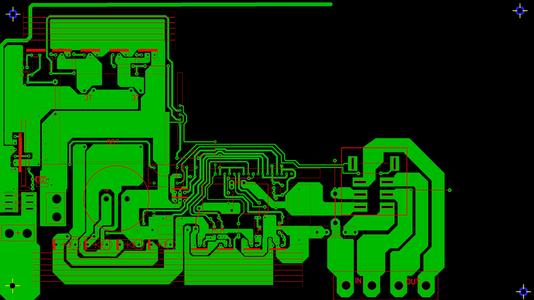

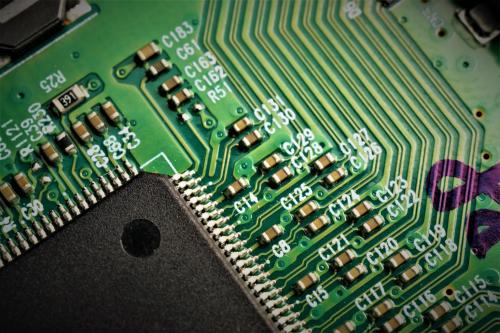

在学习电路设计软件过程中,总会遇到诸多电路设计软件相关难题。为帮助大家解决常见的电路设计软件问题,小编特地带来本文。请注意,本文有关电路设计软件的问题讲解基于protel。如果你想在电路设计软件的学习道路上再进一步,不妨来了解下这些问题哦。 1.原理图常见错误: (1)ERC报告管脚没有接入信号:a.创建封装时给管脚定义了I/O属性;b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;c.创建元件时pin方向反向,必须非pin name端连线。 (2)元件跑到图纸界外:没有在

模拟电路设计一些问题总结

在反馈环外不要使用主动电路进行滤波或控制 EMC 的 RF 带宽,而只能使用被动元件(最好为 RC 电路)。仅仅在运放的开环增益比闭环增益大的频率下,积分反馈方法才有效。在更高的频率下,积分电路不能控制频率响应。 为了获得一个稳定的线性电路设计,所有连接必须使用被动滤波器或其他抑制方法(如光电隔离)进行保护。使用 EMC 滤波器,并且与 IC 相关的滤波器都应该和本地的 0V 参考平面连接

PCB电路设计合作

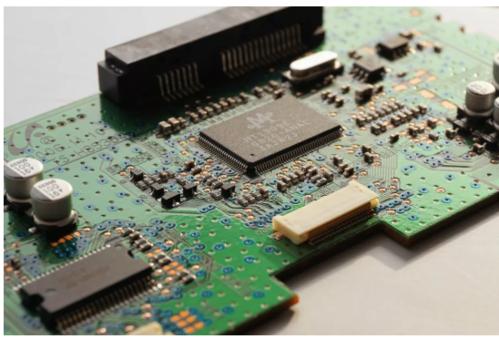

我们知道一旦电路设计完成,它就会被交给“PCB设计师”,然后他们制作了电路板布局。现在,像平板电脑,智能手机甚至电子游戏一样复杂的产品,没有一个人与PCB有关。产品由专家团队设计,如果没有有效的协作,就会浪费时间和出现错误。 这个过程变得越来越复杂,因为团队经常不在同一个地方,所以团队之间协调,记录和分享的软件工具是平稳工作流程的关键。 Momoko带你探讨了评估具有强大协作功能的PCB工具时经常会遇到的几个问题: 在没有强大的协同PCB设计工具的情况下,在PCB设计环境中工作是否有缺点?

对于设计师来说,我们在设计的过程中不能只考虑设计出来的精度以及完美要求,还有很大一个制约条件就是生产工艺的问题。很可能设计出来的产品是“林志玲”生产的就是“罗玉凤”了,板厂不是美帝,不可能为了一个优秀的产品的诞生,重新打造一条生产线。

设计高速电路板的注意事项 怎样引起实际阻抗发生变化的,以及怎样用精确的现场解决工具(field solver)来预见这种现象。即使没有工艺的变化,其它因素也会引起实际阻抗很大的不同。在设计高速电路板时,自动化设计工具有时不能发现这种不很明显但却非常重要的问题。然而,只要在电路设计的早期步骤当中采取一些措施就可以避免这种问题。我把这种技术称做“防卫设计”(defensive design)。

1.Altium Designer将需要做等长的线组成一个类:在Design-Classes中,右键Net Classes弹出菜单中,选择Add Class,为新New Class命名(Rename Class),加入需要的Net。

根据欧姆定律,当被测电流流过电阻时,电阻两端的电压与电流成正比.当1W的电阻通过的电流为几百毫安时,这种设计是没有问题的.然而如果电流达到10-20A,情况就完全不同,因为在电阻上损耗的功率(P=I2xR)就不容忽视了.我们可以通过降低电阻阻值来降低功率损耗,但电阻两端的电压也会相应降低,所以基于取样分辨率的考虑,电阻的阻值也不允许太低.

上海pcb培训多层板布线设计这是个涉及面大的问题。我们抛开其它因素,仅仅就PCB设计环节来说,分享以下几点心得,供参考交流: 1.上海pcb培训多层板合理布置电源滤波/退耦电容:一般在原理图中仅画出若干电源滤波/退耦电容,但未指出它们各自应接于何处。其实这些电容是为开关器件(门电路)或其它需要滤波/退耦的部件而设置的,布置这些电容就应尽量靠近这些元部件,离得太远就没有作用了。有趣的是,当电源滤波/退耦电容布置的合理时,接地点的问题就显得不那么明显。

扫码关注

扫码关注