- 全部

- 默认排序

一、单片机电路设计上拉电阻的选择大家可以看到电路设计中复位电路中电阻R1=10k时RST是高电平 ,而当R1=50时RST为低电平,很明显R1=10k时是错误的,单片机一直处在复位状态时根本无法工作。出现这样的原因是由于RST引脚内含三极管,即便在截止状态时也会有少量截止电流,当R取的非常大时,微弱的截止电流通过就产生了高电平。二、LED串联电阻的计算问题

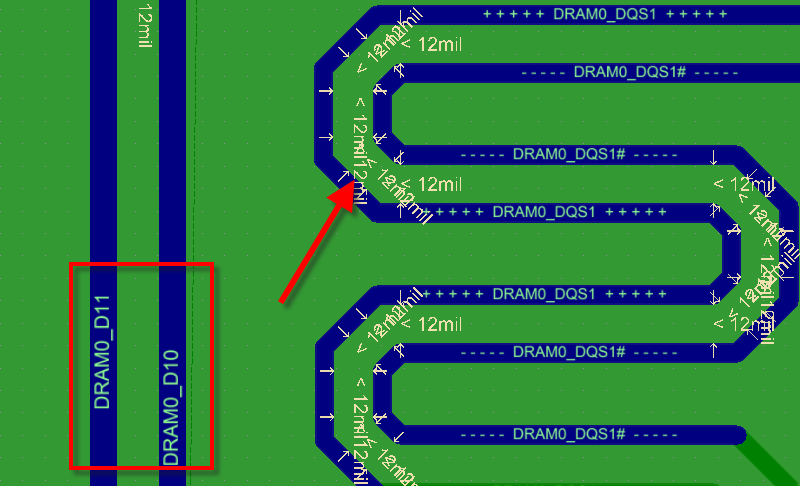

为了尽量减小单板设计的串扰问题,PCB设计完成之后一般要对线间距3W规则进行一次规则检查。一般的处理方法是直接设置线与线的间距规则,但是这种方法的一个弊端是差分线间距(间距设置大小不满足3W规则的设置)也会DRC报错,产生很多DRC报告,难以分辨

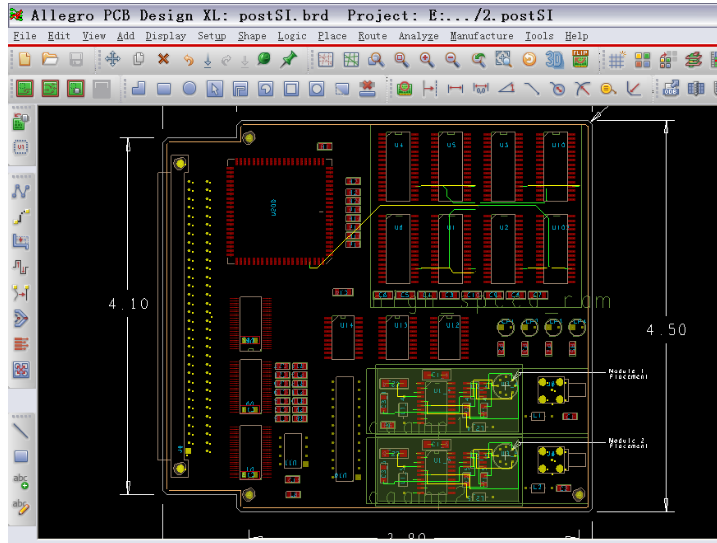

高速高密度多层PCB板的SI/EMC(信号完整性/电磁兼容)问题长久以来一直是设计者所面对的最大挑战。然而,随着主流的MCU、DSP和处理器大多工作在100MHz以上(有些甚至工作于GHz级以上),以及越来越多的高速I/O埠和RF前端也都工作在GHz级以上,再加上应用系统的小型化趋势导致的PCB空间缩小问题,使得目前的高速高密度PCB板设计已经变得越来越普遍。许多产业分析师指出,在进入21世纪以后,80%以上的多层PCB设计都将会针对高速电路。

嵌入式设计是个巨大的工程项目,今日便说说硬件电路设计层面的几个常见问题,最先,我们掌握下嵌入式的硬件架构。我们知道,CPU是这一系统软件的生命,全部的外场配备都两者之间关联,这也突显了嵌入式设计的一个特性硬件可裁剪。在做嵌入式硬件设计中,以下内容必须关心。 第一、开关电源明确

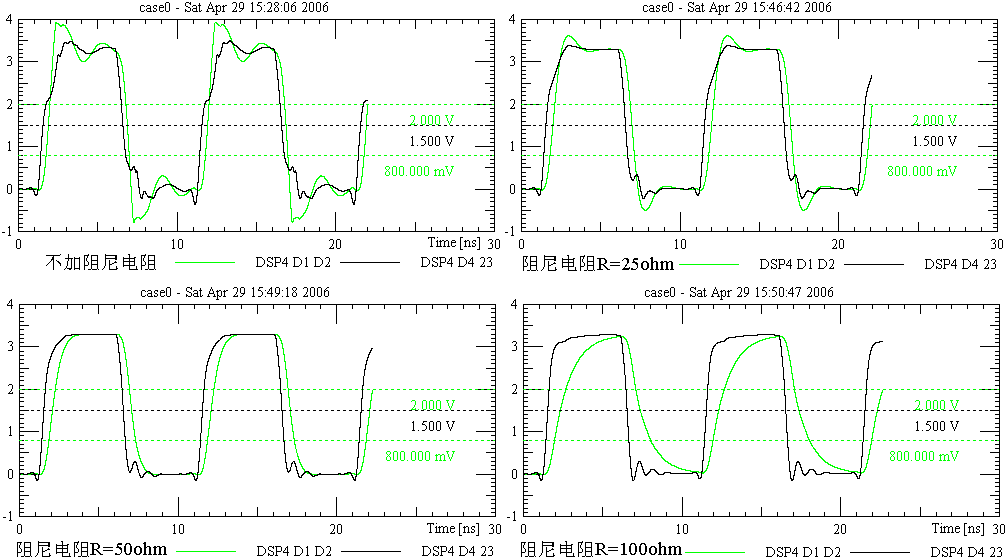

信号完整性是指信号在信号线上的质量。信号具有良好的信号完整性是指当在需要的时候,具有所必需达到的电压电平数值。差的信号完整性不是由某一因素导致的,而是由板级设计中多种因素共同引起的。特别是在高速电路中,所使用的芯片的切换速度过快、端接元件布设不合理、电路的互联不合理等都会引起信号的完整性问题。具体主要包括串扰、反射、过冲与下冲、振荡、信号延迟等。

在研究由反射引起的振铃效应前,先讨论由电路谐振引起的振铃效应。在时钟速度高达10MHz的数字系统中,振铃(Ringing)现象是设计中的显著问题。传导系统对输入信号的响应,在很大程度上取决于系统的尺寸是否小于信号中最快的电气特性的有效长度,反之亦然。电气特性的有效长度由它的持续时间和传播延迟决定,即l=Tr/D(Tr =上升时间,ps;D=延迟,ps/in)。如果走线长度小于有效长度的1/6,该电路表现为集总系统,如果系统对输入脉冲的响应是沿走线分布的,称之为分布系统。

数字电路的调试

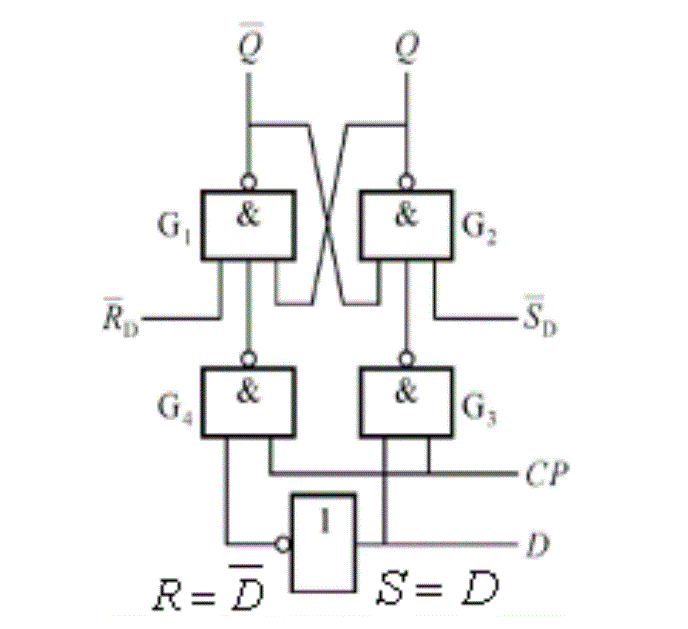

数字电路除了能够满足其时序要求外,需要更多关注的是数字电路对一些关键参数的满足,特别是对于边沿敏感的器件,满足不了其上升时间的要求,则芯片工作将会出现异常。调试的过程中发现一款D触发器构成的一键开关机电路存在问题

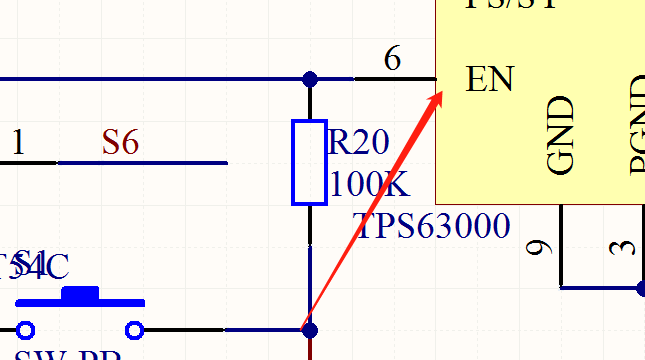

电源设计调试及故障排查

(1)对于采用电池供电的手持设备,系统的电源芯片一般采用效率较高、电压转换灵活的DC-DC(直流-直流)开关电源IC来实现,但是DC-DC开关电源的IC往往存在调试麻烦的问题,这些问题的可以归结为以下几类:1)输出电压基本为0;2)输出电压基本等于输入电压;3)输出电压与设计中预设值偏离较大,这个针对输出可调的DC-DC芯片而言的;4)输出电压正常,但是片子(含除电源外的其他IC)发热严重。输出电压基本为0的时候,首先要检查该电源IC使能脚是否接对是不是高电平,可以用万用表测一下该引脚的电压,若

扫码关注

扫码关注