- 全部

- 默认排序

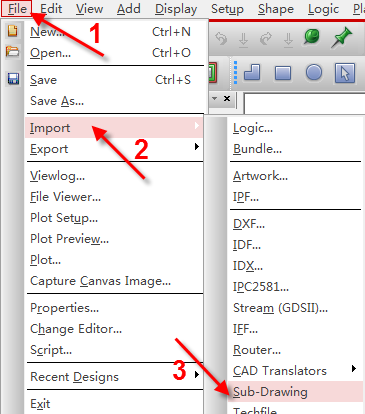

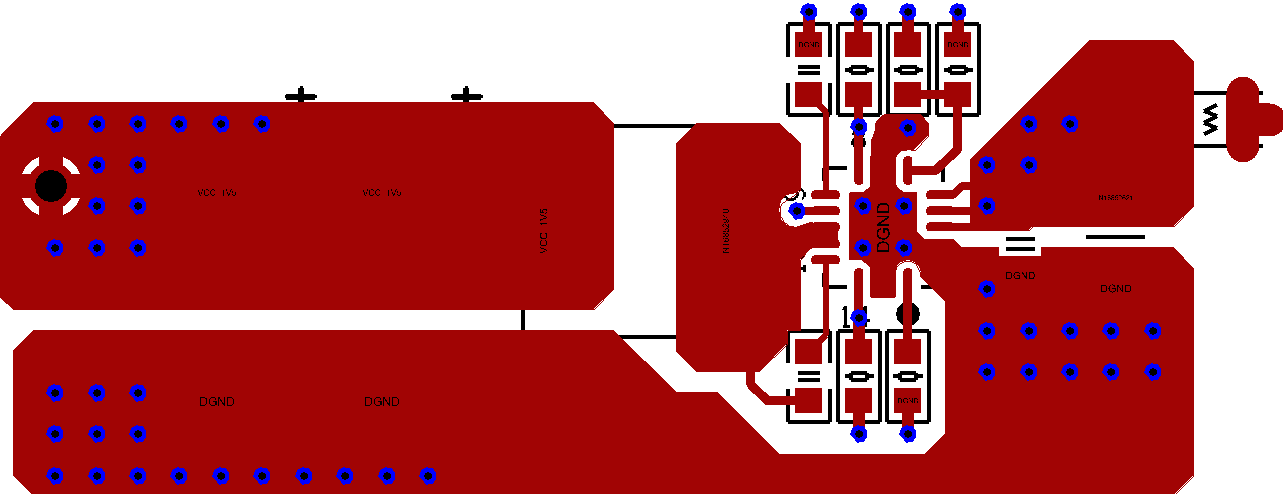

答:在前面的问答中我们讲解了Team Design功能的详细使用方法,除了这种方法可以进行协同设计以外,这样是最高效的方法,Sub-drawing功能也是可以的,简单的说,Sub-drawing就是从别的PCB文件拷贝器件或者走线到当前的PCB文件中,而copy命令也是复制功能,但是只能应用于同一个PCB文件中,这个是二者最大的区别,以下我们讲解一下,Sub-drawing功能的具体的应用方法,操作如下:

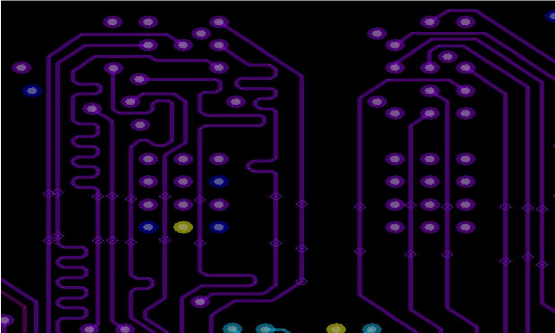

答:在前面的几个问答当中,我们都有提到,对一些做好的模块进行创建Groups组的操作,方便我们进行模块复用、布局操作。我们创建了Groups组之后呢,这个属性会一直存在,我们是否可以将这个属性给去除掉,方便后期的布线操作与规划。因为添加了这个Groups组的属性以后,从这个模块走出的线会出现下面的小方块的现象,如图6-22所示,虽然不影响整体的性能,但是影响美观,所以呢,这里我们会讲解一下如何将已经创建好的Groups组进行打散的操作,具体操作如下:

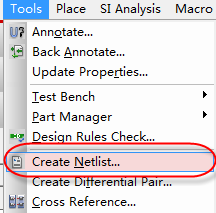

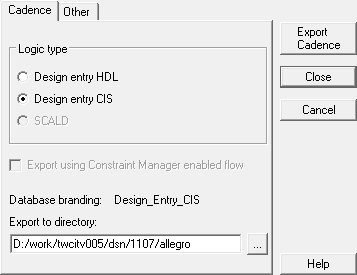

答:在前面的问答中,我们已经清晰的讲解了如何利用Orcad软件输出第一方网表,然后导入到Allegro软件中,这一问呢,我们讲述一下如何利用Orcad软件输出第三方网表文件,并将其导入到Allegro软件中,具体的操作如下:

答:在前面的问答中,我们分别详细讲述了第一方网表与第三方网表的输出方法与导入方法,这两种导入方法有什么区别与联系呢,是不是都可以呢?这里呢,我们讲解一下第一方网表与第三方网表的区别与联系,具体如下:

答:在上述的问答中,我们对所有的区域的含义进行了详细的描述,下面我们讲述下在PCB设计中对一些常用的布局布线区域进行设置,首先在绘制好板框的情况下,我们以Route Keepin为例,然后运用z-copy命令进行设置,具体的操作如下:

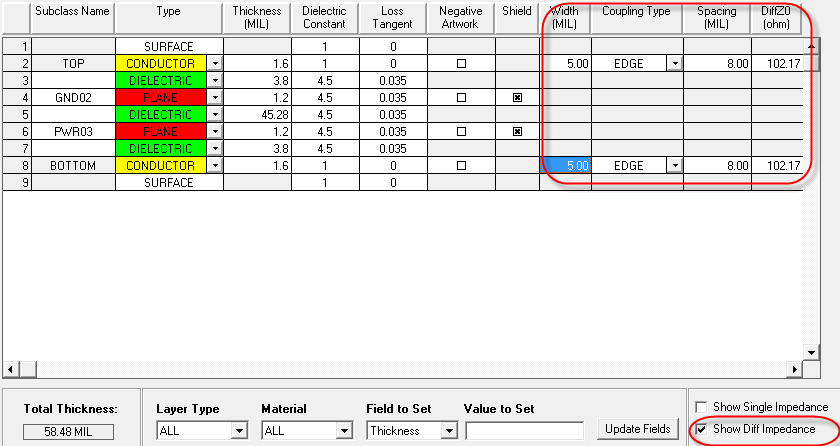

答:在上述的问答中,我们详细讲述了多层板应该如何进行层叠设置,并没有涉及对整个PCB板的阻抗设计,这一问呢,我们就介绍一下如何在Allegro软件中,输入参数,简单的对阻抗线宽做一个大概的估算,具体操作如下:

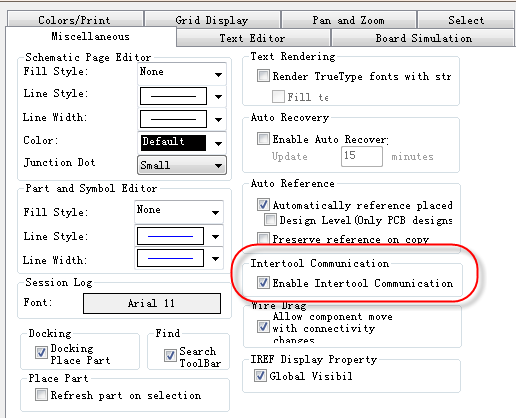

答:在前面的问答中,我们讲解了如何在PCB中对元器件编号进行重排,重新排列之后呢,PCB中是进行更改了,我们还需要将重新排列之后的元器件的编号反标回到原理图中,这样原理图文件跟PCB文件才是同步的,具体操作的步骤如下所示:

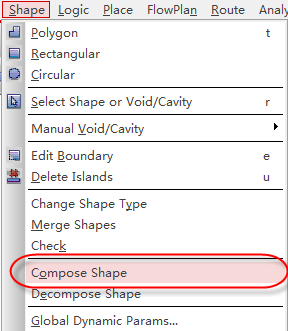

答:在Allegro软件中,所铺的铜皮全部都是动态铜皮,在进行Etch显示的时候,包括走线、铜皮都会显示,在前面的问答中我们讲解了如何将铜皮全隐藏不显示,但是,这样不方便走线设计,走线时不清楚哪一块有铜皮,这里我们讲解一下,如何设置铜皮不显示,但是在PCB中还是显示铜皮的边框,具体操作如下所示:

4月26日华为2022分析师大会在深圳开幕,华为轮值董事长胡厚崑、常务董事汪涛等参与了现场问答,与媒体、分析师等交流。其中胡厚崑表示,今年华为会有新的智能汽车发布,无论是智选模式还是HI模式(Huawei Inside)的车型。如何参与鸿蒙

EMC工程问题解答(六)

一问:为什么垂直缝隙,水平辐射大,是什么原理?答:这个与天线的方向性有关。具体可以参考下面相关缝隙天线的资料。缝隙天线就是在波导面上开有缝隙,以用来辐射或接收电磁波的天线。在研究实际的缝隙天线之前,先讨论在无限大和无限薄的理想导电平板上的缝隙——理想缝隙天线。理想缝隙天线的横向尺寸远小于波长,纵向尺

扫码关注

扫码关注