- 全部

- 默认排序

系统级信号完整性(SI)仿真是高速PCB设计的重要概念,其存在间接联系着高速PCB电路设计的正常运行,但有很多小白不清楚,甚至错将系统级SI仿真和普通的SI混为一谈,这是错误的思维误区,我们要尽量避免。一般来说,现在的EDA信号完整性根据主

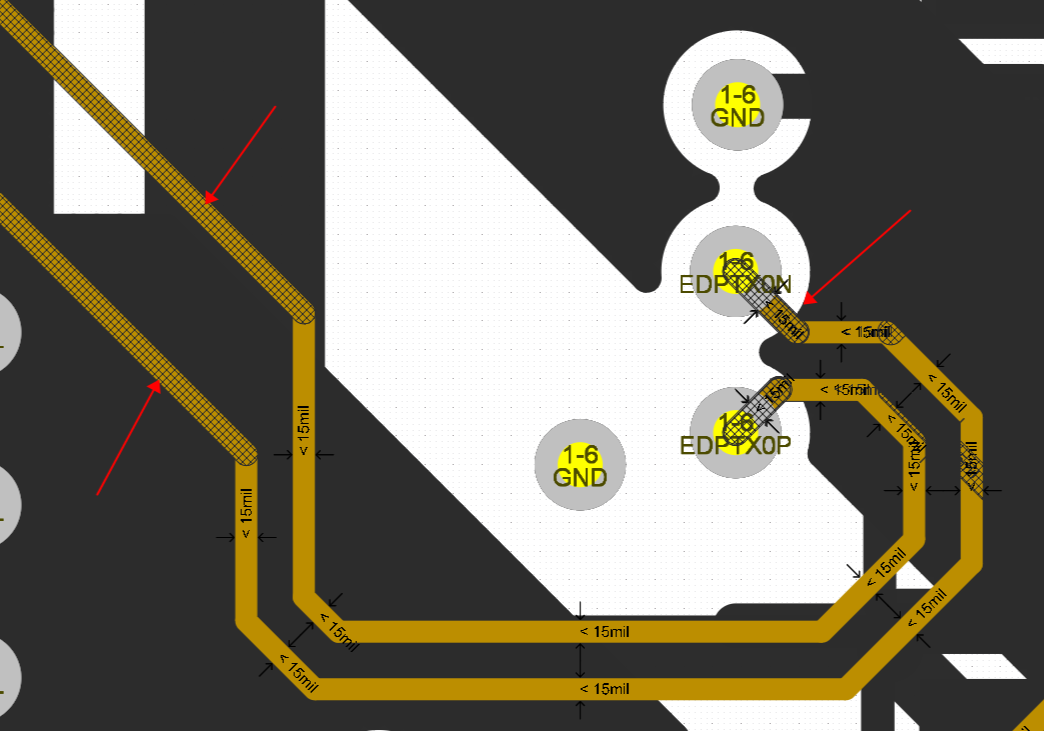

Altium Designer走差分线出现网格是什么原因?答:如图1所示,在AD软件中走差分线出现网格主要是差分线的未耦合长度没有满足差分规则所导致的,未耦合长度指的是差分线中不满足差分间距的长度。图 1 差分走线出现网格走线当出现这种错误

Cadence Allegro单个元器件的PCB封装更新操作在PCB设计中如何对同一种类型的元器件进行封装的更新,有时候会出现这样的情况,出现错误的操作,误删除的其中一个器件的丝印或者是什么的,能否只更新这一个器件呢,其它的不进行更新,当然

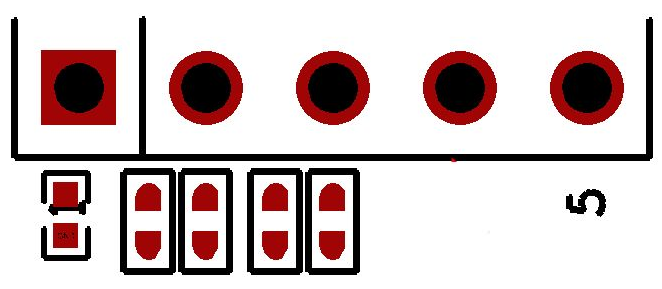

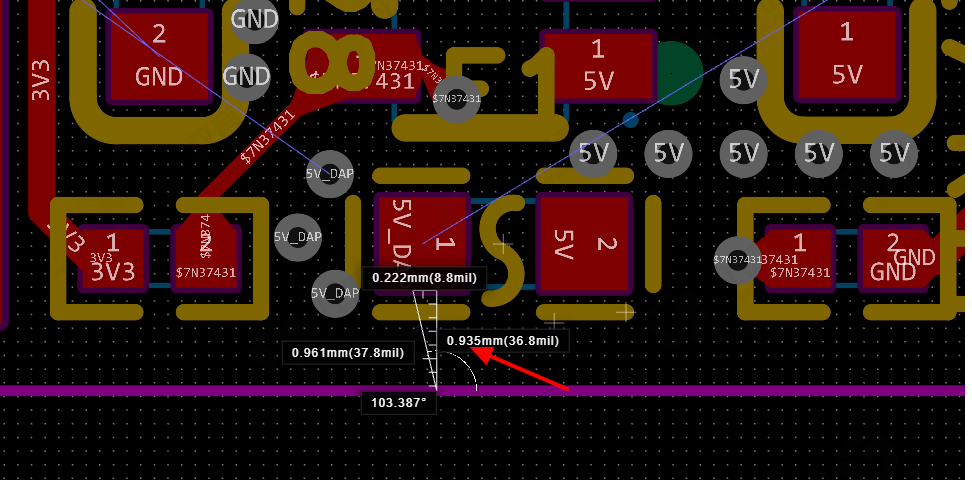

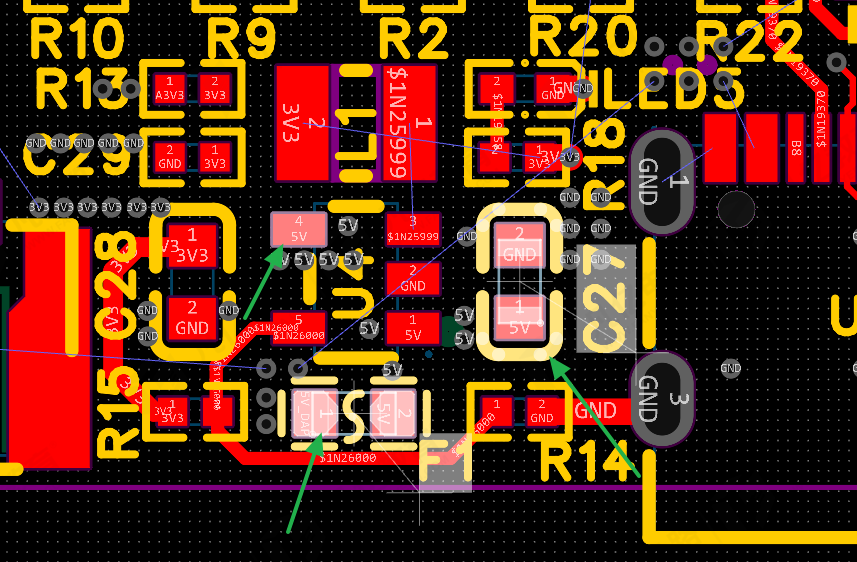

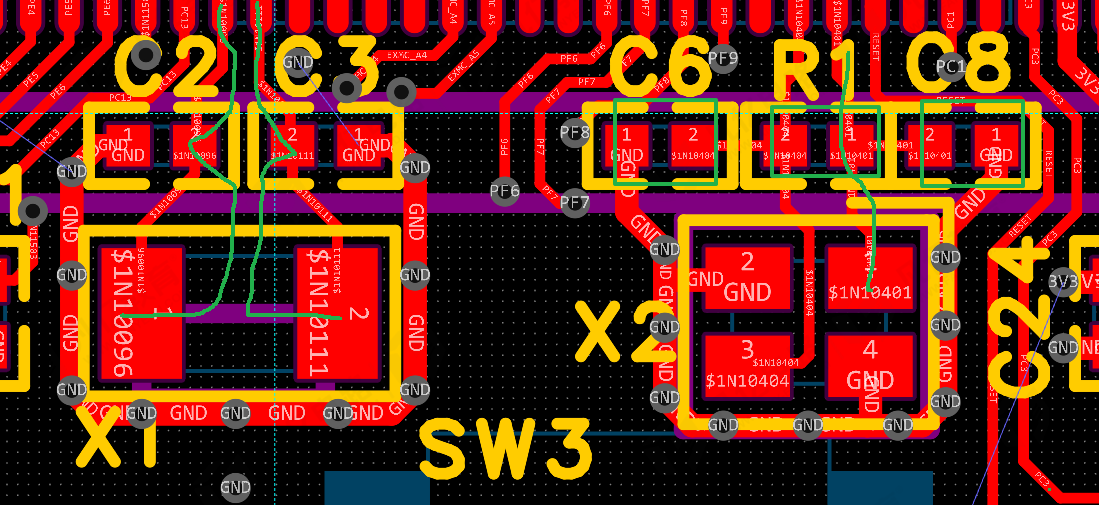

梁山派pcb设计特训营作业评审要求器件离板边5mm不要布局器件,除非特殊要求或后续板子设计可以添加工艺边。 【问题改善建议】:在贴片时留给设备的传送带固定用,建议无特殊要求板边5mm不要布局器件。2.晶振布局、布线错误。 【问题改善

电源输入电容应该靠近管脚放置输出电容电阻应该靠近管脚放置到电感后面输出3.3v晶振布局错误,晶振的一对线要走成类差分的形式, 线尽量短如下图。typec的LCD_R4、LCD_R5要走差分阻抗控制90欧姆做对内等长,差分走线尽量减少打孔换层

晶振布局、布线错误,晶振的一对线要走成类差分的形式, 线尽量短如下图。typec的LCD_R4、LCD_R5要建立差分对走差分阻抗控制90欧姆做对内等长,换层需要靠近过孔打回流地过孔,D7、D8应该尽量靠近typec管脚放置。TF卡所有信号

电源模块反馈电路错误,r15接入反馈电源到r14在到5号管脚。2.晶振布局布线错误3.typec差分对内误差控制5mil以内,尽量避免出现不耦合4.TF卡所有信号线要整组 ,做等长处理以时钟线为目标,目标控制在300mil以内。

DSP芯片已成为大多数电子工程师的常用数字芯片之一,今天我们来了解下DSP芯片的多通道缓冲串口McBSP,探索其异常错误和发生原因。一般来说,每个多通道缓冲串口McBSP有以下五个事件会导致错误发生:①接受过速,由标志RFULL=1表示;②

之前我们新出了《管理员如何处理计算机网络的突发故障》系列之上篇,得到了很多人的喜爱,反响良好,今天我们将更新下篇,希望能帮助到更多小伙伴们。4、缩小搜索范围对所有列出的可能导致错误的原因逐一进行测试,且不要根据一次测试就断定某一区域的网络是

一起学习一、什么是Gerber 文件?Gerber 文件是电路设计过程的输出,包含电路板制造商使用的各类细节,Gerber 文件用来 PCB 制造和组装过程。Gerber 文件包括 PCB 层的物理属性、 PCB 图层等,根据这些信息用来 PCB 板的制造,例如:蚀刻、PCB板的大小尺寸、焊盘等。分

扫码关注

扫码关注