- 全部

- 默认排序

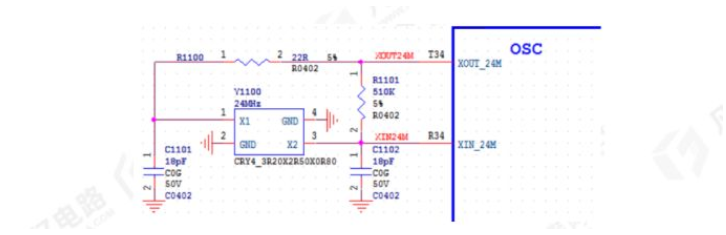

时钟电路就是类似像时钟一样准确运动的震荡电路,任何工作都是依照时间顺序,那么产生这个时间的电路就是时钟电路,时钟电路一般是由晶体振荡器、晶振、控制芯片以及匹配电容组成,如图1所示。图1 时钟电路针对时钟电路PCB设计有以下注意事项:1、晶体

时钟电路就是类似像时钟一样准确运动的震荡电路,任何工作都是依照时间顺序,那么产生这个时间的电路就是时钟电路,时钟电路一般是由晶体振荡器、晶振、控制芯片以及匹配电容组成,如图1所示。图1 时钟电路针对时钟电路PCB设计有以下注意事项:1、晶体

有兴趣了解智能电网的工作原理吗?别再犹豫了!我们为您提供了一些常见问题及其答案。继续阅读,了解智能电网技术的细节。1.智能电网如何节能?智能电网通过将数字技术融入配电系统来优化能源消耗。与传统电网不同,智能电网使用先进的传感器、仪表和通信网

晶振可以说是集成电路的核心元件,一直以来是很多电子工程师在PCB Layout设计时的焦点所在,为了保证系统的优势最大化,晶振的Layout设计更是不能出错,本文将谈谈贴片晶振的Layout设计该如何做?1、匹配电容的摆放位置尽量靠近晶振;

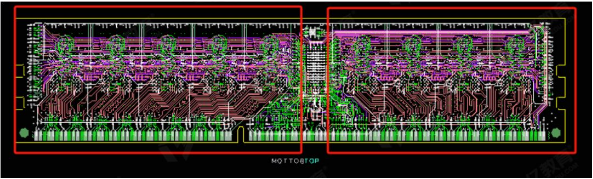

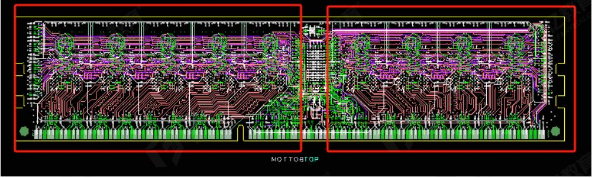

DDR采用菊花链拓扑结构时,由于信号传输线较长通常需要在DDR末端加上终端匹配电阻,端接的方式有很多,但是都是为了解决信号的反射问题,通常为了消除信号的反射可以在信号的源端或者终端进行解决,在源端处消除反射是采用电阻串联的方式,在终端处消除

上次我们对不加端接电阻和加端接电阻之后的仿真结果做了分析之后我们得出在DDR采用菊花链拓扑结构的时候是需要加端接电阻的,这次我们看看DDR末端的端接电阻距离最后一片DDR远一点效果好一些还是近一点效果好一些。本次采用的案例依旧是我们上期的D

CAN(Controller Area Network)是一种用于实时应用的串行通讯协议总线,它可以使用双绞线来传输信号,是世界上应用最广泛的现场总线之一。CAN协议用于汽车中各种不同元件之间的通信,以此取代昂贵而笨重的配电线束。在CAN总线应用中,一般建议使用屏蔽双绞线进行组网、布线,本文将详细讲

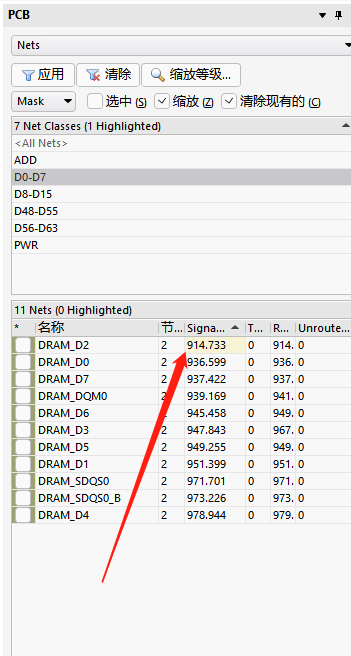

等长存在误差报错2.注意地址线之间等长也需要满足3W规则3.尺寸走线需要优化一下,尽量不要走直角4.地址线等长存在误差报错后期自己调整一下时钟差分信号中高端匹配电阻应该靠近T点放置等长可以在优化一下,满足3W的前提尽量紧凑一些,提高空间利用

配电变压器是电力系统中的重要组成部分,用于将高压输电线路输入的电能变换为适用于用户的低压电能。它是一种静止式变压器,通过电磁感应原理实现电能的变换。配电变压器广泛应用于工业、农业、商业和居民用电等各个领域。01配电变压器基本结构配电变压器由

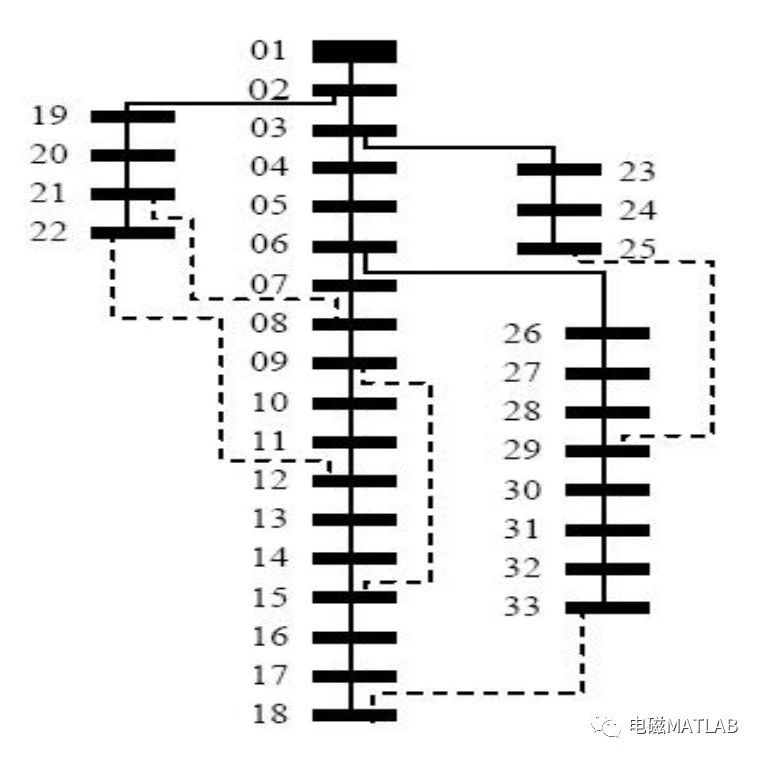

1 前推回代法原理对于如图所示的辐射状配电馈线,k,i分别为父、子节点, i,j分别为父,子节点,Ci为由节点i的子节点构成的节点集.配网潮流前推回代潮流算法第n 1步的迭代公式如下:节点i的前推计算公式为2 算例IEEE33节点结构3 程序运行结果4 matlab程序clcclearclose

扫码关注

扫码关注